# CS 335: Code Generation

#### Swarnendu Biswas

Department of Computer Science and Engineering, Indian Institute of Technology Kanpur

Sem 2023-24-II

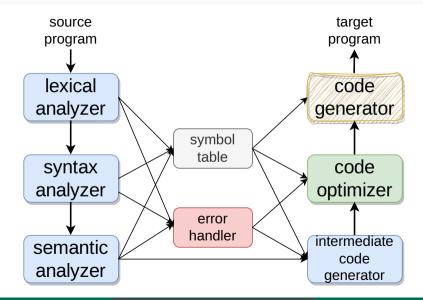

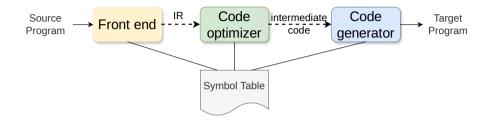

### An Overview of Compilation

Swarnendu Biswas (IIT Kanpur)

### **Code Generation**

- (i) Generated output code must be correct

- (ii) Generated code must be of "good" quality

- ► Notion of good can vary

- ► Should make efficient use of resources on the target machine

- (iii) Code generation should be efficient

Generating optimal code is undecidable, compilers make use of well-designed heuristics

### **Code Generation**

#### Input

- Intermediate representation (IR) generated by the front end

- ► Linear IRs like 3AC or stack machine representations, or graphical IRs

- Symbol table information

#### Assumptions

- Code generation does not bother with error checking

- Code generation assumes that types in the IR can be operated on by target machine instructions

- ► For example, bits, integers, and floats

## **Code Generation**

### Output

#### • Absolute machine code

- ► Generated addresses are fixed and work when loaded at fixed locations in memory

- Efficient to execute, now primarily used in embedded systems

- Relocatable machine code

- Code can be broken down into separate sections and loaded anywhere in memory that meets size requirements

- ► Allows for separate compilation but requires a separate linking and loading phase

- Assembly language

- ► Simplifies code generation, but requires assembling the generated code

### Steps in Code Generation

- Compiler back end performs three steps to translate IR to executable code

Instruction selection Choose appropriate target machine instructions while

generating code

Register allocation Decide what values to keep in which registers

Instruction scheduling Decide in what order to schedule the execution of instructions

- Need to also emit code to manage memory during execution

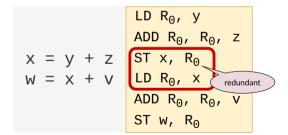

### Instruction Selection

- Possible idea: Match patterns and replace them with a pre-decided template

- (i) Devise a target code skeleton for every 3AC IR instruction

- (ii) Replace every 3AC instruction with the skeleton

$$x = y + z \begin{cases} LD R_0, y \\ ADD R_0, R_0, z \\ ST x, R_0 \end{cases}$$

### Instruction Selection

• Each IR instruction can be translated in several ways, the **challenge** is to pick an **efficient** variant

$$a = a + 1 \begin{cases} LD R_0, a \\ ADD R_0, R_0, \#1 \\ ST a, R_0 \end{cases}$$

INC a

- Need a cost model and heuristics for instruction selection

- Influential factors are the level of abstraction of the IR, speed of instructions, energy consumption, and space overhead

- Target ISA also influences instruction selection Scalar RISC machine simple mapping from IR to assembly

- CISC machine may need to fuse multiple IR operations for effectively using

**CISC** instructions

Stack machine needs to translate implicit names and destructive instructions to assembly

Swarnendu Biswas (IIT Kanpur)

## **Register Allocation**

Instructions operating on register operands are more efficient

Register allocation Choose which variables will reside in registers Register assignment Choose which registers to assign to each variable

- Architectures may impose restrictions on the usage of registers

- Finding an optimal assignment of registers to variables is NP-complete

Architectures such as IBM 370 may require register pairs to be used for some instructions

| MUL x, y | <ul> <li>x is in the even register, y is<br/>in the odd register</li> <li>Product occupies the<br/>entire even/odd register pair</li> </ul>   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| DIV x, y | <ul> <li>64-bit dividend occupies the even/odd register pair</li> <li>Even register holds the remainder, odd register the quotient</li> </ul> |

### Instruction Scheduling

- Order of evaluating the instructions also affects the efficiency of the target code

- Instruction scheduling reorders instructions to maximize utilization of hardware resources and minimize cycles

- Selecting the best order across inputs is an NP-complete problem

### Target Machine for Code Generation

• Efficient code generation requires a good understanding of the target ISA

### • Assumptions

- ► Three-address machine, byte-addressable with four-byte words

- ► *n* general-purpose registers

- Limited instruction set

- ▶ OP dst, src<sub>1</sub>, src<sub>2</sub>

- LD dst, addr

- ST dst, src

- BR L

- Bcond r, L

# Specifies how to **interpret the operands** of an instruction

| Mode              | Form  | Address                             | Example                                                     |

|-------------------|-------|-------------------------------------|-------------------------------------------------------------|

| absolute          | М     | М                                   | LD $R_0$ , M                                                |

| register          | R     | contents(R)                         | ADD $R_0$ , $R_1$ , $R_2$                                   |

| indexed           | c(R)  | contents(c + contents(R))           | LD R <sub>1</sub> , 4(R <sub><math>\emptyset</math></sub> ) |

| indirect register | *R    | contents(contents(R))               | LD $R_1$ , $*R_0$                                           |

| indirect indexed  | *c(R) | contents(contents(c + contents(R))) | LD R <sub>1</sub> , *100(R <sub>0</sub> )                   |

| immediate         | #c    | С                                   | LD R <sub>1</sub> , #1                                      |

|                   |       |                                     |                                                             |

### Examples of Code Generation

| x | = y - z  | LD $R_2$ , z | // R <sub>1</sub> = y<br>// R <sub>2</sub> = z<br>// R <sub>1</sub> = R <sub>1</sub> - R <sub>2</sub><br>// x = R <sub>1</sub>                 | if x < y<br>goto L | -                                                                                       | // R <sub>1</sub> = x<br>// R <sub>2</sub> = y<br>// R <sub>1</sub> = R <sub>1</sub> - R <sub>2</sub><br>// if R <sub>1</sub> < 0 JMP M        |

|---|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| k | o = a[i] |              | <pre>// R<sub>1</sub> = i<br/>// R<sub>1</sub> = R<sub>1</sub> * 8<br/>// R<sub>2</sub> = c(a+c(R<sub>1</sub>))<br/>// b = R<sub>2</sub></pre> | a[j] = c           | LD $R_1$ , C<br>LD $R_2$ , j<br>MUL $R_2$ , $R_2$ , 8<br>ST $a(R_2)$ , $R_1$            | <pre>// R<sub>1</sub> = c<br/>// R<sub>2</sub> = j<br/>// R<sub>2</sub> = R<sub>2</sub> * 8<br/>// c(a+c(R<sub>2</sub>)) = R<sub>1</sub></pre> |

|   | x = *p   |              | <pre>// R<sub>1</sub> = p<br/>// R<sub>2</sub> = c(0+c(R<sub>1</sub>))<br/>// x = R<sub>2</sub></pre>                                          | *p = y             | LD R <sub>1</sub> , p<br>LD R <sub>2</sub> , y<br>ST 0(R <sub>1</sub> ), R <sub>2</sub> | <pre>// R<sub>1</sub> = p<br/>// R<sub>2</sub> = y<br/>// c(0+c(R<sub>1</sub>)) = R<sub>2</sub></pre>                                          |

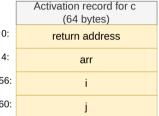

### Runtime Storage Management

Assume that the first location in the activation record (given by staticArea) of the callee stores the return address of the caller

|                   | Static Allocation              |                                                                                                                                         |  |

|-------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | ST callee staticArea, #here+20 | Store return address in the first slot in the<br>callee's activation record, assume 2<br>opcodes and 3 constants are each of 4<br>bytes |  |

|                   | BR callee.codeArea             | Transfer control to callee code                                                                                                         |  |

| return<br>address |                                |                                                                                                                                         |  |

|                       | Callee's code area         |

|-----------------------|----------------------------|

| BR *callee.staticArea | Transfer control to caller |

|                       |                            |

а

### Determine Addresses in Target Code

Need to generate code to manage activation records at runtime

| 3AC                                               |                 |

|---------------------------------------------------|-----------------|

| // code for func                                  | 0:              |

| action <sub>1</sub>                               | 4:              |

| call p<br>action <sub>2</sub>                     | 56              |

| halt // return to                                 | 0 <b>0 S</b> 60 |

| // code for func<br>action <sub>3</sub><br>return | р               |

|     | Activation record for p<br>(88 bytes) |

|-----|---------------------------------------|

| 0:  | return address                        |

| 4:  | buf                                   |

| 84: | n                                     |

### Target Code for Static Allocation

| text area |                     |                                                  |  |

|-----------|---------------------|--------------------------------------------------|--|

|           |                     | // code for c                                    |  |

| 100:      | ACTION <sub>1</sub> | // assume takes 20 bytes                         |  |

| 120:      | ST 364, #140        | // save return address 140                       |  |

| 132:      | BR 200              | // call p                                        |  |

| 140:      | ACTION <sub>2</sub> |                                                  |  |

| 160:      | HALT                | // terminate, return to OS                       |  |

|           |                     |                                                  |  |

|           |                     | // code for p                                    |  |

| 200:      | ACTION <sub>3</sub> |                                                  |  |

| 220:      | BR *364             | // return to address saved<br>// in location 364 |  |

# stack area with activation records

|      |     | // 300-363 hold the activation<br>// record for c |

|------|-----|---------------------------------------------------|

| 300: |     | // return address                                 |

| 304: |     | // local data for c                               |

|      |     |                                                   |

|      |     | // 364-451 hold the activation<br>// record for p |

| 364: | 140 | // return address                                 |

| 368: |     | // local data for p                               |

|      |     |                                                   |

## **Stack Allocation**

| Code for the caller     |                         |  |

|-------------------------|-------------------------|--|

| LD SP, #stackStart code | // initialize the stack |  |

| HALT                    | // terminate execution  |  |

| Code for procedure call                                                |                                                                                                   |  |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| ADD SP, SP, #caller.ARSize<br>ST *SP, #here + 20<br>BR callee.codeArea | // increment stack pointer<br>// save return address in<br>// callee's frame<br>// jump to caller |  |

| Code for return sequence in the callee |                     |

|----------------------------------------|---------------------|

| BR *0(SP)                              | // return to caller |

| Code for return sequence in the caller |                            |  |  |  |  |  |  |

|----------------------------------------|----------------------------|--|--|--|--|--|--|

| SUB SP, SP, #caller.ARSize             | // decrement stack pointer |  |  |  |  |  |  |

## Target Code for Stack Allocation

|  | 3AC                                            |      |                     |

|--|------------------------------------------------|------|---------------------|

|  | // code for s                                  | 100: | LD SP, #60          |

|  | action <sub>1</sub>                            | 108: | ACTION1             |

|  | call q<br>action <sub>2</sub>                  | 128: | ADD SP, SF          |

|  | halt                                           | 136: | ST 0(SP), #         |

|  |                                                | 144: | BR 300              |

|  | // code for p<br>action <sub>3</sub><br>return | 152: | SUB SP, SF          |

|  |                                                | 160: | ACTION <sub>2</sub> |

|  | // code for g                                  | 180: | HALT                |

|  | action <sub>4</sub>                            |      |                     |

|  | call p<br>action <sub>5</sub>                  |      |                     |

|  | call q                                         |      |                     |

|  | action <sub>6</sub>                            | 200: | ACTION3             |

|  | call q<br>return                               | 220: | BR *0(SP)           |

|  |                                                |      |                     |

|      |                     | // code for s           |

|------|---------------------|-------------------------|

| 100: | LD SP, #600         | // initialize the stack |

| 108: | ACTION1             | // code for $action_1$  |

| 128: | ADD SP, SP, #ssize  | // call sequence begins |

| 136: | ST 0(SP), #152      | // push return address  |

| 144: | BR 300              | // call q               |

| 152: | SUB SP, SP, #ssize  | // restore SP           |

| 160: | ACTION <sub>2</sub> |                         |

| 180: | HALT                |                         |

|      |                     |                         |

|      |                     |                         |

|      |                     | // code for p           |

| 200: | ACTION <sub>3</sub> |                         |

| 220: | BR *0(SP)           | // return to caller     |

|      |                     | // code for q              |

|------|---------------------|----------------------------|

| 300: | ACTION <sub>4</sub> | // conditional jump to 456 |

| 320: | ADD SP, SP, #qsize  |                            |

| 328: | ST 0(SP), #344      | // push return address     |

| 336: | BR 200              | // call p                  |

| 344: | SUB SP, SP, #qsize  | // restore SP              |

| 352: | ACTION5             |                            |

| 372: | ADD SP, SP, #qsize  |                            |

| 380: | ST 0(SP), #396      | // push return address     |

| 388: | BR 300              | // call q                  |

| 396: | SUB SP, SP, #qsize  | // restore SP              |

| 404: | ACTION <sub>6</sub> |                            |

| 424: | ADD SP, SP, #qsize  |                            |

| 432: | ST 0(SP), #448      | // push return address     |

| 440: | BR 300              | // call q                  |

| 448: | SUB SP, SP, #qsize  | // restore SP              |

| 456: | BR *0(SP)           | // return to caller        |

600:

Swarnendu Biswas (IIT Kanpur)

// stack starts

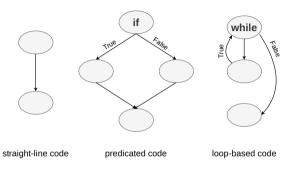

# **Basic Blocks and Control Flow Graphs**

## Basic Block (BB)

### Definition

A BB is a maximal sequence of instructions with only one entry and one exit point

- Entry is at the start of the BB, and exit is from the end of the BB

- Only the start/leader instruction can be the target of a JUMP instruction

- There are no jumps in or out of the middle of a BB

- Identifying BBs

- (i) The first instruction of the input code is a **leader**

- (ii) Instructions that are targets of conditional/unconditional jumps are leaders

- (iii) Instructions that immediately follow conditional/unconditional jumps are leaders

### Identifying BBs

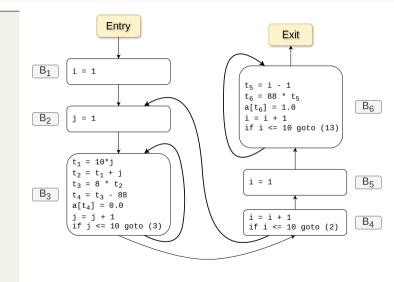

- Statements (1), (2), (3), (10), (12), and (13) are leaders

- There are six BBs: (1), (2), (3)-(9), (10)-(11), (12), (13)-(17)

# Control Flow Graph (CFG)

- Graphical representation of control flow during execution of a program

- Each node represents a statement or a BB

- An entry and an exit node are often added to a CFG for a function

- An edge represents the possible transfer of control between nodes

- Used for static program analysis (e.g., compiler optimizations like instruction scheduling and global register allocation)

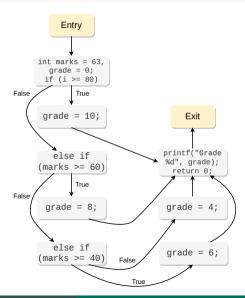

### Example of BBs and a CFG

```

int main() {

int marks = 63, grade = 0;

if (marks \geq 80)

grade = 10;

else if (marks >= 60)

arade = 8:

else if (marks >= 40)

grade = 6;

else

grade = 4;

printf("Grade \%d", grade);

return 0:

3

```

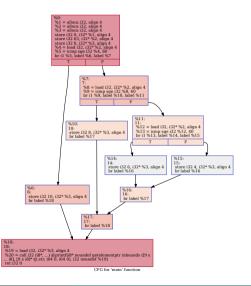

## Example CFG Generated with LLVM

```

int main() {

int marks = 63, grade = 0;

if (marks \geq 80)

grade = 10:

else if (marks >= 60)

arade = 8:

else if (marks >= 40)

grade = 6;

else

grade = 4;

printf("Grade \%d", grade);

return 0:

```

\$ clang++ -S -emit-llvm ctrl-flow.cpp -o ctrl-flow.ll

\$ opt -analyze -enable-new-pm=0 -dot-cfg ctrl-flow.ll

\$ dot -Tpdf -o ctrl-flow.pdf .main.dot

# Loops in a CFG

- A set of CFG nodes L form a loop if L contains a unique loop entry node e such that

- ► *e* is not the Entry node,

- No node in *L* besides *e* has a predecessor outside *L*,

- Only way to reach a node in *L* from outside the loop is through *e*

- Every node in L has a nonempty path to e that is completely within L

- All nodes in the group are strongly connected

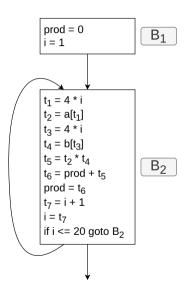

## Example CFG

i = 11 j= 1 2  $t_1 = 10 * i$ 3 4  $t_2 = t_1 + i$ 5  $t_3 = 8 * t_2$  $t_4 = t_3 - 88$ 6  $a[t_4] = 0.0$ 7 i = i + 18 if i <= 10 goto (3) 9 10 i = i + 1if i <= 10 goto (2) 11 i = 112  $t_5 = i - 1$ 13  $t_6 = 88 * t_5$ 14  $a[t_6] = 1.0$ 15 i = i + 116 if i <= 10 goto (13) 17

# **Optimizing BBs**

Local Optimizations

## **Optimization of BBs**

- Code optimizations can lead to substantial improvement in running time and/or energy consumption

- Global optimization analyzes control flow, data flow, and data dependence among BBs

- Local (i.e., intra-BB) optimizations can also provide **significant improvements** in code quality

- ► Local transformations should **not change** the set of expressions computed by a block

- ► Two BBs are equivalent if they compute the same set of expressions

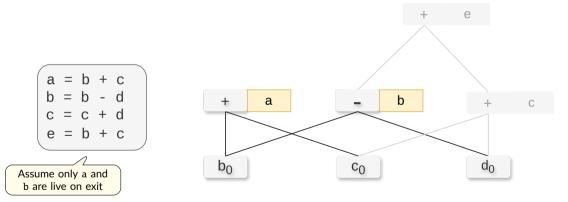

- Expressions are values of names that are live on exit from a BB

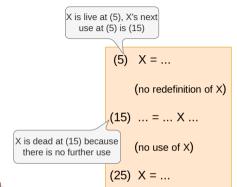

## Next Use and Liveness

- Knowing when the value of a variable will be **used next** is important for generating good code

- For example, can remove variables from registers if not used

- Consider the 3AC instruction I: x = y + z

- ▶ We say *I* defines *x* and uses *y* and *z*

- If a statement J uses x and control can flow from I to J along a path where x is not redefined, then J uses the value of x defined at I

### Definition

A name in a BB is **live** at a given point if its value is used after that point

• Given I and J, we say x is live at statement I

### Example of Next Use and Liveness

| Intermediate Code |   | Live | : | Next Use |     |     |

|-------------------|---|------|---|----------|-----|-----|

|                   | х | У    | Z | х        | У   | z   |

| (1) $x = y + z$   | Т | F    | F | (2)      | -   | -   |

| (2) $z = x * 5$   | F |      | Т | -        |     | (3) |

| (3) $y = z - 7$   |   | Т    | Т |          | (4) | (4) |

| (4) $x = z + y$   | F | F    | F | -        | -   | -   |

### **Determining Next Use and Liveness Information**

### Input • A BB (say *B*) of 3AC

- Assume symbol table shows all non-temporary variables in *B* as live on exit and all temporaries are dead on exit

- **Output** Liveness and next use information for each instruction I: x = y op z in B

- Algorithm (i) Scan forward over *B* to initialize liveness and next use information for (i) each used variable in *B*, and (ii) each instruction *I* in *B*

- (ii) Scan backward over *B*. For each instruction I: x = y op z in *B*, do

- ► Copy the liveness and next use information for x, y, and z from the symbol table to tuple I

- ► Update *x*, *y*, and *z*'s symbol table entries

- Set x.live = FALSE and x.next\_use = NONE

- Set y.live = z.live = TRUE and y.next\_use = z.next\_use = I

### Example Computation of Next Use and Liveness Information

|                   | - |      |   |   |     | ormation |   |      |   |   |      |     |

|-------------------|---|------|---|---|-----|----------|---|------|---|---|------|-----|

| Intermediate Code |   | Live | Ś |   | Nex | kt Use   |   | Live | 5 |   | lext | Use |

|                   | х | У    | z | х | У   | Z        | х | У    | Z | х | У    | Z   |

| (1) $x = y + z$   | F | F    | F | - | -   | -        | F | F    | F | - | -    | -   |

| (2) $z = x * 5$   | F | F    | F | - |     | -        | F | F    | F | - |      | -   |

| (3) $y = z - 7$   | F | F    | F |   | -   | -        | F | F    | F |   | -    | -   |

| (4) $x = z + y$   | F | F    | F | - | -   | -        | F | F    | F | - | -    | -   |

|                   |   |      |   |   |     |          | 2 |      |   |   |      |     |

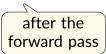

### Example Computation of Next Use and Liveness Information

|                   | Sy | mbo  | ol Ta    | ble Ir | nform  | ation | In  | stru | ctio     | n Info | ormat | tion |

|-------------------|----|------|----------|--------|--------|-------|-----|------|----------|--------|-------|------|

| Intermediate Code |    | Live | <u>;</u> | N      | lext L | Jse   |     | Live | <u>;</u> | Ne     | ext U | se   |

|                   | х  | У    | Z        | х      | У      | Z     | х   | У    | Z        | х      | У     | z    |

| (4) $x = z + y$   | F  | Т    | Т        | -      | (4)    | (4)   | F   | F    | F        | -      | -     | -    |

| (3) $y = z - 7$   | F  | F    | Т        | -      | -      | (3)   | F   | Т    | Т        | -      | (4)   | (4)  |

| (2) $z = x * 5$   | Т  | F    | F        | (2)    | -      | -     | F   | F    | Т        | -      | -     | (3)  |

| (1) $x = y + z$   | F  | Т    | Т        | -      | (1)    | (1)   | Т   | F    | F        | (2)    | -     | -    |

|                   |    |      |          |        |        |       | aft | er t | he       |        |       |      |

backward pass

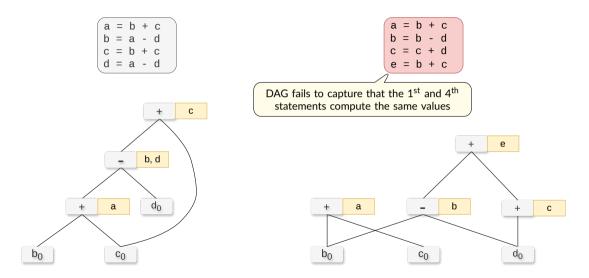

# Structure-Preserving Transformations

- Common subexpression elimination

- ► Instructions compute a value that has been computed

- Dead code elimination

- Remove instructions that define variables that are never used

- Renaming temporary variables

- Can always transform a BB into an equivalent block where each statement that defines a temporary uses a new name

- ► Such a BB is called a normal-form block

- Reordering of dependence-free statements

- Normal-form blocks permit statement interchanges without affecting the value of the block

- May improve latency of accesses and register usage

| a = b + c | a = b + c |

|-----------|-----------|

| b = a - d | b = a - d |

| c = b + c | c = b + c |

| d = a - d | d = b     |

$$t_1 = b + c$$

$$t_2 = x + y$$

## **Algebraic Transformations**

• Apply algebraic laws to simplify computation

| Strength Reduction |         |  |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|--|

| Expensive          | Cheaper |  |  |  |  |  |  |

| x <sup>2</sup>     | x * x   |  |  |  |  |  |  |

| 2 * x              | x + x   |  |  |  |  |  |  |

| x / 2              | x >> 1  |  |  |  |  |  |  |

$$x + 0 = 0 + x = x x * 1 = 1 * x = x x - 0 = x x / 1 = x$$

- Constant folding evaluates constants during compilation (e.g., i = 2 \* 3.14 \* 300 \* 300;)

- Relational operators can generate common sub-expressions (e.g., x > y and x y)

### DAG Representation of BBs

Many optimizations are easier to perform on a DAG representation of BBs

#### Representing BBs with DAGs

- Rules on the DAG structure

- ► Leaf nodes are labeled with variable names or constants

- ► Initial values for each variable are represented by a node

- ► A node *N* is associated with each statement *s* in a BB

- ► Children of *N* correspond to statements that last define the operands used in *s*

- Inner nodes are labeled by an operator symbol

- ▶ Node *N* is labeled by the operator applied at *s*

- ► Nodes optionally have a sequence of identifiers for labels

- Output nodes are those variables that are live on exit

- Each BB node in a CFG can be represented with a DAG

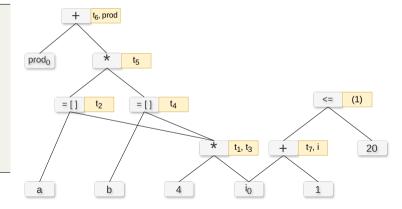

## Constructing a DAG

- Input A basic block (BB)

- Output A DAG for the BB with the following information

- a label for each node (ID for leaf nodes and operator symbols for interior nodes)

- ► a list of identifiers (not constants) for each node

#### Assumptions

- Three kinds of 3AC: (i) x = y op z, (ii) x = op y, and (iii) x = y

- ullet Relational statements like if i  $\,\leq\,$  20 goto (1) are treated like case (i)

- Steps For each statement in the BB,

- (i) If *node*(*y*) is undefined, create a leaf labeled *y* and set *node*(*y*) to the new node

- (ii) For case (i), check if there is a node in the DAG labeled op with left child node(y) and right child node(z). If not, then create a node (denoted by n).

- (iii) For case (ii), check if there is a node labeled op with *node*(*y*) as the only child. If not, then create a node (denoted by *n*).

- (iv) Delete *x* from the list of identifiers for *node*(*x*). Append *x* to the list of identifiers for the node and set *node*(*x*) to *n*.

#### Local Common Subexpressions

#### **Dead Code Elimination**

- Delete a root node from the DAG if it has no live variables

- ► Repeat till there are no such nodes

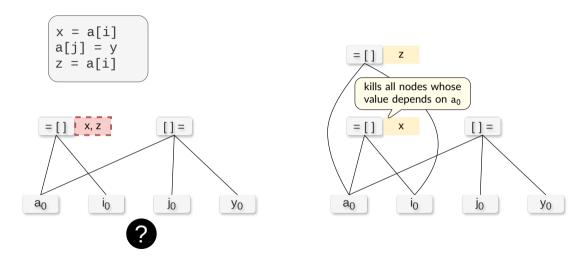

#### **Representing Array References**

### Consider Other Sources of Possible Aliasing

```

// Use of every possible variable

x = *p

// Possible assignment to every variable

*q = y

```

- =\* must include all nodes for optimization analysis

- \*= kills all other nodes

- Possible to use more precise pointer analysis

- Suppose there is a variable *x* defined at a node *n* that is in the scope of a procedure *P*

- We will conservatively assume that *P* uses *x* attached to *n* and kills node *n*

# Code Generation Algorithm

Single Basic Blocks

#### Code Generation Strategy

- Goal

- Assumption

- Generate target code for a sequence of 3AC within a BB

- Every 3AC operator has an equivalent operator in the target language

- Computed values can reside in registers and only need to be saved when

- (i) the register is required for another computation, or

- (ii) just before a procedure call, jump, or a labeled statement

- Implies every register must be saved before the end of a BB

- Steps For each 3AC,

- ► Identify variables that need to be loaded into registers,

- ► Load the variables into registers,

- ► Generate code for the instruction,

- Generate a store if the result needs to be saved in memory.

#### Challenges in Code Generation

| Different Possibilities |                                                                               |                                                                                  |  |  |  |

|-------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| a = b + c               | ADD R <sub>i</sub> , R <sub>i</sub> , R <sub>j</sub>                          | b is in R <sub>i</sub> , c is in R <sub>j</sub> , b is<br>no longer live on exit |  |  |  |

|                         | ADD R <sub>i</sub> ,R <sub>i</sub> ,c                                         | b is in R <sub>i</sub> , b is no longer<br>live on exit                          |  |  |  |

|                         | MOV R <sub>j</sub> ,c<br>ADD R <sub>i</sub> , R <sub>i</sub> , R <sub>j</sub> | b is in R <sub>i</sub> , b is no longer<br>live on exit                          |  |  |  |

#### Usually there will be numerous cases to consider

- An efficient choice depends on several factors (e.g., frequency of use of b and c later)

- Properties of the operator (e.g., commutativity) can add to the complexity

#### A Simple Code Generator

- Treat each IR quadruple as a "macro"

- Replace the macro with pre-existing code templates

Simple to implement but makes inefficient use of registers

Goal: Track values in registers and reuse them

#### **Register and Address Descriptors**

#### **Register Descriptor**

- Keeps track of **what name** is stored in each register, consulted whenever a new register is needed

- Each register holds the value of zero or more names at any time during an execution

#### **Address Descriptor**

- Keeps track of the **location(s)** where the current value of a name can be found at runtime

- Location can be a register, a stack location, a memory address, or some combination of these (data can get copied)

- Information can be stored in the symbol table

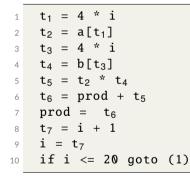

#### Code Generation Algorithm

- For each 3AC instruction *I* of the form x = y op z,

- Invoke function getreg(I) to select registers  $R_x$ ,  $R_y$ , and  $R_z$

- ► If y is not in  $R_y$  according to the address descriptor, then generate instruction LD  $R_y$ , y'

- y' is one of the memory locations for y

- ► Perform the same steps for *z*

- Generate the instruction OP  $R_x, R_y, R_z$

- For a 3AC copy instruction x = y,

- ► If y is not in  $R_y$  according to the address descriptor, then generate instruction LD  $R_y$ , y'

- Adjust the register descriptor for  $R_y$  to include x

### Managing Register and Address Descriptors

- For an instruction LD R, x,

- Change the register descriptor for *R* so it holds only *x*

- ► Change the address descriptor for *x* by adding register *R* as an additional location

- ▶ Remove *R* from the address descriptors of variables other than *x*

- For instruction ST x, R, change the address descriptor for x to include its own memory location

- For an instruction such as ADD  $R_x, R_y, R_z$ , implementing a 3AC x = y + z,

- ► Change the register descriptor for *R<sub>x</sub>* so that it holds only *x*

- Change the address descriptor for x so that its only location is  $R_x$

- ► The memory location for x is no longer in the address descriptor for x

- Remove  $R_x$  from the address descriptor of any variable other than x

- For a copy instruction x = y,

- ► Process the load from *y* into a register, if needed

- Add x to the register descriptor for  $R_y$

- Change the address descriptor for x so that its only location is  $R_y$

#### **Usage of Registers**

- Leave the computed result in a register for as long as possible

- Store the result only at the end of a BB or when the register is needed for another computation

- A variable is live at a point if it is used (possibly in later BBs) later, requires global dataflow analysis

- On exit from a BB, store only live variables which are not already in their memory locations (use address descriptors to identify)

- ► If liveness information is not available, then assume that all variables are live at all times

#### Defining Function getreg()

Input 3AC I: x = y op z

Output Returns registers to hold the value of x, y, and z

Assumption There is no global register allocation

# getreg(): Choosing $R_y$ for y

- 1. If y is in a register, then return the register containing y as  $R_y$

- 2. If y is not in a register, but there is an empty register available, then pick one such register as  $R_y$

- 3. If y is not in a register and there are no empty registers, then

- ► Let *R* be a candidate register and suppose *v* is one of the variables stored in *R*

- Heuristic for candidate selection can be based on farthest references or fewest next use

- ▶ If the address descriptor for *v* says that *v* is somewhere else beside *R*, then choose *R*

- If v is x, and x is not an operand of I (i.e.,  $x \neq z$ ), then choose R

- If v is not used later, then choose R

- Else, generate ST v, R (called a register spill)

- ► *R* may hold several variables, so we need to repeat the previous steps for each variable

- ► Compute the number of store instructions generated for *R* (i.e., score) for each variable

- Pick the register with the lowest score

- Selecting  $R_z$  for z is similar

### getreg(): Choosing $R_x$ for x

- In addition to the previous checks, try the following,

- A register that holds only x is always an acceptable choice for  $R_x$

- ► If y is not used after instruction I, and R<sub>y</sub> holds only y after being loaded, then R<sub>y</sub> can also be used for R<sub>x</sub>

- ▶ Perform similar checks with *R<sub>z</sub>* if required

- If *I* is a copy instruction, then always choose  $R_y$

#### **Code Generation Example**

| 3AC             | Generated Code                                                                                         | - | gister<br>script<br>R <sub>2</sub> |                       | ; <sup>-</sup> ā <sup></sup> | A<br>b | ddress [<br>c    | Desc<br>d | , t       | <u> </u> | es, not live   |

|-----------------|--------------------------------------------------------------------------------------------------------|---|------------------------------------|-----------------------|------------------------------|--------|------------------|-----------|-----------|----------|----------------|

|                 |                                                                                                        |   |                                    |                       | a                            | in men | ory, live at     | d         |           |          | l of the BB    |

| t = a - b       | LD R <sub>1</sub> , a<br>LD R <sub>2</sub> , b<br>SUB R <sub>2</sub> , R <sub>1</sub> , R <sub>2</sub> |   | R <sub>2</sub> is reather is n     | used bec<br>o next us | ause<br>se of b              |        | d of the BB      |           |           |          |                |

|                 |                                                                                                        | а | t                                  |                       | a, $R_1$                     | b      | С                | d         | $R_2$     |          |                |

| u = a - c       | LD $R_3$ , c<br>SUB $R_1$ , $R_1$ , $R_3$                                                              |   |                                    |                       |                              |        |                  |           |           |          |                |

|                 |                                                                                                        | u | t                                  | с                     | а                            | b      | c,R <sub>3</sub> | d         | $R_2$     | $R_1$    |                |

| v = t + u       | ADD $R_3$ , $R_2$ , $R_1$                                                                              |   |                                    |                       |                              |        |                  |           |           |          |                |

|                 |                                                                                                        | u | t                                  | v                     | а                            | b      | С                | d         | $R_2$     | $R_1$    | R <sub>3</sub> |

| Swarnendu Biswa | is (IIT Kanpur)                                                                                        | ( | CS 335: C                          | ode Gen               | eration                      |        |                  | Sem       | n 2023-24 | <br> -   | 53/9           |

53/90

#### Code Generation Example

| Generated Code                               | <b>Register Descriptor</b>                                                                                |                                                                                                                                                                                                               |                                                                                                                                                                                  | Address Descriptor                                                                                                                                                                 |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |                                                                            |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                              | $R_1$                                                                                                     | R <sub>2</sub>                                                                                                                                                                                                | R <sub>3</sub>                                                                                                                                                                   | а                                                                                                                                                                                  | b                                                                                                                                                                                                                                                                   | с                                                                                                                                                                                                                   | d                                                  | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | u                                                                  | v                                                                          |

|                                              | •••                                                                                                       |                                                                                                                                                                                                               | •••                                                                                                                                                                              | •••                                                                                                                                                                                | •••                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                     | •••                                                | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •••                                                                |                                                                            |

|                                              | u                                                                                                         | t                                                                                                                                                                                                             | v                                                                                                                                                                                | а                                                                                                                                                                                  | b                                                                                                                                                                                                                                                                   | с                                                                                                                                                                                                                   | d                                                  | $R_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $R_1$                                                              | $R_3$                                                                      |

| LD R <sub>2</sub> , d                        |                                                                                                           |                                                                                                                                                                                                               |                                                                                                                                                                                  |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |                                                                            |

|                                              | u                                                                                                         | a,d                                                                                                                                                                                                           | v                                                                                                                                                                                | $R_2$                                                                                                                                                                              | b                                                                                                                                                                                                                                                                   | С                                                                                                                                                                                                                   | $d, R_2$                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $R_1$                                                              | $R_3$                                                                      |

| ADD $R_1$ , $R_3$ , $R_1$                    |                                                                                                           |                                                                                                                                                                                                               |                                                                                                                                                                                  |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |                                                                            |

|                                              | d                                                                                                         | a                                                                                                                                                                                                             | v                                                                                                                                                                                | $R_2$                                                                                                                                                                              | b                                                                                                                                                                                                                                                                   | с                                                                                                                                                                                                                   | $R_1$                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    | R <sub>3</sub>                                                             |

| ST a, R <sub>2</sub><br>ST d, R <sub>1</sub> |                                                                                                           |                                                                                                                                                                                                               |                                                                                                                                                                                  |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |                                                                            |

|                                              | d                                                                                                         | a                                                                                                                                                                                                             | v                                                                                                                                                                                | $R_2$                                                                                                                                                                              | b                                                                                                                                                                                                                                                                   | с                                                                                                                                                                                                                   | $R_1$                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    | R <sub>3</sub>                                                             |

|                                              | <br>LD R <sub>2</sub> , d<br>ADD R <sub>1</sub> , R <sub>3</sub> , R <sub>1</sub><br>ST a, R <sub>2</sub> | Generated Code $R_1$ u         u           LD R <sub>2</sub> , d         u           ADD R <sub>1</sub> , R <sub>3</sub> , R <sub>1</sub> u           ST a, R <sub>2</sub> d           ST d, R <sub>1</sub> u | Generated Code $R_1$ $R_2$ u         t           LD R_2, d         u         a,d           ADD R_1, R_3, R_1         u         a           ST a, R_2         ST d, R_1         u | Generated Code $R_1$ $R_2$ $R_3$ u       t       v         LD R_2, d       u       a,d       v         ADD R_1, R_3, R_1       d       a       v         ST a, R_2       ST d, R_1 | Generated Code $R_1$ $R_2$ $R_3$ a                 u       t       v       a         LD R_2, d       u       a, d       v       R_2         ADD R_1, R_3, R_1       u       a       v       R_2         ST a, R_2       ST a, R_1       u       a       v       R_2 | Generated Code $R_1$ $R_2$ $R_3$ a       b                   u       t       v       a       b         LD $R_2$ , d             ADD $R_1$ , $R_3$ , $R_1$ d       a       v $R_2$ b         ST a, $R_2$ ST d, $R_1$ | Generated Code $R_1$ $R_2$ $R_3$ a       b       c | Generated Code $R_1$ $R_2$ $R_3$ a         b         c         d <td< td=""><td>Generated Code       <math>R_1</math> <math>R_2</math> <math>R_3</math>       a       b       c       d       t                                                                                                       </td><td>Generated Code       <math>R_1</math> <math>R_2</math> <math>R_3</math>       a       b       c       d       t       u                                                                                                      </td></td<> | Generated Code $R_1$ $R_2$ $R_3$ a       b       c       d       t | Generated Code $R_1$ $R_2$ $R_3$ a       b       c       d       t       u |

54/90

#### Code Sequences for Indexed and Pointer Assignments

| 3AC      | i in Register $\mathtt{R}_i$ | i in Memory $\mathtt{M}_{i}$          | i in Stack                               |  |  |

|----------|------------------------------|---------------------------------------|------------------------------------------|--|--|

| a = b[i] | MOV b(R <sub>i</sub> ), R    | MOV M <sub>i</sub> , R<br>MOV b(R), R | MOV S <sub>i</sub> (A), R<br>MOV b(R), R |  |  |

| a[i] = b | MOV b, a(R <sub>i</sub> )    | MOV M <sub>i</sub> , R<br>MOV b, a(R) | MOV S <sub>i</sub> (A), R<br>MOV b, a(R) |  |  |

| 3AC    | p in Register R <sub>p</sub> | p in Memory $M_p$                   | p in Stack                             |

|--------|------------------------------|-------------------------------------|----------------------------------------|

| a = *p | MOV *R <sub>p</sub> , a      | MOV M <sub>p</sub> , R<br>MOV *R, R | MOV S <sub>p</sub> (A), R<br>MOV *R, R |

| *p = b | MOV a, *R <sub>p</sub>       | MOV M <sub>p</sub> , R<br>MOV a, *R | MOV a, R<br>MOV R, *S <sub>p</sub> (A) |

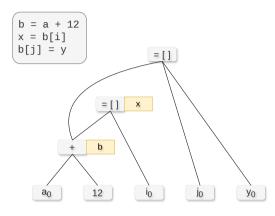

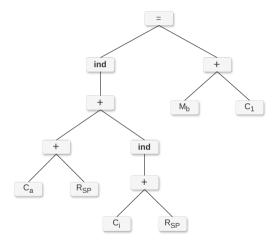

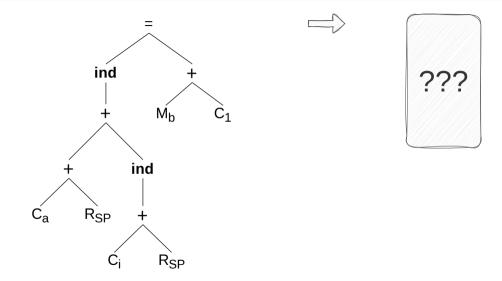

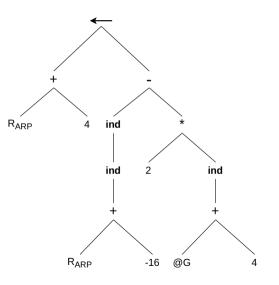

# Code Generation with Tree Rewriting

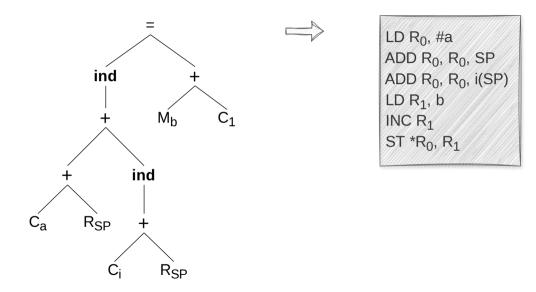

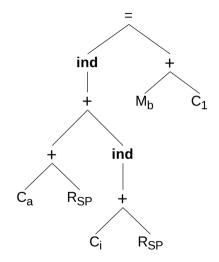

#### **Tree Representation**

- Consider the statement a[i] = b + 1

- ► Assume b is in memory location M<sub>b</sub>

- Array of chars a is a local variable and is stored on the stack

- SP points to the beginning of the current activation record

- Addresses of locals a and i are given as constant offsets C<sub>a</sub> and C<sub>i</sub> from the SP

#### Operator ind denotes indirection

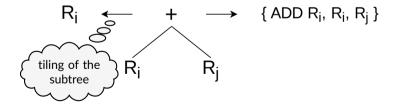

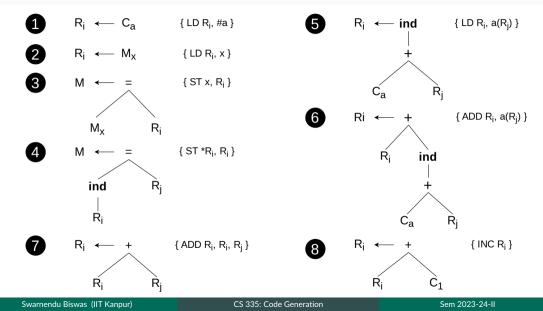

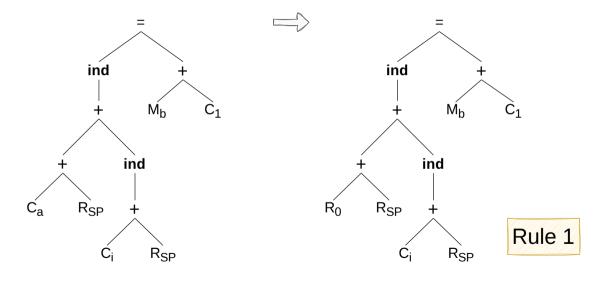

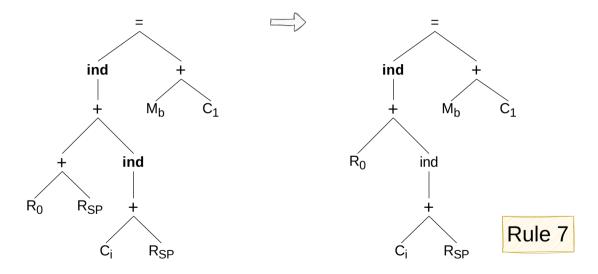

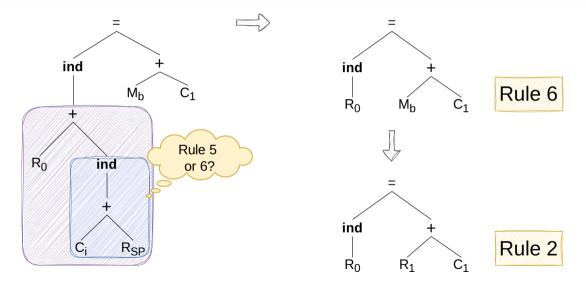

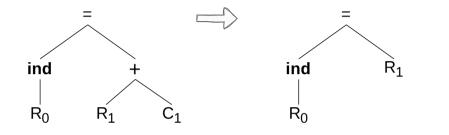

#### **Tree Rewriting**

- Target code can be generated by applying a sequence of tree-rewriting rules to reduce the input tree to a single node

- Each rewrite rule is of the form *replacement* ← *template* { *action* }, where *replacement* is a single node, *template* is a tree, and *action* is a code fragment like in a SDT

- A set of tree rewriting rules is called a tree-translation scheme

#### **Tree Rewriting Rules**

### Code Generation by Tiling an Input Tree

- High-level steps in a tree-translation scheme

- Given an input tree, the templates in the tree-rewriting rules are applied to tile its subtrees

- **Tiling** implies reducing a subtree with the *replacement* node

- ► If a template matches, replace the matching subtree with the replacement node of the rule

- Execute the action associated with the rule

- If the action contains a sequence of instructions, the instructions are emitted

- Repeat the above steps until the tree is reduced to a single node, or until no more templates match

- Output of the tree-translation scheme is the instruction sequence generated as the input tree is reduced to a single node

Μ

#### Considerations during Tree Reduction

- Performance of tree matching impacts the efficiency of code generation at compile time

- Multiple templates may match during code generation

- Different match sequences of templates will lead to different code being generated which can also impact efficiency

- If no template matches, then the code-generation process blocks

- Assume each operator in the intermediate code can be implemented by one or more target-machine instructions

- ► Assume there are sufficient registers to compute each tree node by itself

- How can you **match** tree patterns?

- Represent each template as a set of strings, where a string represents a path from the root to a leaf in the template

- Perform depth-first traversal to match a subtree to a template

## Pattern Matching with LR Parsing

- Convert the input tree to a string using prefix (or postfix) form for comparison

- Use a parsing mechanism for pattern matching

- Come up with a syntax-directed translation (SDT) as an alternate for tree rewriting rules

Prefix representation = = ind + +  $C_aR_{SP}$  ind +  $C_iR_{SP}$  +  $M_bC_1$

# SDT for Tree Rewriting

- Terminal m represents a memory location

- Terminal sp represents register SP

- Terminal c represents a constant

- Design a code generator for a different architecture by rewriting the grammar

- Resolve conflicts using estimates of instruction costs, favoring larger reductions, and favoring shifts over reductions

| Production                                                   | Semantic Action                                          |

|--------------------------------------------------------------|----------------------------------------------------------|

| $R_i  ightarrow \mathbf{c}_a$                                | LD R <sub>i</sub> , #a                                   |

| $R_i \rightarrow M_X$                                        | LD R <sub>i</sub> , x                                    |

| $M \rightarrow = M_X R_i$                                    | ST x, R <sub>i</sub>                                     |

| $M \rightarrow = \operatorname{ind} R_i R_j$                 | ST *R <sub>i</sub> , R <sub>j</sub>                      |

| $R_i \rightarrow \mathbf{ind} + \mathbf{c}_a R_j$            | LD R <sub>i</sub> , a(R <sub>j</sub> )                   |

| $R_i \rightarrow +R_i \operatorname{ind} + \mathbf{c}_a R_j$ | ADD R <sub>i</sub> , R <sub>i</sub> , a(R <sub>j</sub> ) |

| $R_i \rightarrow +R_iR_j$                                    | ADD R <sub>i</sub> , R <sub>i</sub> , R <sub>j</sub>     |

| $R_i \rightarrow +R_i \mathbf{c}_1$                          | INC Ri                                                   |

| R  ightarrow sp                                              |                                                          |

| $M \rightarrow \mathbf{m}$                                   |                                                          |

# Dynamic Programming Based Optimal Code Generation

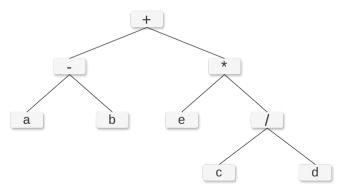

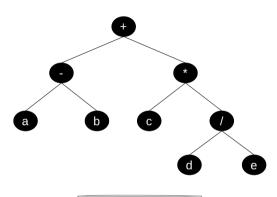

#### **Expression Trees**

#### Definition

An expression tree is a syntax tree for an expression

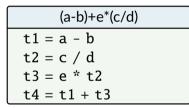

# Generating Code for Expression Trees

Expression tree

Assume only two registers  $\mathsf{R}_0$  and  $\mathsf{R}_1$  are available

- $_1$  LD  $R_0$ , a

- 2 SUB R<sub>0</sub>, R<sub>0</sub>, b

- 3 LD  $R_1$ , d

- 4 DIV R<sub>1</sub>, R<sub>1</sub>, e

- 5 ST t<sub>1</sub>, R<sub>0</sub>

- $^{6}$  LD R<sub>0</sub>, c

- 7 MUL  $R_0$ ,  $R_0$ ,  $R_1$

- 8 ADD  $R_0$ ,  $R_0$ ,  $t_1$

### Is the generated code optimal?

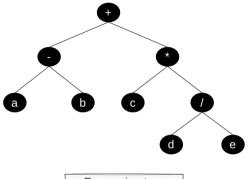

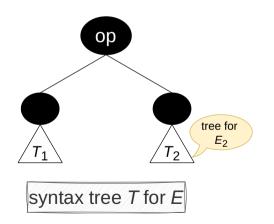

### Dynamic Programming Based Optimal Code Generation

- Generates optimal code from an expression tree

- Algorithm partitions the problem of generating optimal code for an expression into sub-problems of generating optimal code for sub-expressions

- ► To generate optimal code for an expression  $E = E_1$  op  $E_2$ , generate optimal code for  $E_1$ ,  $E_2$ , and the operator op in order, or  $E_2$ ,  $E_1$  and then op

- Models register machines with complex instruction sets

- Assume there are *r* interchangeable registers  $R_0, \ldots, R_{r-1}$

- Instructions are of the following form

$$\blacktriangleright R_i = M_j, R_i = R_i \text{ op } R_j, R_i = R_i \text{ op } M_j, R_i = R_j, \text{ and } M_i = R_j$$

# Contiguous Evaluation

- The optimality criterion requires **contiguous evaluation** of an expression tree

- The optimal program has less or the same cost and uses no more registers

- A program *P* evaluates a tree *T* contiguously if

- ► it first evaluates those subtrees of T that need to be computed into memory,

- ► it then evaluates T1, T2, and then root, in order, or T2, T1, and then root, in order

- Evaluating part of *T*1 leaving the result in a register, evaluating *T*2, and then evaluating rest of *T*1 is not contiguous evaluation

# Assume E is $E_1$ op $E_2$

### Judicious Use of Registers

Given an expression tree for  $E = E_1$  op  $E_2$  and a target with *r* registers

Assume E is  $E_1$  op  $E_2$ tree for  $E_2$ syntax tree T for E

Suppose evaluating  $T_1$  and  $T_2$  require  $r_1$  and  $r_2$  registers, respectively

- $r \ge r_1 > r_2$   $r_1 1$  registers are freed after evaluation of  $T_1$ , one register holds the result

- $T_2$  can be evaluated in  $r_1 1$  registers

- T can be evaluated in  $r_1$  registers

- $r_1 > r$  or  $r_2 > r$  Require register spills

$r_1 == r_2$  • Need  $r_1 + 1$  registers to evaluate T

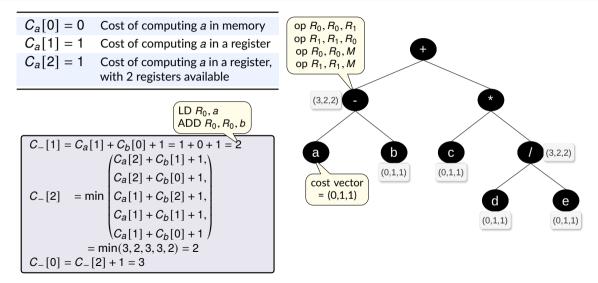

# Dynamic Programming Algorithm

#### Assumption The target has *r* registers

- Steps 1. Compute bottom-up for each node *n* of the expression tree *T* an array *C* of costs

- ► C[i] is the minimum cost of computing the subtree S rooted at n into a register, assuming i registers are available for the computation, for 1 < i < r</p>

- The cost of computing a node n includes the count of loads and stores necessary to evaluate S in the given number of registers plus the cost of computing the operator at the root of S

- 2. Traverse *T*, using the cost vectors to determine which subtrees of *T* must be computed into memory

- 3. Traverse each tree using the cost vectors and associated instructions to generate the final target code

- Code for the subtrees computed into memory locations is generated first, then code for other subtrees, and then code for the root

- Consider a target machine having two registers *R*<sub>0</sub> and *R*<sub>1</sub>

- Assume that the list of available instructions is as follows

| LD <i>R</i> <sub>i</sub> , <i>M</i> <sub>j</sub> |

|--------------------------------------------------|

| op $R_i, R_i, R_j$                               |

| op $R_i, R_i, M_j$                               |

| LD <i>R</i> <sub>i</sub> , <i>R</i> <sub>j</sub> |

| ST <i>M</i> <sub>i</sub> , <i>R</i> <sub>j</sub> |

Algorithm can be extended to cases where instructions have varying costs

Expression tree

# Expression Tree with Cost Vectors

# **Expression Tree with Cost Vectors**

$C_*[1] = C_c[1] + C_{/}[0] + 1 = 1 + 3 + 1 = 5$   $C_*[2] = \min\left(\begin{array}{c} C_c[2] + C_{/}[1] + 1, \\ C_c[2] + C_{/}[0] + 1, \\ C_c[1] + C_{/}[2] + 1, \\ C_c[1] + C_{/}[2] + 1, \\ C_c[1] + C_{/}[1] + 1, \\ C_c[1] + C_{/}[0] + 1 \end{array}\right)$   $= \min(4, 5, 4, 4, 5) = 4$   $C_*[0] = C_*[2] + 1 = 5$

$$C_{+}[1] = C_{-}[1] + C_{*}[0] + 1 = 2 + 5 + 1 = 8$$

$$C_{-}[2] + C_{*}[1] + 1,$$

$$C_{-}[2] + C_{*}[0] + 1,$$

$$C_{-}[1] + C_{*}[2] + 1,$$

$$C_{-}[1] + C_{*}[1] + 1,$$

$$C_{-}[1] + C_{*}[0] + 1$$

$$= \min(8, 8, 7, 8, 8) = 7$$

$$C_{+}[0] = C_{+}[2] + 1 = 8$$

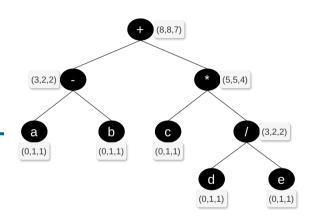

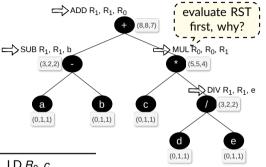

# Tree Traversal to Generate Code

- Minimum cost at node + is 7, which implies right subtree (RST) is computed with 2 registers in R<sub>0</sub> and left subtree (LST) is computed with 1 register into R<sub>1</sub>

- For node \*, compute RST with one register in *R*<sub>1</sub> and LST in *R*<sub>0</sub>

- For node c, emit LD  $R_0$ , c

- For node /, compute RST in memory and compute LST in *R*<sub>1</sub>

- For node d, emit LD  $R_1$ , d

- For node –, compute RST in memory and compute LST in *R*<sub>1</sub>

- For node a, emit LD  $R_1$ , a

79/90

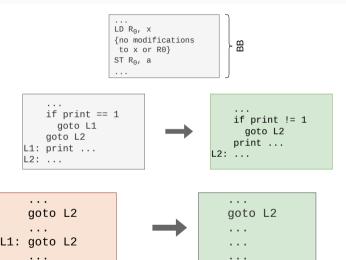

# Code Generation via Peephole Optimization

### Peephole Optimization

- Insight: Find local optimizations by examining short sequences of nearby operations

- ► The sliding window, or the peephole, moves over code

- Code in a peephole need not be contiguous

- ► Goal is to identify code patterns that can be improved

- Rewrite code patterns with improved sequence

# **Examples of Peephole Optimizations**

- Eliminate redundant instructions

- Eliminate unreachable code

- Eliminate jump over jumps

- Algebraic simplification

- Strength reduction

. . .

. . .

. . .

L1:

• Use of machine idioms

goto L1

goto L2

# Peephole Optimization-based Code Generation

- A naïve optimization strategy can use exhaustive search to match the patterns and rewrite code

- ► Can work if number of patterns and the window size are small

- Does not work for modern complex ISAs

- Workflow in a modern peephole optimizer

- **Expander** rewrites the IR to represent all the direct effects of an operation

- If OP R<sub>0</sub>, R<sub>1</sub>, R<sub>2</sub> sets a condition code, then the LLIR should include an explicit operation to set the code

- ► Simplifier performs limited local optimization on the LLIR in the window

- ► Matcher compares the simplified LLIR against the pattern library

- In an optimizer, the input and output languages are the same

- With a different output language (e.g., ASM), the optimizer can be used for code generation

- AST computes  $a = b 2 \times c$

- ► a is stored at offset 4 in the local AR

- b stored as a call-by-reference parameter whose pointer is stored at offset – 16 from the ARP

- ► *c* is at offset 12 from the label @*G*

| Ор | $Arg_1$ | $Arg_2$               | Result                |

|----|---------|-----------------------|-----------------------|

| ×  | 2       | С                     | <i>t</i> <sub>1</sub> |

| _  | b       | <i>t</i> <sub>1</sub> | а                     |

| Ор                    | Arg <sub>1</sub>                 | Arg <sub>2</sub>      | Result                |

|-----------------------|----------------------------------|-----------------------|-----------------------|

| ×                     | 2                                | С                     | <i>t</i> <sub>1</sub> |

| -                     | b                                | <i>t</i> <sub>1</sub> | а                     |

| +<br>R <sub>ARP</sub> | 4 ind<br>ind<br>R <sub>ARP</sub> | -<br>2<br>-16 @0      | ind<br>+<br>5 4       |

$1 R_{10} = 2$  $1 R_{10} = 2$  $2 R_{11} = @G$  $2 R_{11} = @G$ Expand 3  $R_{12} = 12$ Simplify 3  $R_{14} = M(R_{11} + 12)$  $4 R_{13} = R_{11} + R_{12}$ 4  $R_{15} = R_{10} \times R_{14}$  $5 R_{14} = M(R_{13})$  $5 R_{18} = M(R_{ABP} - 16)$  $6 R_{15} = R_{10} \times R_{14}$  $6 R_{19} = M(R_{18})$  $7 R_{16} = -16$  $7 R_{20} = R_{19} - R_{15}$  $8 R_{17} = R_{ABP} + R_{16}$ 8  $M(R_{ABP}+4) = R_{20}$ 9  $R_{18} = M(R_{17})$ 10  $R_{19} = M(R_{18})$ 11  $R_{20} = R_{19} - R_{15}$ fewer instruc-12  $R_{21} = 4$ tions and registers 13  $R_{22} = R_{ARP} + R_{21}$ 14  $M(R_{22}) = R_{20}$ assume a sliding window of size 3

Swarnendu Biswas (IIT Kanpur)

Sem 2023-24-II

# Sequences Produced by the Simplifier

| $1 R_{10} = 2$                    | Sequence 1                 | Sequence 4                      | Sequence 7                      |

|-----------------------------------|----------------------------|---------------------------------|---------------------------------|

| $2 R_{11} = @G$                   | $R_{10} = 2$               | $R_{11} = @G$                   | $R_{15} = R_{10} \times R_{14}$ |

| $_{3}$ R <sub>12</sub> = 12       | $R_{11} = @G$              | $R_{14} = M(R_{11} + 12)$       | $R_{17} = R_{ARP} - 16$         |

| $4 R_{13} = R_{11} + R_{12}$      | $R_{12} = 12$              | $R_{15} = R_{10} \times R_{14}$ | $R_{18} = M(R_{17})$            |

| $5 R_{14} = M(R_{13})$            |                            |                                 |                                 |

| $6 R_{15} = R_{10} \times R_{14}$ |                            |                                 |                                 |

| $7 R_{16} = -16$                  | Sequence 2                 | Sequence 5                      | Sequence 8                      |

| 8 $R_{17} = R_{ARP} + R_{16}$     | $R_{11} = @G$              | $R_{14} = M(R_{11} + 12)$       | $R_{15} = R_{10} \times R_{14}$ |

| 9 $R_{18} = M(R_{17})$            | $R_{12} = 12$              | $R_{15} = R_{10} \times R_{14}$ | $R_{18} = M(R_{ARP} - 16)$      |

| $R_{19} = M(R_{18})$              | $R_{13} = R_{11} + R_{12}$ | $R_{16} = -16$                  | $R_{19} = M(R_{18})$            |

| $1 R_{20} = R_{19} - R_{15}$      |                            |                                 |                                 |

| $2 R_{21} = 4$                    | Sequence 3                 | Sequence 6                      | Sequence 9                      |

| $3 R_{22} = R_{ARP} + R_{21}$     | $R_{11} = @G$              | •                               | $R_{18} = M(R_{ARP} - 16)$      |

| 4 $M(R_{22}) = R_{20}$            |                            | $R_{15} = R_{10} \times R_{14}$ |                                 |

|                                   | $R_{13} = R_{11} + 12$     | $R_{16} = -16$                  | $R_{19} = M(R_{18})$            |

|                                   | $R_{14} = M(R_{13})$       | $R_{17} = R_{ARP} + R_{16}$     | $R_{20} = R_{19} - R_{15}$      |

# Sequences Produced by the Simplifier