## Optimized Coherence Tracking and Private Caching in Many-core Server Processors

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> by Sudhanshu Shukla

> > $to \ the$

#### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

INDIAN INSTITUTE OF TECHNOLOGY KANPUR

April, 2019

## CERTIFICATE

It is certified that the work contained in the thesis entitled "Optimized Coherence Tracking and Private Caching in Many-core Server Processors", by Sudhanshu Shukla, has been carried out under my supervision and that this work has not been submitted elsewhere for a degree.

Marinah Chandham

Dr. Mainak Chaudhuri Department of Computer Science and Engineering Indian Institute of Technology Kanpur

November, 2018

## Synopsis

The cache-coherent many-core server processors are traditionally designed with a per-core private cache hierarchy and a large shared multi-banked last-level cache (LLC). The private cache contents are kept coherent with the help of a scalable cache coherence protocol. An important storage structure employed by the cache coherence protocol is the sparse directory, which keeps track of the location(s) of the cache blocks in the private caches. The height or the number of entries in the sparse directory puts an upper bound on the number of cache blocks that can be tracked simultaneously at any point in time. The width of the sparse directory puts an upper bound on the number of simultaneous sharers of a cache block depending on the encoding format of the sharers. Even after decades of research, design of a space-efficient sparse directory that can scale seamlessly and offer high performance without curtailing the degree of sharing remains one of the most important problems in cache-coherent many-core server processors. In this thesis, we present novel solutions for optimizing the width and height of the sparse directory. In addition to the space overhead of coherence tracking, a many-core processor suffers from large round-trip latency overhead and traffic overhead in the interconnect between the per-core private cache hierarchy and the shared LLC banks. The cache coherence protocol, the sparse directory organization, and the efficiency of the private cache hierarchy together determine the latency and traffic overhead. While our sparse directory proposals exhibit significant savings in the interconnect traffic, we propose a more direct solution to this important problem by taking a fresh look at the private cache hierarchy architecture in the context of popular server workloads. In this thesis, we propose a novel space-efficient private cache hierarchy architecture that outperforms the traditional private cache hierarchy designs in terms of interconnect traffic and execution time.

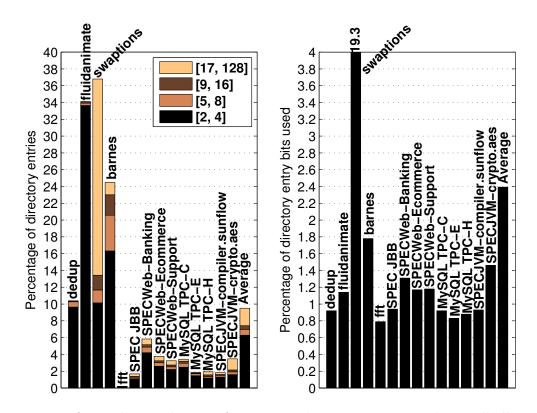

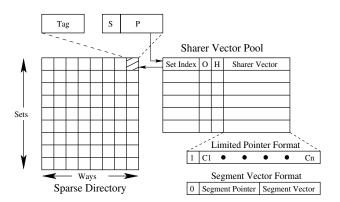

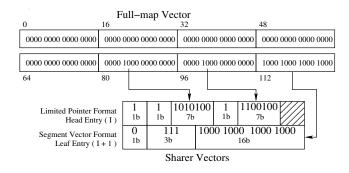

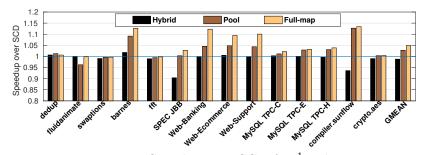

Our width-optimized sparse directory proposal exploits the observation that multithreaded applications typically require two types of directory entries, namely, limited pointer entries tracking a few sharers of a block and bitvector entries tracking larger number of sharers for widely shared blocks. While this is a well-known behavior, the difficulty in employing this observation to practice in a space-efficient manner arises from the fact that the exact proportion of these two types of entries varies across applications and across phases even within the same application. Recent proposals aiming to optimize the average number of bits per directory entry have organized the sparse directory as either a static mix of these two types of entries with a pre-defined proportion or a collection of relatively short bitvector entries that can encode either a limited number of sharer pointers or a larger number of sharers hierarchically. In either case, sparse directory space is wasted depending on the run-time characteristics of the application. We present a directory organization that facilitates allocation of the two different types of directory entries dynamically. Our design maintains a pool of limited pointer entries, where each entry can also double as a segment directory entry encoding the sharers in a cluster of cores. Each tag in the primary sparse directory array has a pointer that can either represent a sharer or point to an entry in the pool. When multiple segment directory entries are needed to encode all the sharers of a block, our pool management protocol guarantees that all these entries are allocated contiguously so that maintaining a pointer to the head entry is enough. Detailed simulation results show that our Pool Directory proposal incorporated in a 128-core system running multi-threaded applications drawn from scientific, general-purpose, and commercial computing domains can offer, on average, 5% improvement in performance and 20% savings in interconnect traffic compared to the state-of-the-art scalable coherence directory (SCD) proposal when using a  $\frac{1}{16} \times$  sparse directory.

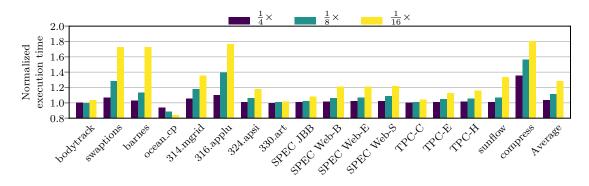

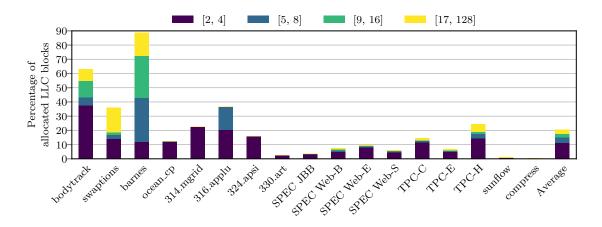

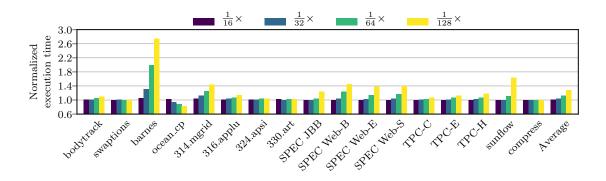

Recent notable research efforts for optimizing the sparse directory height have largely followed two directions. First, the observation that private coarse-grain regions can be tracked in a single directory entry has motivated researchers to explore support for multigrain coherence. Second, pages or blocks have been identified dynamically as private respectively by the operating system (OS) or the hardware. The blocks thus marked private are not tracked by the directory saving directory entries. However, when such a block is shared at a later point, a costly non-scalable broadcast-based recovery mechanism is needed. In this thesis, we design a robust minimally-sized sparse directory that can offer adequate performance while enjoying the simplicity, scalability, and OS-independence of traditional broadcast-free block-grain coherence. We begin our exploration with a naïve design that does not have a sparse directory and the location/sharers of a block are tracked by borrowing a portion of the block's LLC data way. Such a design, however, lengthens the critical path from two transactions to three transactions (two hops to three hops) for the blocks that experience frequent shared read accesses. This is because the LLC data way cannot provide the block in such cases as part of the LLC block is corrupted with tracking information. We address this problem by architecting a tiny sparse directory that dynamically identifies and tracks a selected subset of the blocks that experience a large volume of shared accesses. However, it is difficult to appropriately size this tiny directory, since the actual footprint of the shared blocks varies across applications and across phases even within the same application. Therefore, to make the design robust, we further augment the tiny directory proposal with an option of selectively spilling directory entries into the LLC space for tracking the coherence of the critical shared blocks that the tiny directory fails to accommodate. Our Tiny Directory proposal operating with  $\frac{1}{32} \times$  to  $\frac{1}{256}$  × sparse directories offers performance within a percentage of a traditional 2× sparse directory in a 128-core system. The Tiny Directory design outperforms the state-of-the-art by very large margins when operating with the same number of directory entries.

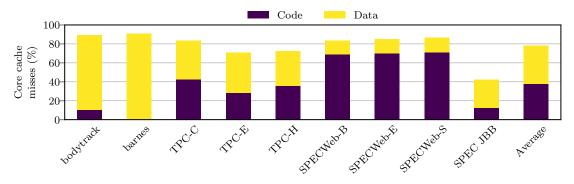

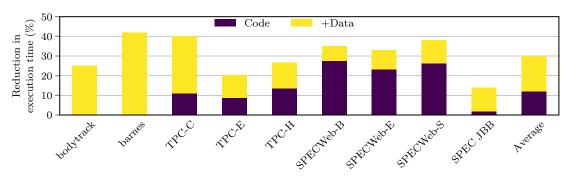

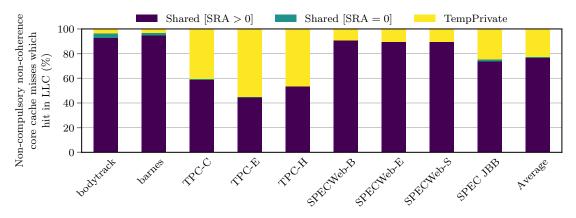

Traditionally, the private cache hierarchy in the many-core server processors treats the private and the shared blocks equally. Our private cache hierarchy design proposal is motivated by the observation that in a single-level private cache hierarchy with per-core private L1 cache, elimination of all non-compulsory non-coherence L1 cache misses to a small subset of read-shared code and data blocks can save a large fraction of the LLC accesses indicating large potential for reducing the interconnect traffic in such architectures. These read-shared code and data blocks should be protected from eviction for a longer period of time in the private cache hierarchy. We architect a specialized exclusive per-core private L2 cache which serves as a victim cache for the per-core private L1 cache. The proposed victim cache selectively accommodates a subset of the L1 cache victims and manages the victim cache contents with specialized replacement policies so that the target subset of the read-shared blocks enjoys longer residence in the private cache hierarchy. The selective victim caching and the replacement policy proposals are driven by an online partitioning of the L1 cache victims based on two distinct features, namely, an estimate of sharing degree and an indirect simple estimate of reuse distance. Our proposal learns the collective reuse probability of the blocks in each partition on-the-fly and decides the victim caching candidates based on these probability estimates. The proposed victim cache at 64 KB capacity, on average, saves 70% LLC accesses and 12.2% execution cycles compared to a baseline 128-core system that has no private L2 cache. In contrast, a traditional 128 KB non-inclusive LRU L2 cache saves only 42% LLC accesses compared to the same baseline while performing slightly worse than the proposed 64 KB victim cache. In summary, our proposal outperforms the traditional design while halving the space investment for the per-core private L2 cache.

## Acknowledgements

First and foremost, I would like to thank my supervisor, Dr. Mainak Chaudhuri, for his mentorship, dedication, and support throughout my graduate studies. Dr. Chaudhuri has not only been a constant source of excellent, technically sound advice, but also a joy to work with. He has always encouraged me to pursue my own ideas and not be scared of hard problems. Doing research with him has been immensely rewarding and a great learning experience.

I wish to express my gratitude to the Department of Computer Science and Engineering at IIT-Kanpur, where I realized that learning can be fun. Thanks especially to the late Dr. Sanjeev K. Aggarwal and Dr. Rajat Moona who introduced me to interesting problems in the area of computer systems, which eventually encouraged me to pursue research in computer architecture. I am thankful to Brajesh Mishra and Saurabh Malhotra for being amazing sysadmins and the continuous support they provided towards managing the compute nodes.

I have learned a lot from my fellow graduate students at IIT-Kanpur and would like to thank Arpita Korwar, Ashish Agarwal, Rohit Gurjar, Siddharth Rai, and Tejas Gandhi. Special thanks to Siddharth Rai, who provided numerous insights and feedback as well as infrastructure support needed for the work presented in this thesis.

On a more personal note, I would like to thank my friends, and my family for their unwavering support and encouragement. My parents, have been great role models, encouraging me to pursue a PhD at IIT-Kanpur. Thanks to these people I have been able to finish this dissertation while retaining my sanity, although I know some of them strongly disagree with this statement.

# Contents

| Li       | ist of Figures xvi |                                                 |    |

|----------|--------------------|-------------------------------------------------|----|

| 1        | Intr               | roduction                                       |    |

|          | 1.1                | Contributions                                   | 5  |

|          | 1.2                | Thesis Organization                             | 9  |

| <b>2</b> | Bac                | kground                                         | 11 |

|          | 2.1                | Multi-level Cache Hierarchy                     | 11 |

|          | 2.2                | Cache Coherence Protocols                       | 14 |

|          |                    | 2.2.1 Directory-based Cache Coherence Protocols | 16 |

|          | 2.3                | Directory Organization                          | 24 |

| 3        | Poo                | ol Directory                                    | 27 |

|          | 3.1                | Related Work                                    | 32 |

|          | 3.2                | Pool Directory                                  | 33 |

|          |                    | 3.2.1 Directory Organization                    | 34 |

|          |                    | 3.2.2 Directory Operations                      | 36 |

|          | 3.3                | Simulation Environment                          | 40 |

|          | 3.4                | Simulation Results                              | 44 |

|          |                    | 3.4.1 Sensitivity to Directory Storage Budget   | 49 |

|          | 3.5                | Summary                                         | 53 |

| 4 | Tin | y Dire  | ctory                                     | 55  |

|---|-----|---------|-------------------------------------------|-----|

|   | 4.1 | Relate  | d Work                                    | 60  |

|   | 4.2 | Simula  | ation Framework                           | 61  |

|   | 4.3 | In-LL   | C Coherence Tracking                      | 63  |

|   |     | 4.3.1   | Organization of Coherence States          | 64  |

|   |     | 4.3.2   | Coherence Protocol Extensions             | 65  |

|   |     | 4.3.3   | Performance Analysis                      | 67  |

|   | 4.4 | Tiny I  | Directory Proposal                        | 72  |

|   |     | 4.4.1   | Selective Allocation Policies             | 73  |

|   |     | 4.4.2   | Introducing Robustness: Spilling into LLC | 76  |

|   |     | 4.4.3   | Coherence Processing Latency at LLC       | 80  |

|   |     | 4.4.4   | Coherence Protocol Complexity             | 81  |

|   | 4.5 | Simula  | ation Results                             | 81  |

|   |     | 4.5.1   | Analysis of Performance                   | 84  |

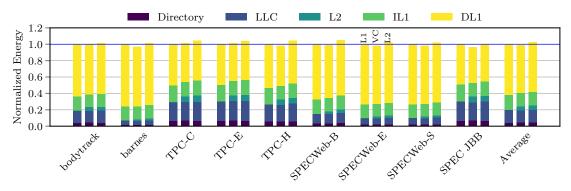

|   |     | 4.5.2   | Energy Comparison                         | 89  |

|   |     | 4.5.3   | Comparison to Related Proposals           | 90  |

|   | 4.6 | Summ    | ary                                       | 91  |

| 5 | Sha | ring-av | ware Private Caching                      | 93  |

|   | 5.1 | Chara   | cterization of Core Cache Misses          | 96  |

|   | 5.2 | Victin  | a Cache Design                            | 100 |

|   |     | 5.2.1   | Victim Caching without Selection          | 100 |

|   |     | 5.2.2   | Selective Victim Caching                  | 101 |

|   | 5.3 | Simula  | ation Environment                         | 106 |

|   | 5.4 | Simula  | ation Results                             | 109 |

|   |     | 5.4.1   | Performance Evaluation                    | 109 |

|   |     | 5.4.2   | Interconnect Traffic Comparison           | 116 |

|   |     | 5.4.3   | Iso-capacity Energy Comparison            | 116 |

|   | 5.5 | Relate  | d Work                                    | 117 |

|    | 5.6   | Summary                        | 120 |

|----|-------|--------------------------------|-----|

| 6  | Con   | clusions and Future Directions | 121 |

|    | 6.1   | Summary and Conclusions        | 121 |

|    | 6.2   | Future Directions              | 123 |

| Aj | open  | dix: List of Publications      | 125 |

| Bi | bliog | graphy                         | 127 |

# List of Figures

| 1.1 | High-level architecture of a typical single-chip multiprocessor. "SW" are         |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | interconnect switches. "DIR." is the directory storage for tracking coher-        |    |

|     | ence information. The network interface required for communicating with           |    |

|     | the neighboring chips is not shown                                                | 2  |

| 2.1 | A two-hop read transaction. $H$ represents the home L3 cache bank and its         |    |

|     | associated directory slice.                                                       | 18 |

| 2.2 | A three-hop read transaction. ${\cal H}$ represents the home L3 cache bank and    |    |

|     | its associated directory slice. SWB is the sharing writeback message              | 19 |

| 2.3 | A read-exclusive request requiring invalidations (Invals). The sharers are        |    |

|     | denoted S0, S1, S2                                                                | 21 |

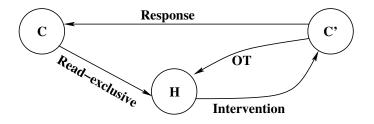

| 2.4 | A three-hop read-exclusive transaction. OT is the ownership transfer message.     | 21 |

| 3.1 | Left panel: Distribution of maximum sharer count averaged over all allo-          |    |

|     | cated directory entries in a $2 \times$ sparse directory. Right panel: Percentage |    |

|     | of directory entry bits set averaged over all allocated directory entries in a    |    |

|     | $2 \times$ full-map sparse directory.                                             | 29 |

| 3.2 | General structure of the Pool directory.                                          | 34 |

| 3.3 | Pool entries with twenty-bit wide sharer vector in a 128-core system              | 35 |

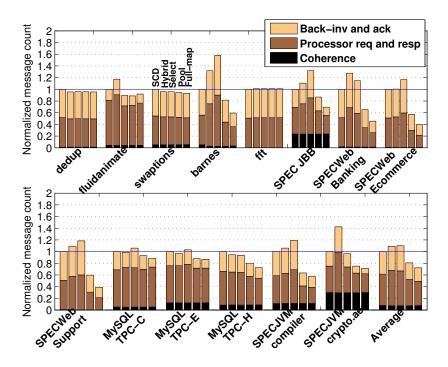

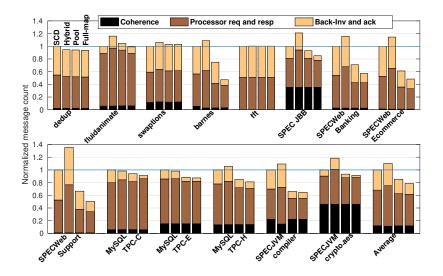

| 3.4 | Interconnect message count normalized to SCD                                      | 45 |

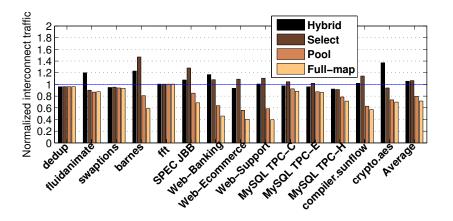

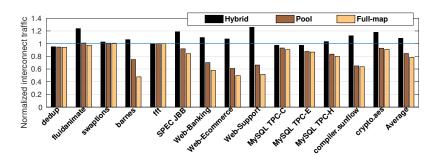

| 3.5 | Interconnect traffic normalized to SCD.                                           | 46 |

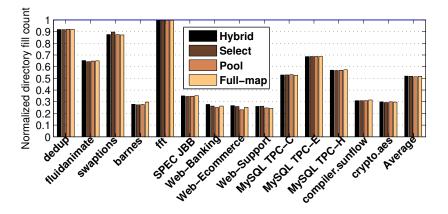

| 3.6 | Sparse directory fill count normalized to SCD                                     | 47 |

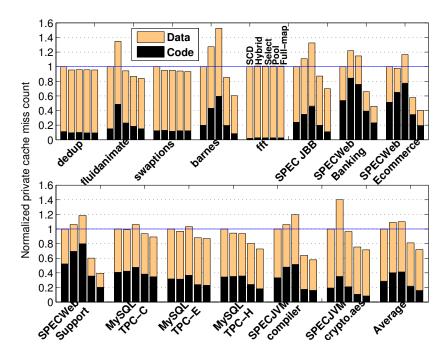

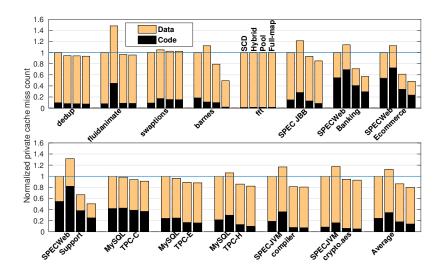

| 3.7 | Private cache miss count normalized to SCD.                                       | 48 |

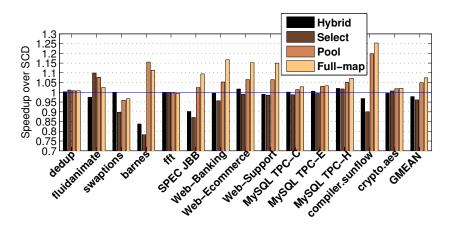

| 3.8                                                                                                                                  | Speedup over SCD                                                                                                                                    | 49                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 3.9                                                                                                                                  | Interconnect message count normalized to SCD for $\frac{1}{8} \times$ directory                                                                     | 51                                                                                                                     |

| 3.10                                                                                                                                 | Interconnect traffic normalized to SCD for $\frac{1}{8} \times$ directory                                                                           | 52                                                                                                                     |

| 3.11                                                                                                                                 | Sparse directory fill count normalized to SCD for $\frac{1}{8} \times$ directory                                                                    | 52                                                                                                                     |

| 3.12                                                                                                                                 | Private cache miss count normalized to SCD for $\frac{1}{8} \times$ directory                                                                       | 53                                                                                                                     |

| 3.13                                                                                                                                 | Speedup over SCD for $\frac{1}{8} \times$ directory.                                                                                                | 53                                                                                                                     |

| 4.1                                                                                                                                  | Performance with $\frac{1}{4}$ ×, $\frac{1}{8}$ ×, and $\frac{1}{16}$ × sparse directories normalized to a 2×                                       |                                                                                                                        |

| 1.1                                                                                                                                  | directory. $\ldots$                                                | 56                                                                                                                     |

| 4.2                                                                                                                                  | Distribution of maximum sharer count per allocated LLC block.                                                                                       | 57                                                                                                                     |

|                                                                                                                                      | -                                                                                                                                                   | 57                                                                                                                     |

| 4.3                                                                                                                                  | Performance with $\frac{1}{16} \times$ , $\frac{1}{32} \times$ , $\frac{1}{64} \times$ , and $\frac{1}{128} \times$ sparse directories for tracking |                                                                                                                        |

|                                                                                                                                      | shared blocks only. Tracking non-shared blocks has no overhead. Results                                                                             |                                                                                                                        |

|                                                                                                                                      | are normalized to a $2 \times$ sparse directory                                                                                                     | 59                                                                                                                     |

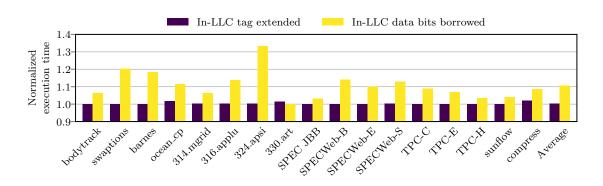

| 4.4                                                                                                                                  | Performance of in-LLC coherence tracking normalized to a $2 \times$ sparse direc-                                                                   |                                                                                                                        |

|                                                                                                                                      | tory                                                                                                                                                | 68                                                                                                                     |

|                                                                                                                                      | oorg                                                                                                                                                | 00                                                                                                                     |

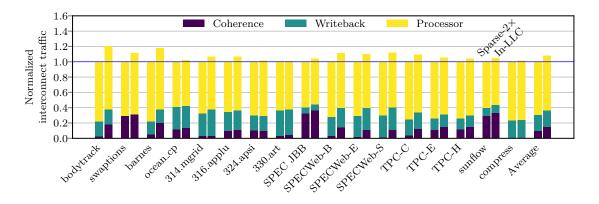

| 4.5                                                                                                                                  | Interconnect traffic for in-LLC coherence tracking normalized to a $2 \times$ sparse                                                                | 00                                                                                                                     |

| 4.5                                                                                                                                  |                                                                                                                                                     | 68                                                                                                                     |

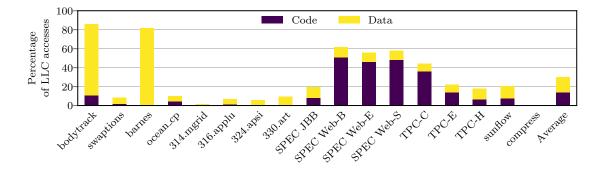

| 4.5<br>4.6                                                                                                                           | Interconnect traffic for in-LLC coherence tracking normalized to a $2\times$ sparse                                                                 |                                                                                                                        |

|                                                                                                                                      | Interconnect traffic for in-LLC coherence tracking normalized to a $2 \times$ sparse directory.                                                     | 68                                                                                                                     |

| 4.6                                                                                                                                  | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | 68<br>69                                                                                                               |

| 4.6<br>4.7                                                                                                                           | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | 68<br>69<br>70<br>71                                                                                                   |

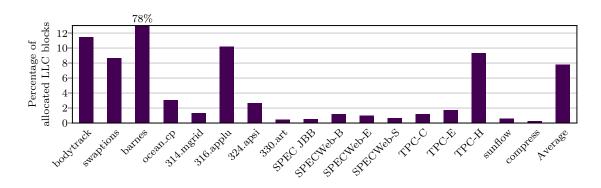

| <ul><li>4.6</li><li>4.7</li><li>4.8</li><li>4.9</li></ul>                                                                            | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | 68<br>69<br>70<br>71<br>71                                                                                             |

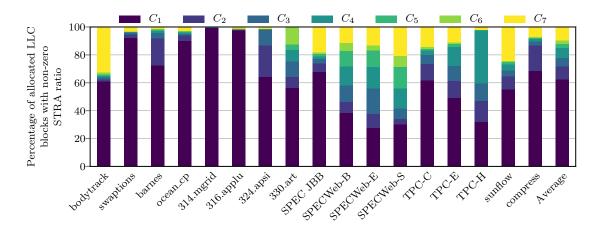

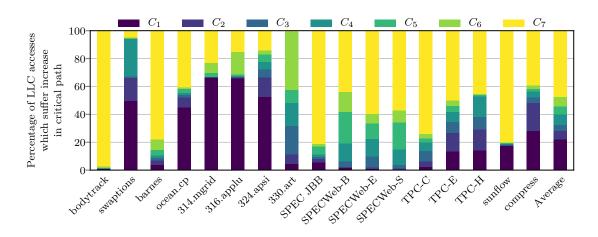

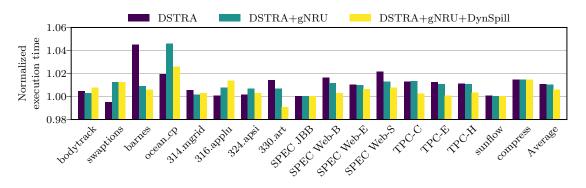

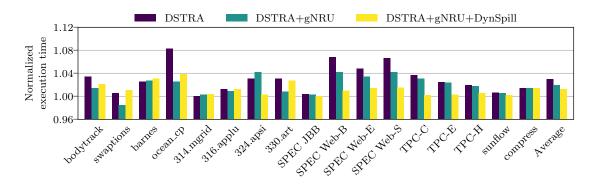

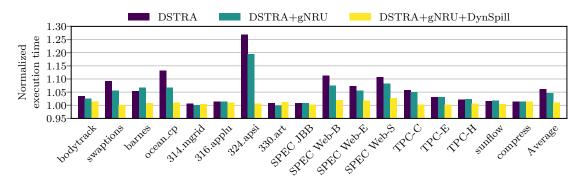

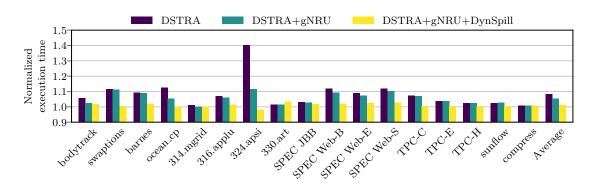

| <ul> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> </ul>                                                         | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse<br>directory                                                           | <ul> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>82</li> </ul>                                     |

| <ul> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> </ul>                                           | Interconnect traffic for in-LLC coherence tracking normalized to a $2 \times$ sparse directory                                                      | 68<br>69<br>70<br>71<br>71<br>82<br>83                                                                                 |

| <ol> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> </ol>                             | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | <ul> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>82</li> <li>83</li> <li>84</li> </ul>             |

| <ol> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> </ol>               | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | <ol> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>82</li> <li>83</li> <li>84</li> <li>84</li> </ol> |

| <ol> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> </ol>               | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | <ol> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>82</li> <li>83</li> <li>84</li> <li>84</li> </ol> |

| <ol> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> </ol> | Interconnect traffic for in-LLC coherence tracking normalized to a 2× sparse directory                                                              | <ol> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>82</li> <li>83</li> <li>84</li> <li>84</li> </ol> |

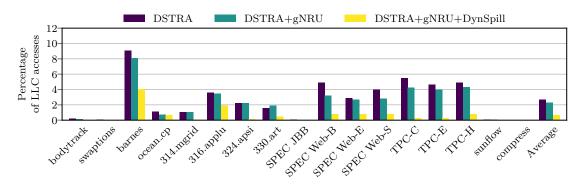

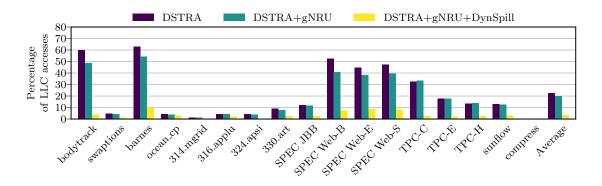

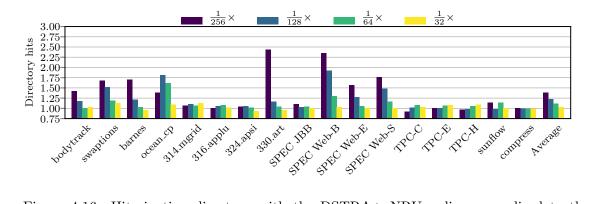

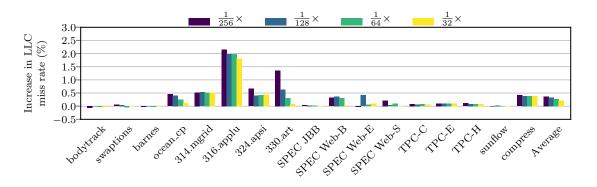

| 4.16 | Hits in tiny directory with the DSTRA+gNRU policy normalized to the                                                                                               |           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|      | DSTRA policy.                                                                                                                                                     | 86        |

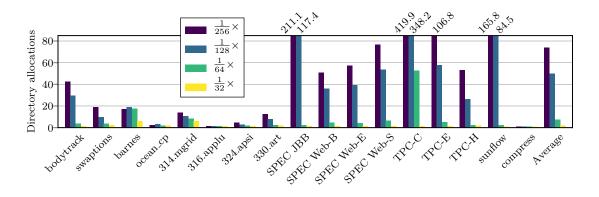

| 4.17 | Allocations in tiny directory with the DSTRA+gNRU policy normalized to                                                                                            |           |

|      | the DSTRA policy.                                                                                                                                                 | 87        |

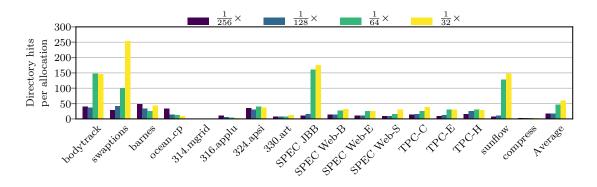

| 4.18 | Hits per allocation in tiny directory with the DSTRA+gNRU policy                                                                                                  | 87        |

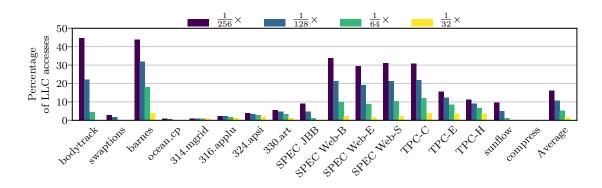

| 4.19 | Percentage of LLC accesses which are able to avoid increase in critical path                                                                                      |           |

|      | because of spilled directory entries in the LLC when using the $DSTRA+gNRU+gNRU+gNRU+gNRU+gNRU+gNRU+gNRU+gNRU$                                                    | -DynSpill |

|      | policy                                                                                                                                                            | 88        |

| 4.20 | Increase in LLC miss rate due to spilling when using DSTRA+gNRU+DynSpill                                                                                          |           |

|      | policy compared to a $2 \times$ sparse directory                                                                                                                  | 89        |

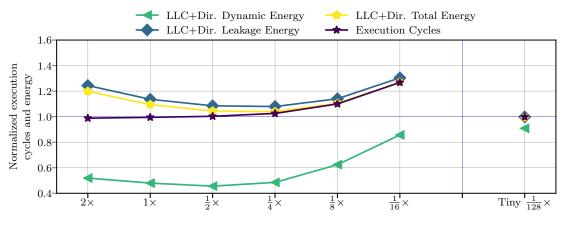

| 4.21 | Execution cycles and energy normalized to the $\frac{1}{256} \times$ tiny directory exercis-                                                                      |           |

|      | ing the DSTRA+gNRU+DynSpill policy.                                                                                                                               | 90        |

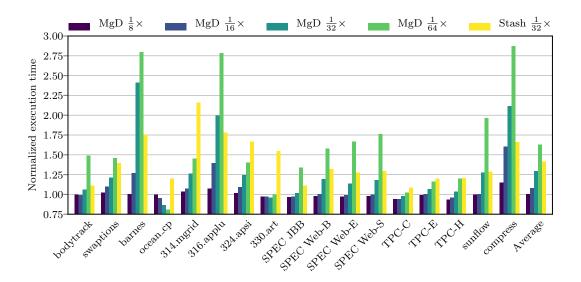

| 4.22 | Performance of $\frac{1}{8} \times$ , $\frac{1}{16} \times$ , $\frac{1}{32} \times$ , $\frac{1}{64} \times$ multi-grain directory (MgD) and $\frac{1}{32} \times$ |           |

|      | Stash directory normalized to a sparse $2 \times$ directory                                                                                                       | 92        |

| 5.1  | Non-compulsory non-coherence core cache misses that hit in LLC                                                                                                    | 95        |

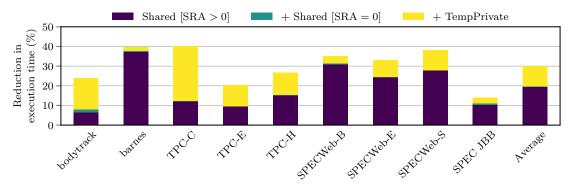

| 5.2  | Execution time saved when non-compulsory non-coherence core cache misses                                                                                          |           |

|      | that hit in the LLC are treated as core cache hits.                                                                                                               | 95        |

| 5.3  | Distribution of non-compulsory non-coherence core cache misses that hit in                                                                                        |           |

|      | LLC based on the sharing types of the LLC blocks being accessed                                                                                                   | 97        |

| 5.4  | Execution time saved when non-compulsory non-coherence core cache misses                                                                                          |           |

|      | that hit in the LLC are treated as core cache hits.                                                                                                               | 98        |

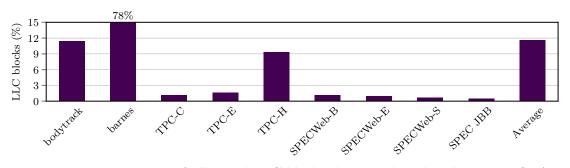

| 5.5  | Percentage of allocated LLC blocks that are shared with positive SRA                                                                                              | 98        |

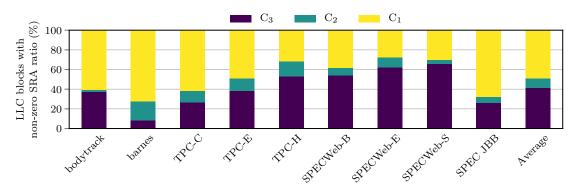

| 5.6  | Distribution of the shared LLC blocks into the SRA ratio categories                                                                                               | 99        |

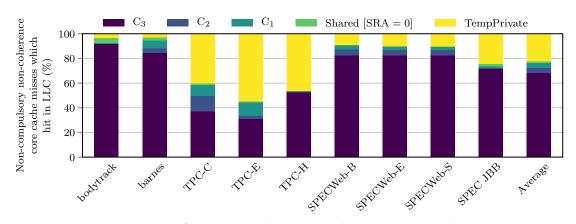

| 5.7  | Distribution of non-compulsory non-coherence core cache misses that hit in                                                                                        |           |

|      | LLC based on the sharing status of the LLC block being accessed                                                                                                   | 99        |

| 5.8  | Execution time saved when non-compulsory non-coherence core cache misses                                                                                          |           |

| -    | that hit in the LLC are treated as core cache hits.                                                                                                               | 100       |

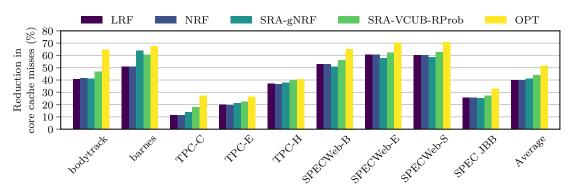

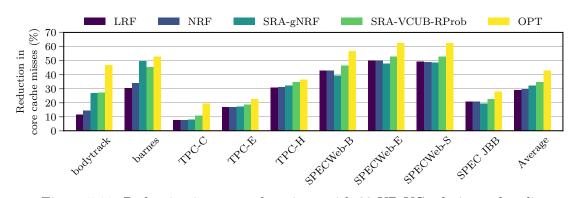

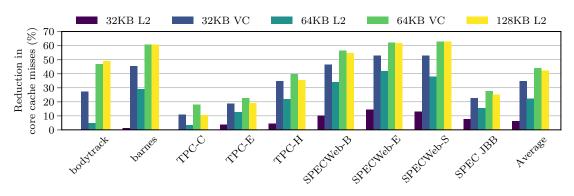

| 5.9  | Reduction in core cache misses with 64 KB VC relative to baseline                                                                                                 |           |

| 5.9  | Reduction in core cache misses with 64 KB VC relative to baseline                                                                                                 | 110       |

xvii

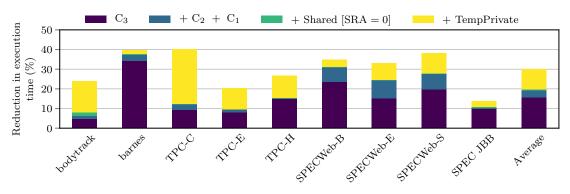

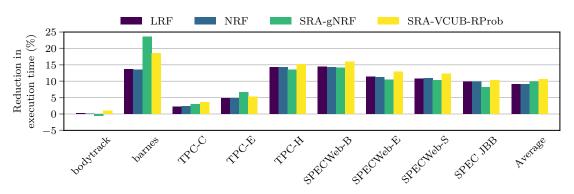

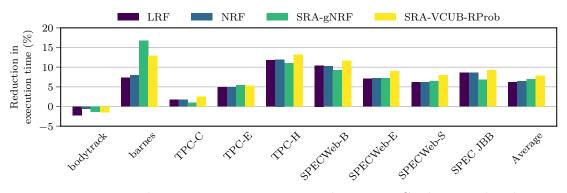

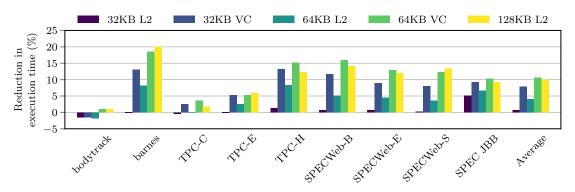

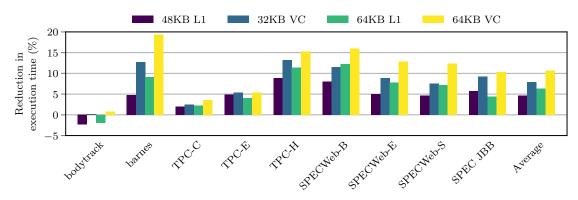

| 5.10 Reduction in execution time with 64 KB VC relative to baseline 110     |

|-----------------------------------------------------------------------------|

| 5.11 Reduction in core cache misses with 32 KB VC relative to baseline 110  |

| 5.12 Reduction in execution time with 32 KB VC relative to baseline 111     |

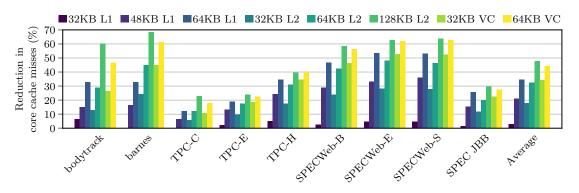

| 5.13 Comparison between traditional non-inclusive L2 cache and SRA-VCUB-    |

| RProb-VC in terms of reduction in core cache misses                         |

| 5.14 Comparison between traditional non-inclusive L2 cache and SRA-VCUB-    |

| RProb-VC in terms of reduction in execution time                            |

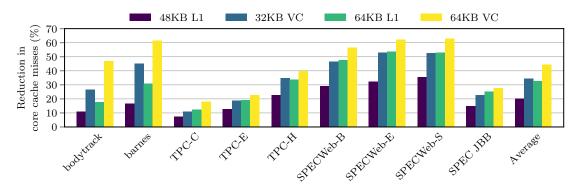

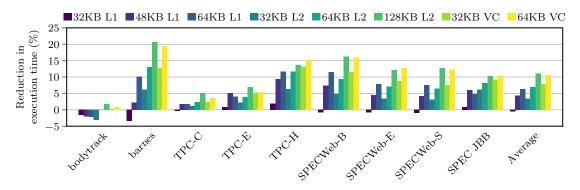

| 5.15 Comparison between iso-capacity L1-only baselines and the SRA-VCUB-    |

| RProb-VC configurations in terms of reduction in core cache misses 113      |

| 5.16 Comparison between iso-capacity L1-only baselines and the SRA-VCUB-    |

| RProb-VC configurations in terms of reduction in execution time 113         |

| 5.17 Comparison of core cache miss savings between the SRA-VCUB-RProb-      |

| VC design and single-level and two-level private hierarchy configurations   |

| enhanced with the SHiP policy                                               |

| 5.18 Comparison of execution time savings between the SRA-VCUB-RProb-VC     |

| design and single-level and two-level private hierarchy configurations en-  |

| hanced with the SHiP policy                                                 |

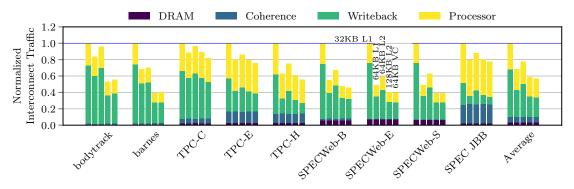

| 5.19 Interconnect traffic for private cache hierarchy configurations        |

| 5.20 Total energy expended by the cache hierarchy for various private cache |

| hierarchy configurations with a per core private cache hierarchy budget of  |

| 128 KB                                                                      |

## Chapter 1

## Introduction

The workloads that typically run on general-purpose processors can be largely divided into two categories, namely client workloads and server workloads. The server workloads are multi-threaded or multi-process in nature where the threads or the processes carry out different types of work such as thread/process pool management, allocation of software resources (memory, buffer, etc.), compute, input/output (I/O), book-keeping/statistics collection, etc.. As a result, the server workloads demand high levels of concurrency and some guarantee on response time bound. To cater to this demand, during the past decade, high-end server-grade single-chip multiprocessors (CMPs) have sported an increasing number of high-performance independent processor cores along with a deep on-chip cache hierarchy. While the cache hierarchy and the highly-optimized core microarchitecture help achieve good single-thread performance, the large number of on-chip cores allow many threads to run concurrently achieving high levels of throughput. Such CMPs with large core counts are often referred to as many-core processors.

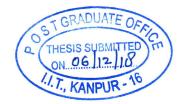

Figure 1.1 shows the high-level components of a typical single-chip multiprocessor. The chip has six cores numbered C0 to C5. Each core has an instruction processing pipeline optimized for single-thread performance. The pipeline interfaces with the per-core private L1 instruction (iL1) and L1 data (dL1) caches for fetching code and data. The L1 cache misses are forwarded to the per-core unified L2 cache. The L2 cache of each core connects to an interconnection network switch. The L3 cache is the last-level cache (LLC), shared by all cores, and is architected as a collection of banks. Each core has a local L3 cache bank connected to its switch, while accessing the other remote L3 cache banks requires a traversal through the interconnection network. The interconnection network may have a few switches dedicated for connecting the memory controllers. While the L2 cache misses are forwarded to the appropriate L3 cache bank derived from the physical address, the L3 cache misses are forwarded to the appropriate memory controller based on the physical address. Each memory controller may have single or multiple channels connecting usually to DDRx DRAM modules. All the switches are connected according to some topology to form an interconnection network [43]. The typical topologies include ring, mesh, and torus. The connections put restriction on the possible routes between two switches leading to lower overall bandwidth. Each switch contains virtual channels or queues to improve routing throughput and avoid routing deadlocks. The virtual channels can be multiplexed on a smaller number of physical networks.

Figure 1.1: High-level architecture of a typical single-chip multiprocessor. "SW" are interconnect switches. "DIR." is the directory storage for tracking coherence information. The network interface required for communicating with the neighboring chips is not shown.

The shared memory programming model is very popular in the multi-threaded server

workloads. Its popularity primarily stems from the ease of programming enabled by the communication abstraction provided by the load/store interface. A thread can produce a new value to a shared variable through a traditional store instruction and another thread can eventually see this value by simply loading the shared variable. For this programming model to work correctly, certain ordering constraints may have to be imposed on a set of operations involving the shared variables. This is usually achieved through explicit synchronization operations in the application software. For the shared memory abstraction along with the synchronization operations to work correctly, the underlying hardware must ensure that the stores to a particular address eventually become visible to all cores in the system (known as write propagation) and that all cores in the system see the stores to a particular address in exactly the same order (known as write serialization). Write propagation and write serialization together form what is popularly known as cache coherence [25, 36, 75]. Simply put, the cache coherence hardware keeps the contents of the private caches across the cores coherent. For the cache coherence hardware to scale efficiently to a large number of cores, it is necessary to systematically avoid broadcast of any information to all cores. This requirement necessitates maintaining additional storage structures for keeping track of the location of copies of cache blocks in the entire chip. This coherence tracking information can enable the hardware to quickly locate the copies of a cache block whenever needed. For example, when a core does a store to a cache block, it may be necessary to invalidate all copies of the cache block residing in the other cores' private caches to maintain coherence. This coherence tracking storage is usually referred to as the coherence directory [14]. Further, since the directory maintains information about only a subset of the memory blocks in the system, it is referred to as the sparse directory keeping track of a sparse sampling of all the memory blocks [35, 66, 81]. The sparse directory is architected by decomposing it into slices and associating a slice with each L3 cache bank, as shown in Figure 1.1. The directory slice attached to an L3 cache bank is responsible for keeping track of the copies of all blocks mapped to that L3 cache bank. This directory slice or the associated L3 cache bank is referred to as the home directory slice or the home L3 cache bank of all these blocks. Each entry of the directory slice maintains information about one cache block. Two types of directory entry encoding have been widely used. In one type, a directory entry is represented as a vector of bits where each bit encodes either a sharer or a cluster of sharers. The width of such a bitvector entry is necessarily equal to either the maximum number of cores or the maximum number of core clusters. In the other type of encoding, a directory entry is represented as a collection of pointers where each pointer encodes the identity of a sharer. The width of such a limited pointer entry is equal to  $p(\lceil \log_2 C \rceil + 1)$  where p is the number of pointers in the directory entry and C is the number of cores in the CMP. Each pointer needs a valid bit and space to encode the identity of a sharer. In addition to the sharer encoding, each directory entry maintains the coherence states of a block.

Two important problems arise as the number of cores of a cache-coherent CMP is scaled from a few tens of cores to 100+ cores. The first problem relates to the efficient support for shared memory programming model. The legacy shared memory workloads must continue to run efficiently and hence, the entire hardware substrate for cache coherence must scale gracefully [62]. However, since the coherence directory is responsible for keeping track of the copies of the blocks in the private caches, the number of directory entries must be scaled up accordingly to take into account the increasing aggregate private cache capacity with core count. An under-provisioned directory curtails the number of blocks that can be cached simultaneously in the private cache hierarchy hampering performance. Also, the average number of directory storage bits devoted to keep track of the copies of a block must be scaled up with core count because with a larger number of cores, the number of possible copies of a block inside the chip increases. This aspect usually impacts the width of a directory entry. A less than adequately sized directory entry would restrict the degree of sharing and may hamper performance. In this thesis, we study novel optimizations that target the directory width as well as the directory height for 100+ core CMPs.

The second problem relates to managing the communication traffic in the on-chip interconnection network of a large many-core processor. Given the large working sets of the server workloads, the communication traffic in the interconnect between the private cache hierarchy and the shared L3 cache banks is usually large. Additionally, as the scale of the chip increases, the average round-trip latency through the interconnect also grows. Therefore, it is important to optimize the design to reduce this traffic. The coherence directory organization and the efficiency of the private cache hierarchy together dictate the shape and volume of this traffic. While our directory optimization proposals show significant savings in the interconnect traffic, we also study the design of an efficient private cache hierarchy in the context of the server workloads. Our private cache hierarchy proposal takes into account the nature of code and data sharing between the cores and designs a space-efficient architecture that decides which blocks to keep longer in the private cache hierarchy.

In the following two sections, we outline the contributions of this thesis (Section 1.1) and its organization (Section 1.2).

#### **1.1** Contributions

This thesis makes three specific contributions addressing the two scalability problems discussed above. The first contribution is a width-optimized novel two-level directory organization. The proposed organization attempts to optimize the average number of bits devoted to a directory entry. Our proposal exploits the well-known observation that a shared block exhibits a bi-modal pattern in the number of sharers i.e., a block is either shared by a few threads or widely shared [25, 81]. As a result, multi-threaded applications typically require two types of directory entries, namely, limited pointer entries tracking a few sharers of a block and bitvector entries tracking larger number of sharers for widely shared blocks. The primary challenge in designing a directory that has these two kinds of entries is that the exact proportion of these two types of entries varies across applications and across phases even within the same application. Recent proposals aiming to optimize the average number of bits per directory entry have organized the directory as either a static mix of these two types of entries with a pre-defined proportion or a collection of relatively short bitvector entries that can encode either a limited number of sharer pointers or a larger number of sharers hierarchically [27, 69, 85]. In either case, directory

space is wasted depending on the run-time characteristics of the application. We present a directory organization that enables on-demand allocation of the two different types of directory entries dynamically. Our design maintains a pool of limited pointer entries, where each entry can also double as a segment directory entry encoding the sharers in a cluster of cores. Each entry in the primary directory array has a pointer that can either represent a sharer or point to an entry in the pool. As a result, one entry of the primary directory array is enough for tracking a private block. A moderately shared block would require a pool entry. When multiple segment directory entries are needed to encode all the sharers of a block, our pool management protocol guarantees that all these pool entries are allocated contiguously so that maintaining a pointer to the head entry is enough. We study the performance of this proposal using detailed simulation of a 128-core CMP running multi-threaded applications drawn from scientific, general-purpose, and commercial computing domains. Our Pool Directory proposal offers, on average, 5% improvement in performance and 20% savings in interconnect traffic compared to the stateof-the-art scalable coherence directory (SCD) proposal using an equally sized directory. The details of the Pool Directory design, its evaluation, and comparison with related literature are presented in Chapter 3.

The second contribution is a height-optimized directory organization. The proposed organization seeks to design a directory that has a minimal number of entries. Recent notable research efforts for optimizing the directory height have largely followed two directions. First, it has been observed that large coarse-grain contiguous memory regions are often private in server workloads [13]. Each private coarse-grain region can be tracked using a single directory entry. This optimization, however, requires support for multi-grain coherence so that fine-grain shared blocks can also be tracked by the directory [5, 10, 86]. Second, pages or blocks that are temporarily private can be identified dynamically respectively by the operating system (OS) or the hardware. The blocks thus marked private are not tracked by the directory saving directory entries. However, if and when such a block is shared at a later point, a costly non-scalable broadcast-based recovery mechanism is needed because no information about the locations of these blocks is available [24, 26]. Such broadcast-based schemes are very difficult to scale to 100+ cores. In this thesis, we design a robust minimally-sized directory that can offer adequate performance while the accompanying coherence protocol can enjoy the simplicity, scalability, and OS-independence of the traditional broadcast-free block-grain coherence protocols. We begin our exploration with a naïve design that does not have a directory at all and the location/sharers of a block are tracked by borrowing a portion of the block's L3 cache data way. Such a design, however, lengthens the critical path from two transactions to three transactions (two hops to three hops) for the blocks that experience frequent shared read accesses. This is because the L3 cache data way cannot provide the block in such cases (which the baseline can); part of the L3 cache block is corrupted with tracking information. We address this problem by architecting a tiny directory that dynamically identifies and tracks a selected subset of the blocks that experience a large volume of shared accesses. However, it is difficult to appropriately size this tiny directory, since the actual footprint of the shared blocks varies across applications and across phases even within the same application. Therefore, to make the design robust, we further augment the tiny directory proposal with an option of selectively spilling directory entries into the L3 cache space. The spill selection mechanism gives priority to the tracking information of the shared blocks that are critical and cannot be accommodated by the tiny directory. Our Tiny Directory proposal operating with under 200 KB of storage budget offers performance within a percentage of a traditional directory with 8 MB storage in a 128-core system. The Tiny Directory design outperforms the state-of-the-art by very large margins when operating with the same number of directory entries. The Tiny Directory design, its evaluation, and comparison with recent related works are discussed in Chapter 4.

The third contribution is a space-efficient private cache hierarchy design for many-core server processors. Traditionally, the private and the shared blocks are treated equally by the private cache hierarchy. We start our exploration with a single-level private cache hierarchy having a per-core private L1 cache and augment it with an intelligent L2 cache. We observe that in a single-level private cache hierarchy with per-core private L1 cache, elimination of all non-compulsory non-coherence L1 cache misses to a small subset of readshared code and data blocks can save a large fraction of the L3 cache accesses indicating large potential for reducing the interconnect traffic in such architectures. These readshared code and data blocks should be protected for a longer period of time in the private cache hierarchy. We architect a specialized exclusive per-core private L2 cache which serves as a victim cache for the per-core private L1 cache. The goal of the proposed victim cache is to lengthen the residency of the target subset of the read-shared blocks in the private cache hierarchy. The proposed victim cache selectively accommodates a subset of the L1 cache victims and manages the victim cache contents with specialized replacement policies. The selective victim caching and the replacement policy proposals are driven by an online partitioning of the L1 cache victims based on two distinct features, namely an estimate of sharing degree and an indirect simple estimate of reuse distance. Our proposal learns the collective reuse probability of the blocks in each partition onthe-fly and decides the victim caching candidates based on these probability estimates. The proposed victim cache at 64 KB capacity, on average, saves 70% L3 cache accesses and 12.2% execution cycles compared to a baseline 128-core system that has no private L2 cache. In contrast, a traditional 128 KB non-inclusive LRU L2 cache saves only 42%L3 cache accesses compared to the same baseline while performing slightly worse than the proposed 64 KB victim cache. In summary, our proposal outperforms the traditional design while halving the space investment for the per-core private L2 cache. The private cache hierarchy design and its detailed evaluation are presented in Chapter 5.

We summarize our contributions in the following.

- We propose a width-optimized two-level Pool Directory organization that dynamically allocates two types of directory entries from a unified pool of short-vector directory entries.

- We propose a height-optimized Tiny Directory organization that keeps track of a critical subset of shared blocks in the directory and keeps the tracking information of the rest of the blocks in the L3 cache space.

- We propose a space-efficient sharing-aware private cache hierarchy suitable for server

workloads. The private cache hierarchy is designed to have a traditional L1 cache and a specialized victim L2 cache that selectively caches a subset of critical read-shared blocks.

**Thesis Statement:** The thesis addresses the scalability bottlenecks posed by the coherence tracking overhead and the latency/bandwidth overhead of the interconnect in a server processor with 100+ cores. The over-arching goal of the thesis is to design (i) a spaceefficient coherence tracking infrastructure that can lower the coherence directory overhead while maintaining/improving performance and (ii) a space-efficient private caching architecture that can lower the overall number of trips to the shared last-level cache. The thesis demonstrates its success in achieving these goals through detailed simulation results on a 128-core chip-multiprocessor.

#### 1.2 Thesis Organization

Chapter 2 introduces the background material on cache hierarchy, cache coherence, and directory organization relevant to our contributions. Chapters 3, 4, and 5 present the detailed proposal and evaluation of Pool Directory, Tiny Directory, and space-efficient private cache hierarchy design, respectively. Each chapter also includes a discussion of the related literature relevant to each proposal. Chapter 6 concludes the thesis with a discussion of possible future avenues of research relevant to the domain of our contributions.

### Chapter 2

## Background

We have introduced the readers to the basic many-core processor architecture and the notion of cache coherence in Chapter 1. In this chapter, we discuss three components of the processor microarchitecture in more detail, as these have direct relevance to the contributions of this thesis. Section 2.1 discusses the protocols for maintaining a multi-level cache hierarchy. Section 2.2 presents different types of cache coherence protocols and the basics of composing such protocols. As we have mentioned in Chapter 1, the directory storage is at the center of the scalable cache coherence hardware. We discuss some of the details of directory organization in Section 2.3.

#### 2.1 Multi-level Cache Hierarchy

An on-chip multi-level cache hierarchy is common in today's processors. A cache hierarchy is organized as a collection of levels of caches. The cache levels get bigger and slower as they get further away from the core computing pipeline. Such a design is motivated by the fact that the most recently used code and data subset should reside close to the computing pipeline and be accessible with low latency. As a result, when an access to a cache level n fails to find the requested code or data, it is fetched from the outer levels of the cache hierarchy and usually allocated in level n, unless it can be ascertained with high confidence that the fetched block of code or data will not be accessed from the level n cache in nearfuture. In this thesis, we will assume that a block fetched to a particular level of the cache hierarchy is always allocated in that level, unless explicitly mentioned otherwise. Different cache hierarchy designs implement different types of relationships between the contents of the levels of the hierarchy and these relationships are of importance to us for this thesis. In the following discussion, we will first assume a two-level cache hierarchy with the levels denoted by L1 and L2. Next, we will extend the discussion to a three-level cache hierarchy by introducing the L3 cache.

In a two-level cache hierarchy, depending on the cache management policies, the L1 cache contents may or may not be a subset of the L2 cache contents. If the L1 cache contents are always a subset of the L2 cache contents, the L2 cache is said to be inclusive of the L1 cache. To maintain the inclusion invariant, the following two aspects of the cache management policy must be strictly observed. First, a block allocated in the L1 cache as a result of an L1 cache miss needs to be resident in the L2 cache as well. This implies that when a block is fetched from outer levels of the memory hierarchy, it is allocated in both L1 and L2 caches. Second, when a block is evicted from the L2 cache, in addition to querying the L1 cache for any up-to-date dirty copy, the L1 cache copy must also be invalidated. These invalidation messages are usually referred to as back-invalidation messages. If the L1 cache contents are not a subset of the L2 cache contents, the L2 cache is said to be non-inclusive of the L1 cache. A special case of a non-inclusive L2 cache is an exclusive L2 cache where the intersection between the L1 cache contents and the L2 cache contents is always empty. To maintain the exclusion invariant, a block allocated in the L1 cache must not be resident in the L2 cache or a block allocated in the L2 cache must not be resident in the L1 cache. This requirement implies the following. First, a block fetched from the outer levels of the memory hierarchy due to a miss in the L1 and L2 caches is allocated only in the L1 cache. Second, a block evicted from the L1 cache may be allocated in the L2 cache. Third, a block fetched to the L1 cache from the L2 cache due to an L1 cache miss is allocated in the L1 cache and invalidated from the L2 cache. Fourth, a block evicted from the L2 cache does not have to invalidate any L1 cache copy, thereby eliminating back-invalidations. The remaining spectrum of non-inclusive L2

cache designs is often referred to as non-inclusive/non-exclusive (NINE) to make it clear that it is neither inclusive nor exclusive. One popular NINE L2 cache design maintains inclusion all the time except after a block is evicted from the L2 cache. In such a design, a block fetched from outer levels of the memory hierarchy is allocated in both L1 and L2 caches. When a block is evicted from the L2 cache, its copy, if any, is not invalidated from the L1 cache. If an L1 cache eviction misses in the L2 cache, it may be allocated in the L2 cache. In this thesis, any NINE design will follow this protocol.

A two-level cache hierarchy with an exclusive L2 cache enjoys more aggregate cache capacity than one with an inclusive or a NINE L2 cache. This is because in an exclusive cache hierarchy, there is no replication of data across the levels of the cache hierarchy. Further, the back-invalidations in an inclusive design can forcefully evict live L1 cache blocks leading to loss in performance. These are usually referred to as inclusion victims. The exclusive and NINE designs do not suffer from this problem. To keep the volume of inclusion victims low, typically a 4:1 or 8:1 capacity ratio is recommended between the L2 and L1 caches of an inclusive cache hierarchy. As this capacity ratio increases, the probability that an L2 cache victim will find a copy in the L1 cache gradually drops.

The discussion presented so far can be seamlessly extended to a three-level hierarchy, which we use in this thesis. The L3 cache contents can be inclusive, exclusive, or non-inclusive/non-exclusive with respect to the union of the L1 and L2 cache contents. If the L2 cache is inclusive of the L1 cache, this union is same as the L2 cache contents. In this thesis, we will use a NINE L2 cache and a NINE L3 cache design. After eviction of a block from the L3 cache, its copy may continue to reside in the L1 cache or the L2 cache or both. This model of inclusion, exclusion, and NINE can also be extended to a setting with multiple cores. In this thesis, we will use a model where the L1 and L2 caches are private to a core, while the L3 cache is shared among all the cores. In such a NINE L3 cache design, after eviction of a block from the L3 cache or the L2 cache or both in multiple copies of it may continue to reside in the L1 cache or the L2 cache

#### 2.2 Cache Coherence Protocols

Cache coherence helps offer the single shared address space abstraction to the programmers in a many-core system having multiple private caches. To provide programmers the view of a coherent shared memory across all the cores, CMPs implement cache coherence protocols. These protocols keep the multiple private caches of a CMP coherent by enforcing the Single-Writer Multiple-Reader (SWMR) invariant [75]. The SWMR invariant requires that for any memory location, at any given moment in time, there is either a single core that may write to it (and may also read it) or some number of cores that may read from it. A cache coherence protocol is a collection of actions that take the responsibility of propagating and serializing the stores to a particular address. The actions depend on the type of the operation e.g., a load or a read miss from a core's private cache hierarchy, a store or a write miss from a core's private cache hierarchy, or an eviction coming out of a core's private cache hierarchy. An operation completed within the confines of the private cache hierarchy of a core does not require any action from the cache coherence hardware. To implement the appropriate actions, a coherence protocol maintains the state of every cache block residing inside the private cache hierarchy. The nature of the actions also depends on the state of the block involved in the operation.

Typical cache block states are invalid (I), shared (S), clean exclusive (E), modified (M), and owned (O). A block is in invalid state with respect to a particular level of the cache hierarchy of a core if it is not present in that level of the cache hierarchy. A block is cached in shared state in a particular level of the cache hierarchy of a core if it is not modified and the core needs coherence protocol's "permission" to modify it. The core has permission to read the block. Other cores can also have copies of the block in shared state in their private caches. A block is in clean exclusive state in a particular level of the cache hierarchy of a core if it is not modified and the core has permission to read as well as modify the block. No other core can have a copy of the block in its private cache hierarchy. A block is in modified state in a particular level of the cache hierarchy of a core if parts of the block have been modified. The core has permission to read from and write to the block. A block is in owned state in a particular level of the cache hierarchy of a core if the block has been modified and the core does not have permission to modify the block. The core can read the block. No other core can have the block in E, M, or O state. Other cores can have copies of the block in shared state in their private caches. The eviction of an O state block from the private cache hierarchy of a core generates a writeback to the next level of the memory hierarchy. A coherence protocol implementation may not support all the five states. Based on the set of supported states, MESI and MOESI are the two very popular coherence protocols.

The coherence protocol actions are triggered in response to a request coming out of the private cache hierarchy of a core. To trigger the appropriate action, knowledge about the current state of the requested block in the private caches of other cores is necessary. There are two possible techniques to gather this information. In the first technique, the request is broadcast to all cores. The private caches of each core "snoop" the request and act depending on the state of the requested block in its private cache hierarchy. These broadcast-based snoopy protocol implementations demand significant interconnect bandwidth and usually considered impractical beyond a few tens of cores.

In the second technique, as mentioned in Chapter 1, a dedicated piece of storage, known as the coherence directory, is maintained for tracking locations and state of each block resident in the private caches of the cores. The locations encode the id's of the cores that have copies of the block in their private caches. Depending on the requested block address, the request is first sent to the home L3 cache bank where it consults the home directory slice (the concept home was introduced in Chapter 1). The directory offers the current locations of the copies of the block and indicates the coherence state of the block. The coherence state can be S, M, or O depending on the supported set of states. A coherence state of S indicates that the block is in shared state and the rest of the directory entry provides the identities of the sharers (there could be only one sharer also). A coherence state of M indicates that the block is in modified state and the rest of the directory entry encodes the identity of the core where the modified block can be found. A coherence state of O indicates that the block is in O state in the private cache hierarchy of a core. In this case, the rest of the directory entry encodes the identity of the owner core and the identities of the other sharers of the block. A coherence state of I is unnecessary because a block that is not resident in the private cache hierarchy of any core is not tracked in the directory. The directory is a tagged structure and the tags of only those blocks which are cached in the private cache hierarchy of the cores are found in the directory. A coherence state of E is not maintained in the directory and a block in E state in some core's private cache hierarchy is tracked in M state in the directory. This is because the core having the block in E state can silently modify the block and take the block to M state without notifying the home directory slice.

Once the locations and the state of a requested block are obtained from the directory, point-to-point unicast messages are sent to only the cores having copies of the requested block. Only these cores act upon the forwarded request. Since a request is always forwarded to the home directory slice first before any coherence action is triggered, the directory also serves as a serialization point for multiple racing requests to a block. The directory handles these requests one at a time typically in the order of arrival (although this order has no influence on the correctness) and resolves the races with additional transient coherence states. Naturally, the directory-based coherence protocol implementations demand much less interconnect bandwidth than their broadcast-based snoopy counterparts and hold promise to scale to 100+ cores. In this thesis, we will consider only directorybased coherence protocols. We discuss the basic set of actions of such protocols in more detail in the next section.

#### 2.2.1 Directory-based Cache Coherence Protocols

As already mentioned, the exact set of coherence protocol actions depends on the request type and the current state of the requested block. In the following, we discuss the different cases for a MESI cache coherence protocol, which we use in this thesis. We assume a NINE L3 cache design. We do not assume any point-to-point message ordering between pairs of source and destination in the interconnection network. This is because different message types (e.g., request, response, intervention) for the same block between the same pair of source and destination may travel along different virtual networks inside a switch and may not maintain any ordering along the way in the most general unrestricted design of virtual network scheduling algorithms, which usually carry out an online maximum bipartite matching between the input and output ports of a switch. This is true even if all virtual networks multiplex on a single physical network. Mapping different types of messages on different virtual networks is necessary to avoid protocol deadlocks [18]. Even within the same virtual network, it is possible to reorder the messages for improving program performance e.g., it may make sense to prioritize processor miss requests over writebacks in the request network. Also, two different messages in the same virtual network between the same source and destination pair may travel along two different paths if adaptive or hot-potato routing is supported. Overall, the most general coherence protocols do not assume any ordering between network messages.

#### Read/Load miss

Suppose core C suffers from a read miss in its private cache hierarchy for a block B. The request is sent to the home L3 cache bank of B and the home directory slice is consulted in parallel with reading the L3 cache tags. The following situations may arise.

*B* is not in L3 cache and not tracked in directory: The request is forwarded to the appropriate memory controller which responds with the block after reading from DDRx DRAM. The block is allocated in the home L3 cache bank and forwarded to the private cache hierarchy of C for allocation in E state if it is a data block or in S state if it is a code block. The home directory slice allocates an entry for tracking B, marks the coherence state of the block as M or S depending on whether the block is data or code respectively, and records the identity of C in the entry.

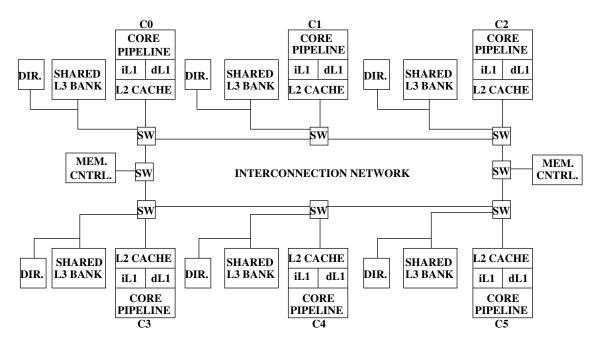

*B* is in L3 cache, but not tracked in directory: The block is read from the L3 cache and sent to the private cache hierarchy of *C* for allocation in E state if it is a data block or in S state if it is a code block. The home directory slice allocates an entry for tracking *B*, marks the coherence state of the block as M or S depending on whether the block is data or code respectively, and records the identity of *C* in the entry. This is known as a two-hop transaction because the critical path involves two messages. This is shown in Figure 2.1.

Figure 2.1: A two-hop read transaction. H represents the home L3 cache bank and its associated directory slice.

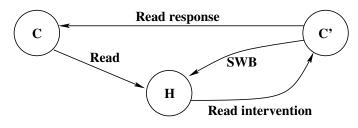

B is in L3 cache and tracked in directory: The actions depend on the coherence state of the block recorded in the directory entry. In a MESI protocol, the coherence state can be either S or M. If the state is S, the block is read from the L3 cache and sent to the private cache hierarchy of C for allocation in S state. The identity of core Cis added to the list of sharers in the directory entry. This is a two-hop transaction. On the other hand, if the coherence state is M with the identity of core C' recorded in the directory entry, the request is forwarded to core C' and the directory entry is marked busy which is a transient coherence state. This forwarded message is usually referred to as an intervention message. Core C' directly sends the requested block to core C and also sends a message (typically known as sharing writeback [25]) to the home directory slice to change the state of the directory entry to S and mark both C and C' as sharers in the directory entry. The sharing writeback message also carries a copy of the block to update the copy in the L3 cache bank so that subsequent requests for this block can be responded to by the L3 cache bank itself. The critical path involves three messages and the transaction is referred to as a three-hop transaction. This is shown in Figure 2.2. It may happen that when the forwarded intervention message arrives at core C', the requested block has already been evicted from the private cache hierarchy of core C'. To handle such late intervention races, each evicted block is allocated in an eviction buffer local to the private cache hierarchy of the core evicting the block. The block stays in the eviction buffer until the eviction is acknowledged by the home directory slice. Every eviction message received by the home directory slice is acknowledged with one of the two acknowledgment message types sent back to the evicting core. Two acknowledgment types are needed to

differentiate the situation where the home directory has forwarded an intervention from the situation where there is no such in-flight intervention message.

Figure 2.2: A three-hop read transaction. H represents the home L3 cache bank and its associated directory slice. SWB is the sharing writeback message.

*B* is not in L3 cache, but is tracked in directory: This situation can arise in a NINE L3 cache design where the L3 cache has evicted the block, but some cores still have the block in their private caches. If the coherence state of the block is M in the directory entry, an intervention message is forwarded to the core having the block and the protocol actions are similar to a regular intervention as discussed above. The only additional action is to allocate the block in the L3 cache bank when the sharing writeback message arrives. If the coherence state of the block is S in the directory entry, one of the sharers is elected to provide the block and an intervention message is forwarded to the elected sharer. The rest of the flow is same as a regular intervention discussed above, except that a copy of the block is allocated in the L3 cache so that subsequent requests can be quickly served from the L3 cache bank itself using a two-hop transaction. The late intervention races are handled with the help of the eviction buffer and eviction acknowledgment messages.

An alternative to dynamically electing a sharer as the source of the block is to maintain a "forwarding" core all the time in the directory entry. Such protocols are referred to as MESIF protocols, where there is always a core having the block in F state. The primary complication of such a protocol is that when the F state core evicts the block from its private cache hierarchy, a new forwarding core must be elected from among the existing sharers of the block by the home directory slice and notified. This requires complex handling of races where the newly elected core may also evict the block while the election is in progress in the home directory slice. We do not explore MESIF protocols in this thesis. We find that a reasonably small eviction buffer per core is sufficient for our implementation.

#### Write/Store Miss

Suppose core C suffers from a store miss in its private cache hierarchy for a block B. A store miss can take two forms depending on the state of the block B in the private cache hierarchy of C. If the block is not present in C, a read-exclusive miss is generated. On the other hand, if the block is present in C is S state, an upgrade miss is generated. The sole purpose of the upgrade miss is to seek permission from the cache coherence layer to modify the block B. In any case, the miss request is sent to the home L3 cache bank of B and the home directory slice is consulted in parallel with reading the L3 cache tags. The following situations may arise.

*B* is not in L3 cache and not tracked in directory: In this case, the miss request must be read-exclusive. The request is forwarded to the appropriate memory controller which responds with the block after reading from DDRx DRAM. The block is allocated in the home L3 cache bank and forwarded to the private cache hierarchy of C. The home directory slice allocates an entry for tracking B, marks the coherence state of the block as M, and records the identity of C in the entry.

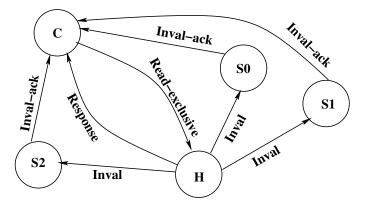

*B* is in L3 cache, but not tracked in directory: In this case also, the miss request must be read-exclusive. The block is read from the L3 cache and sent to the private cache hierarchy of C. The home directory slice allocates an entry for tracking B, marks the coherence state of the block as M, and records the identity of C in the entry.