# Facilitating Process Persistence in Hybrid Non-Volatile Memory Systems

A Thesis Submitted

in Partial Fulfilment of the Requirements

for the Degree of

Doctor of Philosophy

by

Arun KP 18111263

DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY KANPUR

## Certificate

It is certified that the work contained in this thesis entitled "Facilitating Process Persistence in Hybrid Non-Volatile Memory Systems" by Arun KP has been carried out under my supervision and that it has not been submitted elsewhere for a degree.

Dr. Debadatta Mishra

Assistant Professor

Department of Computer Science and Engineering

Indian Institute of Technology Kanpur

Dr. Biswabandan Panda

Assistant Professor

Department of Computer Science and Engineering

Indian Institute of Technology Bombay

**Declaration**

This is to certify that the thesis titled "Facilitating Process Persistence in Hybrid

Non-Volatile Memory Systems" has been authored by me. It presents the research

conducted by me under the supervision of Dr. Debadatta Mishra and Dr. Biswa-

bandan Panda.

To the best of my knowledge, it is an original work, both in terms of research content and

narrative, and has not been submitted elsewhere, in part or in full, for a degree. Further,

due credit has been attributed to the relevant state-of-the-art and collaborations with

appropriate citations and acknowledgments, in line with established norms and practices.

Arun KP

Roll No. 18111263

CSE Department

Indian Institute of Technology Kanpur

iii

### Abstract

Name of the student: Arun KP Roll No: 18111263

Degree for which submitted: PhD Department: CSE Department

Thesis title: Facilitating Process Persistence in Hybrid Non-Volatile Memory

Systems

Thesis supervisors: Dr. Debadatta Mishra and Dr. Biswabandan Panda

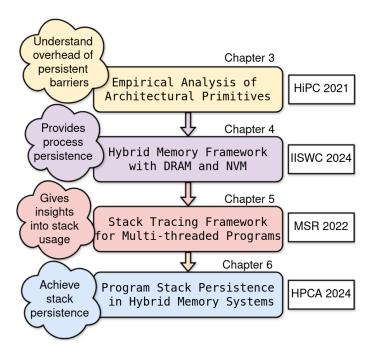

Computing systems with persistent process semantics enable applications to resume execution from a consistent state after an abrupt system restart due to a crash or power failure, saving computation time and energy. Enabling process persistence capability in systems requires storing the state of a process consisting of CPU registers, memory state, and operating system metadata in a persistent device. In this thesis, we focus on saving the state of a process in a hybrid memory system comprising Non-Volatile Memory (NVM) along with volatile DRAM. While NVM allows access through the load/store interface of a CPU, using NVM for persistence requires special care to guarantee consistent data updates in NVM. Therefore, we need mechanisms at the hardware and/or software layers to ensure a consistent memory state in NVM across reboots.

In this thesis, we first analyze the performance overhead associated with different memory persistence mechanisms for NVM on Intel x86-64 and Arm64 systems. We study the performance of conventional persistence barrier primitives to modify data reliably in NVM. We also analyze the performance of advanced mechanisms, such as logging, for memory persistence. We study performance overhead by incorporating memory persistence mechanisms in data structures widely used in modern operating systems to maintain process states. We observe that the performance overhead of different persistence techniques depends upon the nature of the data structure; for example, queue incurs the highest performance

*Abstract* v

overhead compared to other data structures across different persistence barrier primitives on Intel x86-64 and Arm64. We also observe that using memory serialization operations to enforce the order of writes to NVM contributes significantly to the performance overhead of all memory persistence mechanisms.

The design choices to persist different process states determine the performance of achieving process persistence. Thus, we need a simulation framework to study end-to-end performance trade-offs across different design choices for achieving process persistence in a hybrid memory system. As the existing simulation infrastructure requires nontrivial adaptation to incorporate hybrid memory for process persistence study, we create a hybrid memory simulation framework, *Kindle*, that supports process persistence. *Kindle* provides an end-to-end framework consisting of an operating system and a hardware simulator to enable quick prototyping of mechanisms and policies for process persistence in a hybrid memory system. Using *Kindle*, we compare the efficiency of two design choices to persistently maintain the virtual address translation of processes. We also implement prototypes of two state-of-the-art hybrid memory schemes using *Kindle* to show its capability to realize complex designs.

From the empirical analysis, we observe that the working set size and memory access patterns of applications influence the performance of memory persistence mechanisms. Among the persistent process states, the memory state is a crucial component in size and importance. Thus, the performance of the memory state persistence mechanism decides the overall performance of process persistence. The memory layout of a process consists of heap and stack areas, and they exhibit distinct usage patterns. To analyze the stack usage of different applications, we create an efficient stack tracing framework, SniP, for multi-threaded applications. SniP, with its targeted stack tracing capability, generates a trace file containing only stack access of an application, reducing the time taken to create a stack trace compared to tracing the entire memory area of a program using a state-of-the-art program tracing tool like Intel Pin and separating stack accesses from it. SniP results in  $\sim 75 \times$  reduction in trace file size for the TinyDBM key-value store application

*Abstract* vi

and up to  $\sim 24 \times$  reduction in tracing time for the Python3 HTTP server compared to Intel Pin.

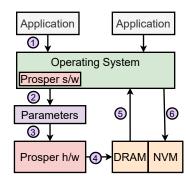

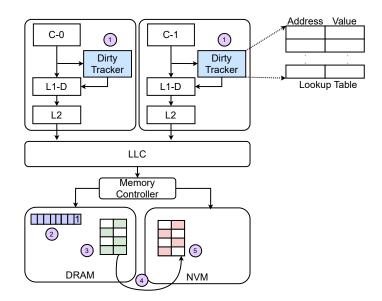

We further investigate unique properties of the program stack, such as the grow and shrink pattern of usage, presence of activation record, and indirect usage, with the help of SniP. We identify that these unique stack properties necessitate nontrivial adaptations to stateof-the-art memory persistence mechanisms for NVM to achieve program stack persistence efficiently. Even with adaptations, state-of-the-art memory persistence mechanisms such as undo and redo logging incur more than 35× slowdown in persisting stack compared to no persistence (i.e., stack in DRAM). Thus, to address inbuilt inefficiencies in state-of-theart memory persistence approaches while using them for the stack, we propose *Prosper*, a periodic checkpointing-based hardware-software co-designed approach that handles unique stack properties. Prosper hardware tracks stack modifications at sub-page granularity, resulting in  $\sim 4 \times$  reduction (on average) in checkpoint size compared to the state-of-theart scheme based on the memory management unit for tracking memory updates (dirty bit scheme). Prosper hardware introduces performance overhead of less than 1% on average, providing up to 3.6× reduction in stack persistence overhead compared to the state-ofthe-art NVM memory persistence schemes. Integration of Prosper with existing state-ofthe-art memory persistence mechanisms for heap also benefits achieving persistence for the entire memory area, providing 2.6× improvement over solely using the state-of-the-art mechanism for the entire memory area persistence.

This thesis contributes infrastructure and mechanisms for process persistence in a hybrid memory system with NVM and DRAM. The thesis initially provides insights into the performance overhead of primitive and advanced memory persistence mechanisms for NVM and later proposes a hybrid memory simulation framework with NVM and DRAM. The framework incorporates process persistence semantics using a periodic checkpoint-based scheme to maintain the execution context and memory state of a process consistently. Notably, we create an efficient stack tracing framework and show the need to specialize memory persistence schemes based on the memory area (heap or stack) under consideration by bringing out stack-specific properties using the framework. Finally, we propose

Abstract vii

a checkpoint-based memory persistence scheme for the stack that handles unique stack properties and provides efficient stack persistence.

# Acknowledgements

I extend my heartfelt gratitude to all faculty members and technical and non-technical staff of the Computer Science and Engineering Department at IIT Kanpur for their unwavering support throughout my PhD journey. I am grateful to CDOS research group members, KD-222 lab members, and fellow PhD students for the invaluable guidance and knowledge they shared during discussions. I thank Dr. Biswabandan Panda, who moved to IIT Bombay during COVID-19, for making this PhD journey possible by offering me a position at IIT Kanpur. I am fortunate to have worked with Dr. Debadatta Mishra as my primary supervisor and received his technical wisdom and constant support, which made my PhD journey smooth and intellectually satisfying.

I am immensely thankful to my wife, parents, family, and friends for their comfort and support throughout this journey, enabling me to focus on and complete my PhD work. I thank all my teachers, starting from school days, who believed in me unconditionally.

Finally, I am indebted to all citizens of India for the financial support I received through my PhD fellowship and to every known and unknown individual whose blood, sweat, and tears made each day of this journey possible.

# Contents

| A  | Acknowledgements vi |                                                             |      |  |  |

|----|---------------------|-------------------------------------------------------------|------|--|--|

| Li | st of               | Figures                                                     | xii  |  |  |

| Li | st of               | Tables                                                      | xiv  |  |  |

| A  | bbre                | ations                                                      | xvi  |  |  |

| 1  | Inti                | duction                                                     | 1    |  |  |

|    | 1.1                 | Crash consistency challenge                                 | . 2  |  |  |

|    | 1.2                 | System efficiency challenge                                 | . 4  |  |  |

|    | 1.3                 | Process persistence in a hybrid NVM system                  | . 5  |  |  |

|    | 1.4                 | Contributions                                               | . 6  |  |  |

|    |                     | 1.4.1 Empirical analysis of architectural primitives        | . 7  |  |  |

|    |                     | 1.4.2 Hybrid memory framework with DRAM and NVM             | . 8  |  |  |

|    |                     | 1.4.3 Stack tracing framework for multi-threaded programs   | . 9  |  |  |

|    |                     | 1.4.4 Checkpoint based scheme for program stack persistence | . 9  |  |  |

|    | 1.5                 | Thesis Organization                                         | . 10 |  |  |

| 2  | Bac                 | ground                                                      | 12   |  |  |

|    | 2.1                 | Importance of Data Consistency in NVM                       | . 12 |  |  |

|    | 2.2                 | Architecture primitives for Data Consistency                | . 14 |  |  |

|    |                     | 2.2.1 Intel x86-64                                          | . 14 |  |  |

|    |                     | 2.2.2 Arm64                                                 | . 15 |  |  |

|    | 2.3                 | Advanced Techniques for Data Consistency                    | . 16 |  |  |

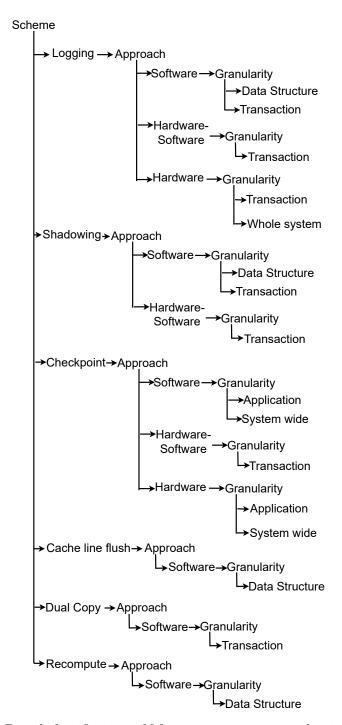

|    |                     | 2.3.1 Classification Based on Usage Granularity             |      |  |  |

|    |                     | 2.3.2 Classification Based on Scheme                        | . 22 |  |  |

|    |                     | 2.3.3 Classification Based on Memory Update Monitoring      | . 26 |  |  |

|    | 2.4                 | Achieving Process Persistence                               | . 27 |  |  |

| 3  | Em                  | irical Analysis of Architectural Primitives                 | 29   |  |  |

|    | 3.1                 | Setup and Methodology                                       | . 31 |  |  |

Contents

|   |      | 3.1.1 Benchmarks and Parameters                                  |

|---|------|------------------------------------------------------------------|

|   |      | 3.1.2 Redo and Undo Logging                                      |

|   |      | 3.1.3 Why do we focus on flush-based data consistency methods? 3 |

|   | 3.2  | Evaluation of data consistency primitives                        |

|   |      | 3.2.1 Performance with Intel x86-64                              |

|   |      | 3.2.2 Performance with Arm64                                     |

|   | 3.3  | Performance of Redo and Undo Logging                             |

|   |      | 3.3.1 Performance with x86-64                                    |

|   |      | 3.3.2 Performance with Arm64                                     |

|   | 3.4  | Influence on co-running applications                             |

|   | 3.5  | Summary                                                          |

| 4 | Kin  | dle: A Hybrid Memory Framework 54                                |

| • | 4.1  | Design and Implementation                                        |

|   | 7.1  | 4.1.1 Process Persistence                                        |

|   |      | 4.1.2 Kindle Framework                                           |

|   | 4.2  | Evaluation                                                       |

|   | 4.2  |                                                                  |

|   |      |                                                                  |

|   |      | 4.2.2 SSP using Kindle                                           |

|   | 4.0  | 4.2.3 HSCC using Kindle                                          |

|   | 4.3  | Summary                                                          |

| 5 | Fra  | mework for Multi-threaded Program Stack Tracing 70               |

|   | 5.1  | Design and Implementation                                        |

|   | 5.2  | Evaluation                                                       |

|   |      | 5.2.1 Stack tracing with SniP                                    |

|   |      | 5.2.2 Use cases                                                  |

|   |      | 5.2.2.1 Tracing ML Classification Algorithms 8                   |

|   |      | 5.2.2.2 Detecting uninitialized memory usage in stack 8          |

|   | 5.3  | Related Work                                                     |

|   | 5.4  | Summary                                                          |

| 6 | Pro  | gram Stack Persistence in Hybrid Memory Systems 8'               |

|   | 6.1  | Motivation                                                       |

|   |      | 6.1.1 Inefficiency due to Stack Pointer Unawareness 9            |

|   |      | 6.1.2 Inefficiency of Page-level Dirty Tracking                  |

|   | 6.2  | Dirty Tracking with Prosper                                      |

|   | 0.2  | 6.2.1 Prosper Software                                           |

|   |      | 6.2.2 Prosper Hardware                                           |

|   |      | 6.2.3 Multi-threading Support                                    |

|   |      | 6.2.4 Implementation                                             |

|   | 6.3  | Experimental Setup                                               |

|   | 0.0  |                                                                  |

|   |      | 6.3.1 Checkpoint Performance                                     |

|   | 0.4  | 6.3.2 Tracking Overhead Experiments                              |

|   | 6. 1 | L'ive line trop                                                  |

| $\mathbf{X}^{\mathbf{I}}$ |

|---------------------------|

|                           |

|    | 6.5   | Summ   | nary                                                             | . 115 |

|----|-------|--------|------------------------------------------------------------------|-------|

| 7  | Cor   | clusio | ons and Future Directions                                        | 116   |

|    | 7.1   | Summ   | nary and Conclusions                                             | . 116 |

|    | 7.2   | Futur  | e Directions                                                     | . 118 |

|    |       | 7.2.1  | Empirical Analysis on the Influence of NVM Device on Persistence | . 118 |

|    |       | 7.2.2  | Memory Persistence using CXL attached persistent memory          | . 119 |

| Li | st of | Publi  | cations                                                          | 121   |

| Bi | bliog | graphy | ,                                                                | 122   |

# List of Figures

| 1.1 | Illustration of the need to order stores to NVM in the presence of volatile caches                                                                | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Illustration of persistent barrier to order stores to NVM in the presence of volatile caches.                                                     | 3  |

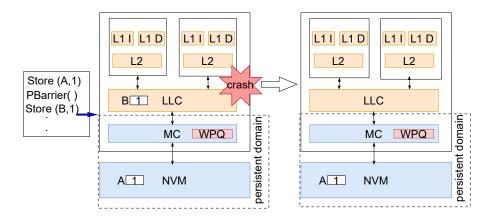

| 1.3 | Schematic diagram for different ways to persist data in hybrid memory systems                                                                     | Ę  |

| 1.4 | Contributions in this thesis                                                                                                                      | 7  |

| 2.1 | Broad classification of Memory persistence mechanisms for NVM                                                                                     | 18 |

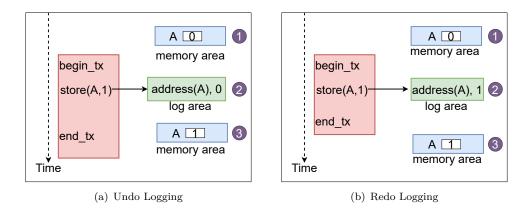

| 2.2 | Write-Ahead logging mechanisms                                                                                                                    | 22 |

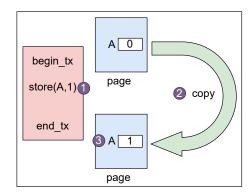

| 2.3 | Copy-on-write mechanism                                                                                                                           | 24 |

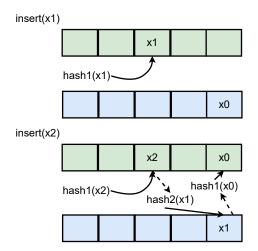

| 3.1 | Insert operations on Cuckoo Hashing data structure                                                                                                | 32 |

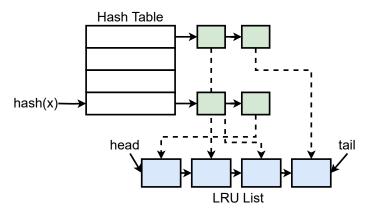

| 3.2 | Schematic diagram of LRU micro-benchmark                                                                                                          | 33 |

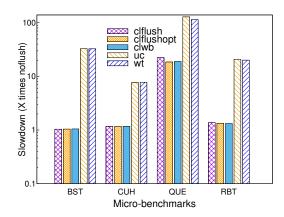

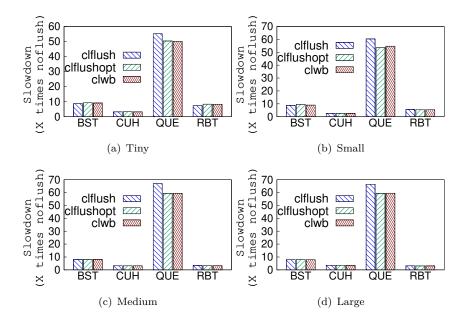

| 3.3 | Performance overhead of data consistency methods. Y-axis values are slow-                                                                         |    |

|     | down with respect to noflush (not using any data consistency method)                                                                              | 35 |

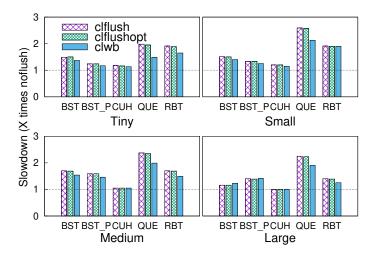

| 3.4 | Performance slowdown with different data consistency methods in gem5                                                                              |    |

|     | simulation of x86-64 system. Y-axis values are slowdown normalized to                                                                             |    |

|     | noflush (lower the better)                                                                                                                        | 36 |

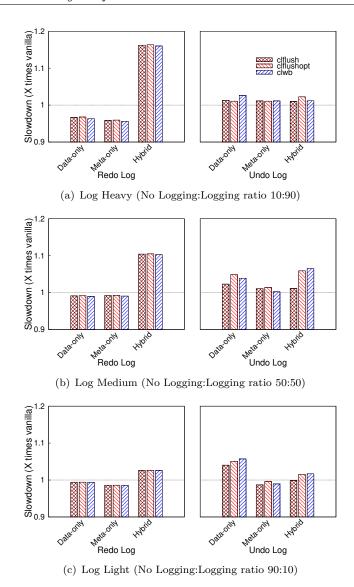

| 3.5 | Performance slowdown under data consistency methods in real x86-64 system. Y-axis values are slowdown with respect to noflush (lower the better). | 40 |

| 3.6 | Performance slowdown with different data consistency methods in gem5                                                                              | -  |

| 0.0 | simulation of Arm64 system. Y-axis values are slowdown normalized to                                                                              |    |

|     | noflush (lower the better)                                                                                                                        | 41 |

| 3.7 | Influence of data consistency methods based on nature of update operations                                                                        |    |

| J., | for different logging requirements in gem5 simulation of x86-64 system. Y-                                                                        |    |

|     | axis values are slowdown w.r.t. vanilla case of no logging (lower the better).                                                                    | 43 |

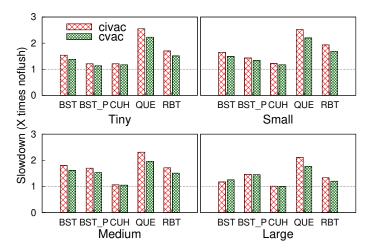

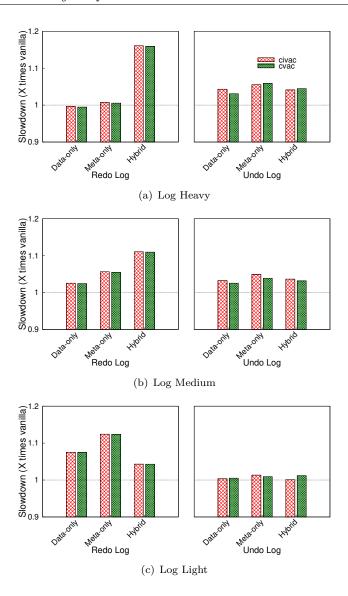

| 3.8 | Influence of data consistency methods based on nature of update operations                                                                        |    |

|     | for different logging requirements in gem5 simulation of Arm64 system. Y-                                                                         |    |

|     | axis values are slowdown w.r.t. vanilla case of no logging (lower the better).                                                                    | 47 |

| 4.1 | Number of publications on hybrid memory systems with NVM, listed in                                                                               |    |

|     | Google Scholar                                                                                                                                    | 55 |

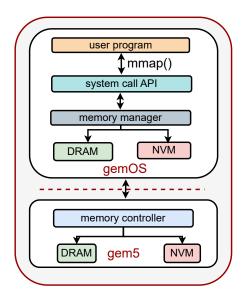

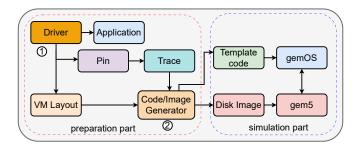

| 4.2 | Interaction between gem5 and gemOS in Kindle                                                                                                      | 57 |

| 4.3 | Schematic diagram of Kindle                                                                                                                       | 59 |

List of Figures xiii

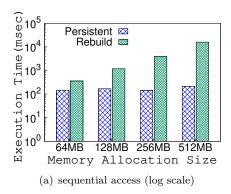

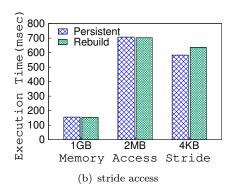

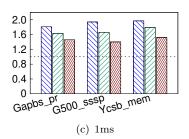

| 4.4        | Influence of memory access size and stride length on execution time with periodic checkpointing for context while using different page table consistency schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

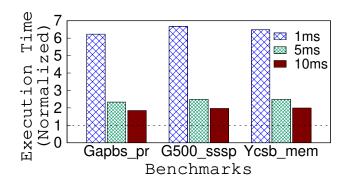

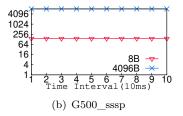

| 4.5        | Influence of memory consistency interval on performance. Y-axis shows normalized execution time with no memory consistency 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.6        | Influence of OS migration activities on application performance under DRAM fetch threshold 5, 25, and 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

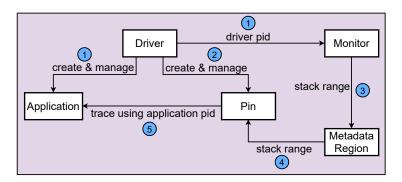

| 5.1<br>5.2 | Schematic diagram of SniP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

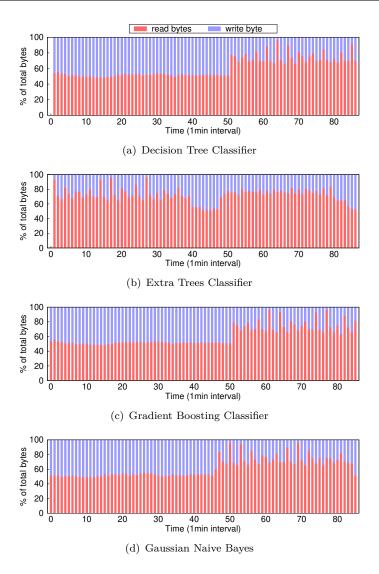

| 5.3        | Percentage of read and write access to stack of Machine Learning classification algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

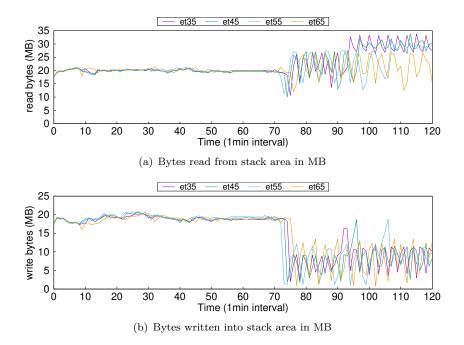

| 5.4        | Read and write behaviour of Extra Trees Classifier with varying feature set size [et35, et45, et55, et65 represents 35, 45, 55, 65 feature sizes] 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

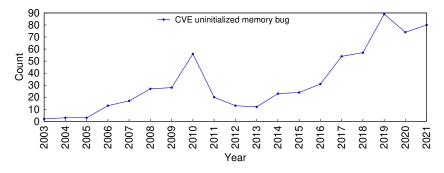

| 5.5        | CVE uninitialized memory bugs reported over years                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.6        | JSON file format, Python parser output of uninitialized memory bug $84$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

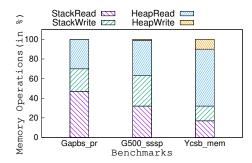

| 6.1        | Memory operations to the stack and heap regions (in %) demonstrating the significance of stack operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

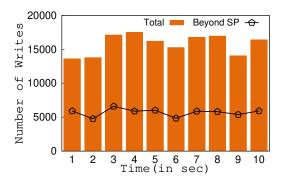

| 6.2        | Number of total stack writes and writes beyond final stack pointer (SP) aggregated at 100 intervals with each interval of 10ms for Ycsb_mem benchmark. 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

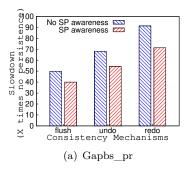

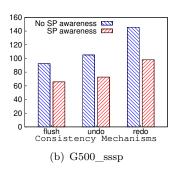

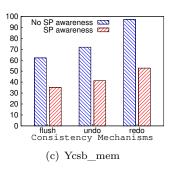

| 6.3        | Slowdown of primitive memory persistence mechanisms with SP awareness and No SP awareness with respect to no persistence (DRAM). SP awareness: stack pointer awareness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

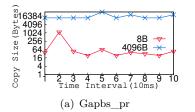

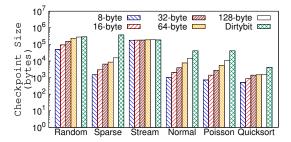

| 6.4        | Comparison of checkpoint size in page and byte level dirty tracking of stack modifications. Y axis shows copy size in page (4096 Byte) and sub-page (8 Byte) granularity tracking for benchmarks in Figure 6.1 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

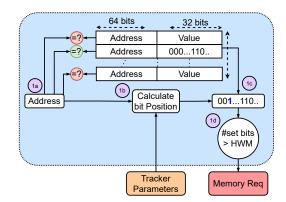

| 6.5        | Schematic diagram of Prosper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.6        | Schematic diagram of Prosper hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.7        | Working of the Prosper hardware tracker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

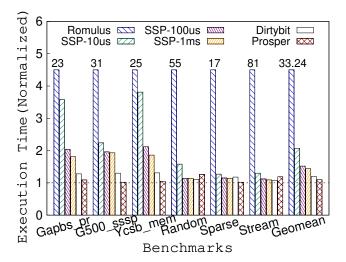

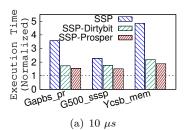

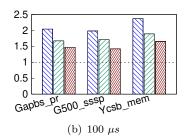

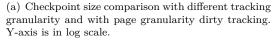

| 6.8        | Application performance comparison with different memory persistence mechanisms applied to stack. Y-axis shows application execution time with memory persistence required to personalized to personalized to be presistenced to be applied to the leavest the lea |

| 6.9        | ory persistence normalized to no persistence, the lower the better 108 Performance comparison for heap+stack area persistence, with SSP with different intervals. Y-axis shows the execution time normalized to no persis-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | tence, lower the better                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

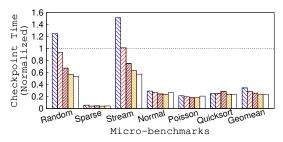

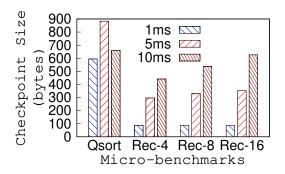

| 6.10       | Stack checkpoint performance for different micro-benchmarks with <i>Prosper</i> . 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | Influence of checkpoint interval on checkpoint size with dirty stack tracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

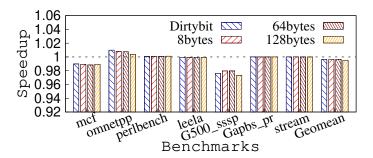

| 6 19       | using Prosper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

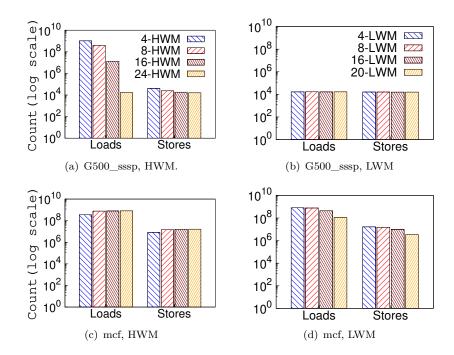

|            | Tracking overhead for different SPEC workloads. Y-axis shows an application's performance under dirty tracking with respect to no dirty tracking 113 Sensitivity of HWM and LWM for bitmap load and store operations. For                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0.10       | HWM study LWM is fixed at 4 and for LWM study HWM is fixed at 24 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# List of Tables

| 2.1  | Memory persistence mechanisms for NVM                                                        | 17 |

|------|----------------------------------------------------------------------------------------------|----|

| 3.1  | Microbenchmarks used in the experiments                                                      | 31 |

| 3.2  | Working set sizes used for experiments on gem5                                               | 33 |

| 3.3  | Gem5 configuration                                                                           | 34 |

| 3.4  | Cache miss and ROB stall behavior with large working set                                     | 38 |

| 3.5  | LLC MPKI with Medium and Small working set                                                   | 36 |

| 3.6  | Working set sizes used for real system experiments                                           | 39 |

| 3.7  | Influence of read-to-write ratio on performance slowdown in gem5 simula-                     |    |

|      | tion of Arm64 system                                                                         | 42 |

| 3.8  | L1-D cache miss and replacements with logging using clwb in gem5 simulation of x86-64 system | 44 |

| 3.9  | L1-D cache misses with redo and undo logging in gem5 simulation of x86-64                    |    |

|      | system                                                                                       | 45 |

| 3.10 | Number of times rename stage is blocked due to no space in ROB in gem5                       |    |

|      | simulation of x86-64 system                                                                  | 46 |

| 3.11 | Number of times instruction commit has stalled in gem5 simulation of                         |    |

|      | Arm64 system                                                                                 | 48 |

| 3.12 | L1-D miss rate (in %) with logging using cvac in gem5 simulation of Arm64                    |    |

|      | system                                                                                       | 48 |

|      | Number of L1-D replacements in gem5 simulation of Arm64 system                               | 49 |

| 3.14 | Performance of SPEC while co-running with micro-benchmarks in gem5                           |    |

|      | simulation of x86-64 system                                                                  | 50 |

| 3.15 | LLC MPKI of SPEC while co-running with micro-benchmarks in gem5 sim-                         |    |

| 0.10 | ulation of x86-64 system                                                                     | 51 |

| 3.16 | Key takeaways from the empirical analysis                                                    | 53 |

| 4.1  | gem5 Memory Configuration                                                                    | 57 |

| 4.2  | Benchmark Details                                                                            | 61 |

| 4.3  | Execution time with periodic checkpointing of execution context for differ-                  |    |

|      | ent VMA modification size                                                                    | 65 |

| 4.4  | Influence of checkpoint interval on execution time for periodic checkpointing                |    |

|      | of execution context                                                                         | 67 |

| 4.5  | Number of Pages Migrated                                                                     | 71 |

| 4.6  | Percentage of time spent for page selection and page copy in OS migration                    |    |

|      | activity.                                                                                    | 72 |

List of Tables

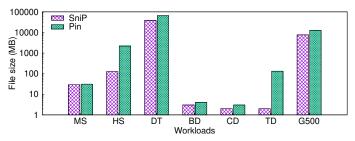

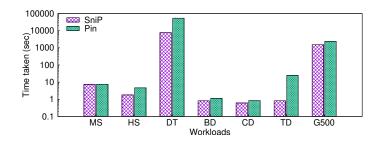

| 5.1 | Comparison of size and time for SniP stack tracing w.r.t Pin full tracing | 80  |

|-----|---------------------------------------------------------------------------|-----|

| 6.1 | Comparison of existing memory persistence mechanisms                      | 90  |

| 6.2 | gem5 Configuration                                                        | 104 |

| 6.3 | Microbenchmarks with different stack usage scenarios                      | 107 |

# Abbreviations

**NVM** Non-Volatile Memory

**ISA** Instruction Set Architecture

**HDD** Hard Disk Drive

SSD Solid State Drive

**PCM** Phase Change Memory

FASE Failure Atomicity Section

**ADR** Asynchronous DRAM Refresh

SP Stack Pointer

**ROB** Reorder Buffer

**HWM** High Water Mark

**LWM** Low Water Mark

WPQ Write Pending Queue

MC Memory Controller

WAL Write Ahead Logging

**CoW** Copy on Write

MPKI Misses Per Kilo Instructions

Abbreviations xvii

**LLC** Last Level Cache

**DCPMM** Data Center Persistent Memory Module

PTBR Page Table Base Register

**TLB** Transaction Lookaside Buffer

**PTE** Page Table Entry

**API** Application Programming Interface

Dedicated to Universe.

# Chapter 1

## Introduction

Process persistence enables applications to resume execution from a consistent state after restart or system crash. Process persistence requires periodically saving the state of a process consisting of CPU registers, memory, and OS meta-data in a persistent device [1]. The time needed to save state in a persistent device depends upon the access latency of the device and the method used to persist data. For example, using file system layers [2, 3] to persist data on secondary storage devices (HDDs and SSDs) incurs serialization and other related software overheads. Therefore, an efficient process persistence approach requires a device with better access latency. The device should also provide access without additional software layers. Byte addressable Non-Volatile Memory (NVM) meets this requirement by providing access through the CPU load/store interface and persists data with access latency comparable to volatile DRAM [4]. NVM, connected to a system's memory interface, facilitates direct access by eliminating complex storage management middle-wares such as file systems [5]. Thus, NVM provides an opportunity to build efficient infrastructure and mechanisms to achieve process persistence with minimum performance overhead.

However, using NVM for persistence presents the following challenges related to *crash* consistency and system efficiency. Crash consistency challenges arise due to direct access from the CPU through the load/store interface. The system efficiency challenge occurs if NVM is used as the sole memory in the system by replacing conventional DRAM memory.

1. Crash consistency: Data path from CPU to NVM consists of intermediate volatile components such as hardware caches. Ensuring consistency of memory updates in the presence of these volatile components requires specialized techniques to provide a

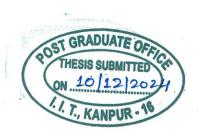

FIGURE 1.1: Illustration of the need to order stores to NVM in the presence of volatile caches.

consistent memory state across system restarts. In-flight data in these intermediate volatile components are lost in case of a power failure or abrupt restart. Moreover, these components can change the order of writes to NVM based on exerted data eviction policies, causing deviation in the actual memory state from the expected program state. These intricacies of processor-memory data path organization require non-trivial adaptation of traditional file systems or database techniques (e.g., journaling and transactions [6]) to use for NVM [7–10].

2. **System Efficiency:** NVM has higher read and write latency than DRAM; for example, phase change memory (PCM) is 1.6× slower than DRAM [11]. Therefore, using NVM as a drop-in replacement for DRAM leads to poor application performance.

### 1.1 Crash consistency challenge

The crash consistency challenge is due to the presence of volatile intermediate components in the data path to NVM. Therefore, addressing this challenge requires mechanisms to determine whether writes reach the persistent domain and verify the order in which writes reach the persistent domain. Persistent domain encompasses system components that can retain data across reboots. Thus, mechanisms to address this challenge, i.e., memory persistence mechanisms, should ensure the order of writes to the persistent domain. The mechanisms should also provide detectability, i.e., assurance on whether a write is complete or not from the objective of recovery after a crash [12–15]. For example, Figure 1.1

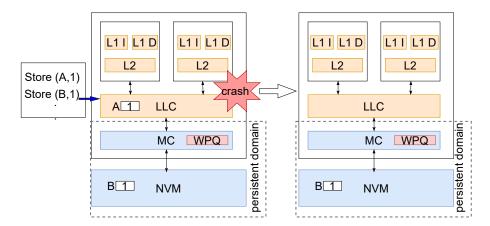

Figure 1.2: Illustration of persistent barrier to order stores to NVM in the presence of volatile caches.

demonstrates the need to order writes to the persistent domain in the presence of volatile caches.