# JOLOKIAC++ : AN ANNOTATION BASED COMPILER FRAMEWORK FOR GPGPU

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> by VIBHA PATEL

to the

### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING INDIAN INSTITUTE OF TECHNOLOGY KANPUR, INDIA

June 2014

# CERTIFICATE

It is certified that the work contained in the thesis entitled "JolokiaC++ : An Annotation based Compiler Framework for GPGPU" by Vibha Patel has been carried out under our supervision and that this work has not been submitted elsewhere for a degree.

(Late) Dr. Sanjeev Aggarwal Professor, Department of Computer Science and Engineering, Indian Institute of Technology Kanpur, Kanpur-208016, INDIA.

Dr. Harish Karnick Professor, Department of Computer Science and Engineering, Indian Institute of Technology Kanpur, Kanpur-208016, INDIA.

#### dury tarpare

Dr. Amey Karkare Assitant Professor, Department of Computer Science and Engineering, Indian Institute of Technology Kanpur, Kanpur-208016, INDIA.

Vivek Saskas

Dr. Vivek Şarkar Professor of Computer Science, E.D. Butcher Chair in Engineering, Rice University Houston, Texas, USA

### Abstract

We present the design and implementation of a generic annotation based compiler framework, JolokiaC++, which generates high quality CUDA (Compute Unified Device Architecture) code for GPUs. The framework abstracts the details of the underlying hardware using annotations, thus allowing an end-user to write parallel programs without detailed knowledge about the hardware. The end-user can extract an acceptable level of performance from GPU hardware without worrying about low level details of the hardware like data allocation, memory organization and communication overhead.

The ultimate goal of the framework is to increase productivity without compromising performance. The proposed key ingredients to achieve the goals of productivity and performance are implicit and explicit annotations supported by task-level data flow analysis and operation-level data flow analysis. JolokiaC++ can also optimize irregular data applications on GPUs. We developed extensions for the generic parallel constructs that allow portable and efficient programming of codes with irregular accesses on the GPU.

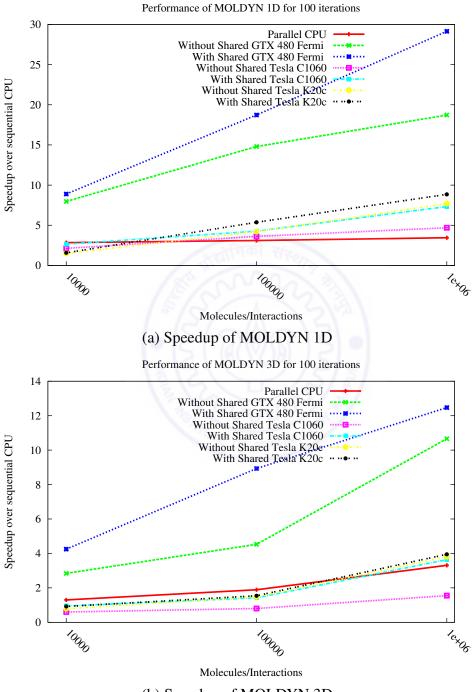

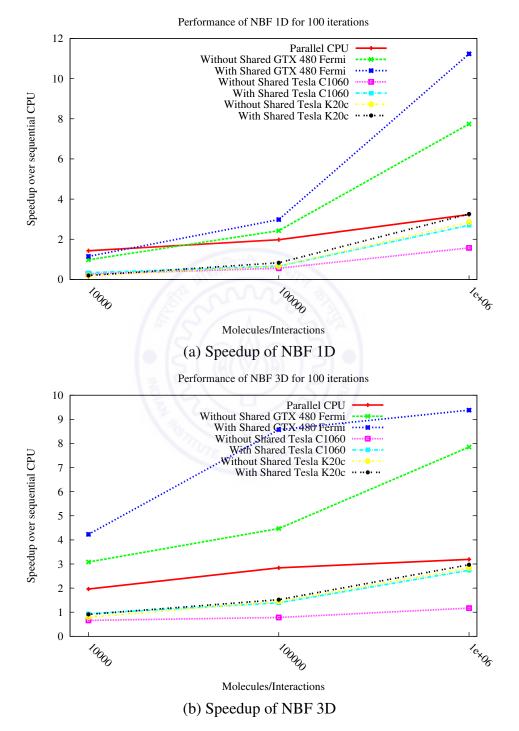

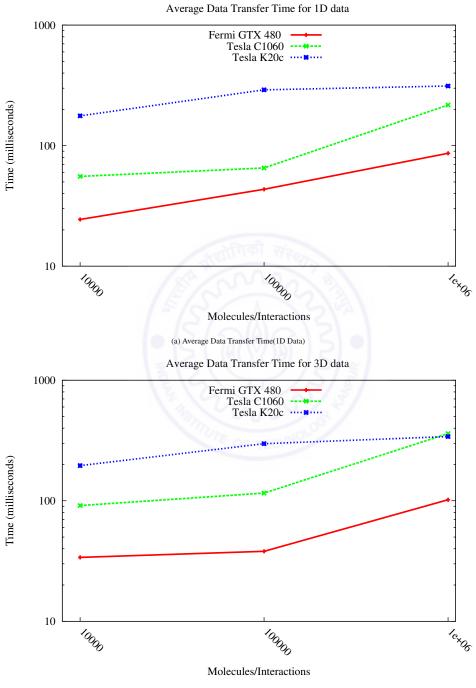

We evaluate and show the effectiveness of our framework on kernels with regular and irregular accesses. The regular access kernels include Blackscholes, Matrix-Vector multiplication, Matrix-Matrix multiplication, Jacobi 1D & 2D, Heat 2D, Vector Addition and Convolution. We evaluated the performance of regular kernel on Nvidias GeForce 770 using CUDA version 5.5. The inspector-executor composition for irregular accesses in our framework is evaluated by generating synthetic data for aggregation benchmarks: MOL-DYN, IRREG and NBF. We present experimental results from compiling the irregular

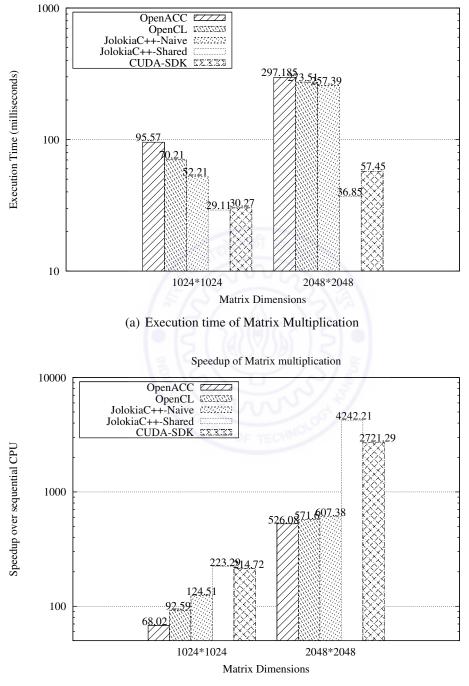

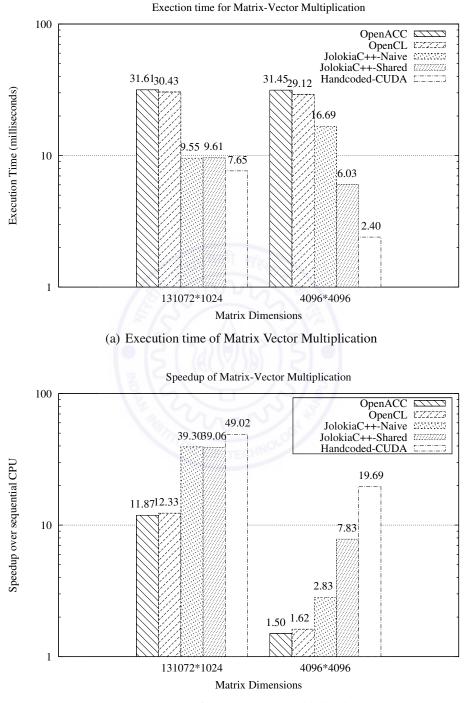

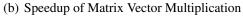

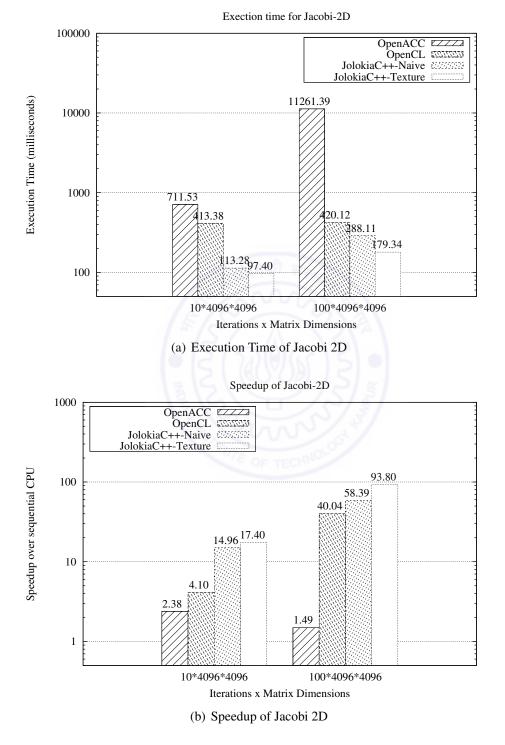

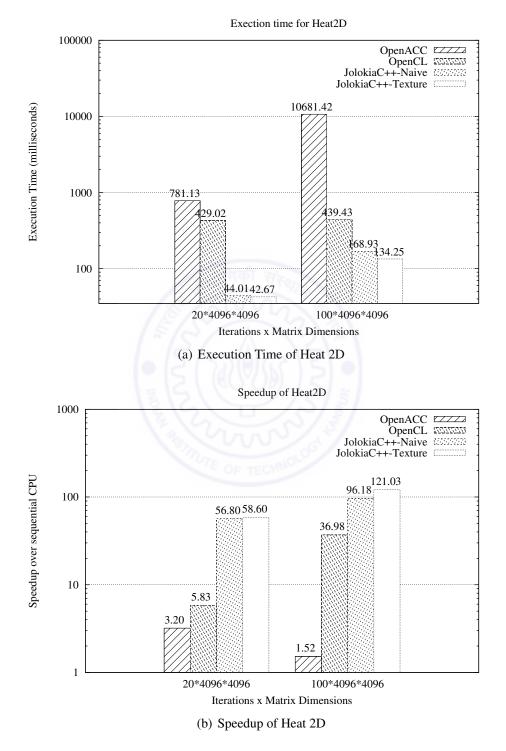

data kernels for execution on Fermi GTX 480, Tesla C1060 and Tesla K20c GPUs. The speedup of optimized JolokiaC++ implementation for regular kernels ranges from 0.89 - 4242.21 as compared to OpenCL which ranges from 0.42 - 571.59 and OpenACC which ranges from 1.08 - 526.08. The speedup of shared memory composition of irregular kernels ranges from 0.59 - 11.23 as compared to the composition without shared memory implementation which ranges from 0.5 - 7.74. The speedup of optimized JolokiaC++ when compared with hand-written OpenCL and OpenACC implementation for regular kernels ranges from 0.52 - 17.13 and 0.199 - 79.56 respectively.

The speedup of almost all the regular kernels using optimized JolokiaC++ is better when compared with OpenCL and OpenACC implementations. The shared memory composition of the inspector/executor mechanism for irregular kernels performs reasonably well when compared with a sequential CPU based implementation and without shared memory composition. Experimental results indicate that the annotation based framework can help domain experts to achieve better performance using GPUs without knowing the details of the architecture and programming intricacies.

vi

### Acknowledgements

At this moment of accomplishment, first of all I pay homage to my guide, Late. Prof. Sanjeev K. Aggarwal. This work would not have been possible without his guidance, support and encouragement academically as well as personally. He has been a wonderful mentor and a facilitator. Under his guidance I successfully overcame many difficulties and learned a lot. Despite of his extremely busy schedule, he has always accommodated me whenever I needed his guidance. His unflinching courage and conviction will always inspire me, and I hope to continue to work with his noble thoughts. I wish his soul roots in peace and solace in the heaven. I can only say a proper thanks to him through my future work.

I am also extremely indebted to my guide Prof. Harish Karnick, for picking me up as a student at the critical stage of my Ph.D. I warmly thank my co-guide, Prof. Amey Karkare, for his valuable advice, constructive criticism and his extensive discussions around my work. I would like to express my deepest gratitude to my co-guide, Prof. Vivek Sarkar, for his support and guidance in my thesis. I am thankful to all the faculty members of the department to provide a research conducive environment.

My life as a PhD student has been full of fun, thanks to my dear friends Umarani, Surya, Rohit, Purushottam, Amrita, Ajitha, Saiful, Puneet, Pawan and the entire class of MTech 2008. Thanks to the administrative staff members for making all the paper work hassle-free. Thanks to the lab staff members for technical and infrastructural support. I especially thank Research-I foundation for funding my visits to conferences. I acknowledge the financial support for my PhD from the Ministry of Human Resources and Development.

I am grateful for the unconditional and unquestioning support from my loving husband throughout my work. My very existence is indebted to my parents and I thank them to make me what I am today. I would like to pay high regards to my brother and sisters for their sincere encouragement and inspiration throughout my research work and lifting me uphill this phase of life.

Last but not the least, I thank the God almighty for giving me strength all my life.

Dedicated

to

My Family Members & Respected Teachers

# Contents

| Li | List of Tables xiv |                                                       |     |  |

|----|--------------------|-------------------------------------------------------|-----|--|

| Li |                    |                                                       |     |  |

| Li | st of A            | Algorithms                                            | xix |  |

| Li | st of A            | Abbreviations                                         | xxi |  |

| 1  | Intr               | oduction                                              | 1   |  |

|    | 1.1                | Key Challenges for General Purpose Programming on GPU | 3   |  |

|    |                    | 1.1.1 Lack of Memory Hierarchy Management support     | 3   |  |

|    |                    | 1.1.2 Lack of Language Support                        | 4   |  |

|    |                    | 1.1.3 Thread Block Synchronization on GPU             | 4   |  |

|    |                    | 1.1.4 Inadequate Parameter Modeling Support           | 4   |  |

|    | 1.2                | GPU Programming using JolokiaC++                      | 5   |  |

|    | 1.3                | Our Contributions                                     | 5   |  |

|    | 1.4                | Organization of the Thesis                            | 8   |  |

| 2  | Bac                | kground and Related Work                              | 9   |  |

|    | 2.1                | Basic Terms                                           | 9   |  |

|    | 2.2                | Background                                            | 10  |  |

|    |                    | 2.2.1 GPU Parallel Computing Architecture             | 10  |  |

|   |      | 2.2.2   | Execution Model                                                     | 11 |

|---|------|---------|---------------------------------------------------------------------|----|

|   |      | 2.2.3   | CUDA Programming Model                                              | 12 |

|   | 2.3  | Related | d Work                                                              | 12 |

| 3 | Lan  | guage D | Design                                                              | 21 |

|   | 3.1  | Design  | of JolokiaC++ Framework                                             | 23 |

|   |      | 3.1.1   | JolokiaC++ Programming Model                                        | 24 |

|   |      | 3.1.2   | JolokiaC++ Annotations                                              | 25 |

|   |      | 3.1.3   | Task-Level Data Flow Graph                                          | 30 |

|   |      | 3.1.4   | Operation-Level Data Flow Graph                                     | 31 |

| 4 | Reg  | ular Ap | plications                                                          | 37 |

|   | 4.1  | Memor   | ry Access Operators                                                 | 38 |

|   | 4.2  | Compi   | ling high level JolokiaC++ constructs                               | 42 |

|   |      | 4.2.1   | Task-Level Data Flow Analysis for Optimizing Communication .        | 46 |

|   |      | 4.2.2   | Operation-Level Data Flow Analysis for Optimizing Memory Ac-        |    |

|   |      |         | cess                                                                | 47 |

| 5 | Irre | gular D | ata Applications                                                    | 55 |

|   | 5.1  | Prelim  | inaries of the Framework                                            | 58 |

|   | 5.2  | Optimi  | zation of Irregular Applications                                    | 59 |

|   |      | 5.2.1   | Flow Analysis Framework for GPU                                     | 61 |

|   |      | 5.2.2   | Code Generation using Sparse Polyhedral Framework                   | 65 |

|   |      | 5.2.3   | Executor Code Generation                                            | 73 |

|   |      | 5.2.4   | Inter-Block synchronization using lock-free barrier                 | 74 |

|   | 5.3  | Empiri  | cal Search for Selection of Optimal Tile Size and Scheduling Policy | 76 |

|   |      |         |                                                                     |    |

|    | 6.1 Experimental Methodology and Performance Results for Regular Access |                                                     |     |

|----|-------------------------------------------------------------------------|-----------------------------------------------------|-----|

|    |                                                                         | Kernels                                             | 79  |

|    |                                                                         | 6.1.1 Ease of Programming                           | 81  |

|    |                                                                         | 6.1.2 Performance Results and Discussion            | 84  |

|    | 6.2                                                                     | Experimental Evaluation of Irregular Access Kernels | 85  |

| 7  | Con                                                                     | clusion and Future Work                             | 101 |

| Aŗ | pend                                                                    | ices                                                | 103 |

| A  | Ann                                                                     | otation Grammar Specification                       | 105 |

| Pu | blica                                                                   | tions                                               | 119 |

# **List of Tables**

| 3.1 | CPU-GPU Memory Space Management Annotations                          | 28 |

|-----|----------------------------------------------------------------------|----|

| 6.1 | Test Set and their Configuration                                     | 80 |

| 6.2 | Execution time of benchmarks in milliseconds                         | 83 |

| 6.3 | Speedup of the benchmarks over sequential CPU implementations        | 83 |

| 6.4 | Configuration of GPUs                                                | 85 |

| 6.5 | Execution time of Sequential (Seq) and Parallel (Par) hand-coded CPU |    |

|     | implementation in milliseconds                                       | 86 |

| 6.6 | Execution Time of IRREG in milliseconds                              | 87 |

| 6.7 | Execution Time of MOLDYN in milliseconds                             | 88 |

| 6.8 | Execution Time of NBF in milliseconds                                | 89 |

| 6.9 | Average Reordering Time in milliseconds                              | 89 |

# **List of Figures**

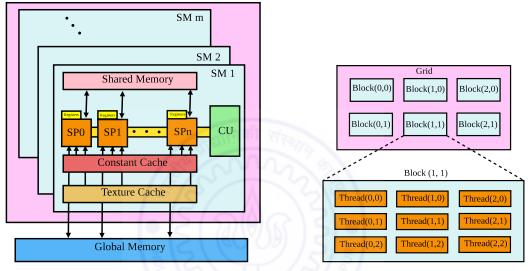

| 2.1 | CUDA Parallel Computing Architecture and Programming Model                | 11 |

|-----|---------------------------------------------------------------------------|----|

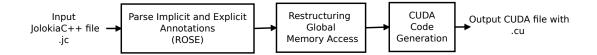

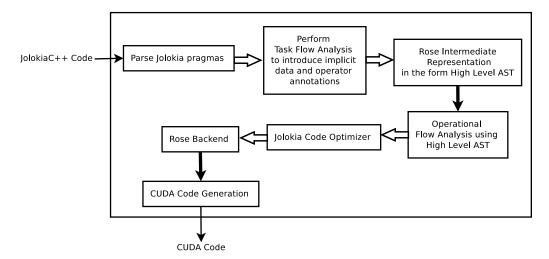

| 3.1 | Compilation Framework of JolokiaC++                                       | 22 |

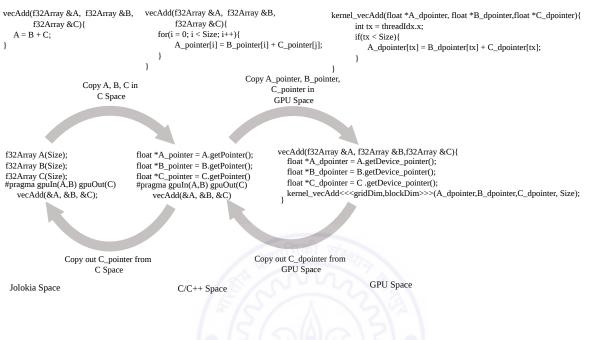

| 3.2 | Translation spaces in JolokiaC++                                          | 24 |

| 3.3 | Translation of JolokiaC++ code                                            | 25 |

| 3.4 | Task-Level Data Flow Graph                                                | 32 |

| 4.1 | Memory Access Patterns and their Respective Operator Annotations with     |    |

|     | their Linearized Representation.                                          | 38 |

| 4.2 | Inter and Intra-thread access of elements in absence of scratchpad anno-  |    |

|     | tation                                                                    | 41 |

| 4.3 | Inter and Intra-thread access of elements in presence of scratchpad anno- |    |

|     | tation                                                                    | 42 |

| 4.4 | Memory Access Pattern of Naive Matrix-Vector Multiplication without       |    |

|     | Scratchpad Annotation                                                     | 51 |

| 4.5 | Memory Access Pattern of Matrix-Vector Multiplication using Scratch-      |    |

|     | pad Annotation                                                            | 52 |

| 4.6 | Operation-Level Data Flow Tree for Matrix-Vector Multiplication           | 53 |

| 4.7 | Composed Task and Operation-Level Data Flow Tree                          | 54 |

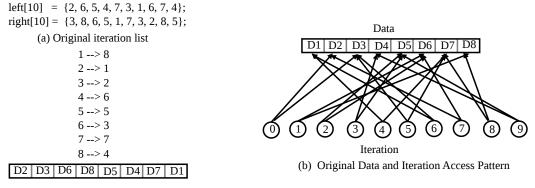

| 5.1 | Irregular Memory Access                                                   | 56 |

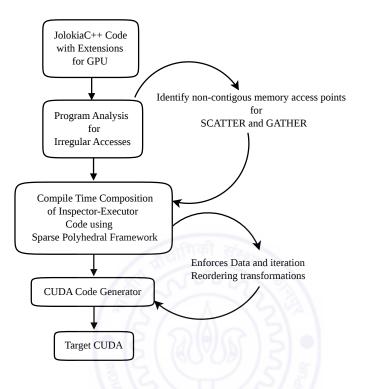

| 5.2  | Compiler Framework for Optimizing Irregular Applications | 58 |

|------|----------------------------------------------------------|----|

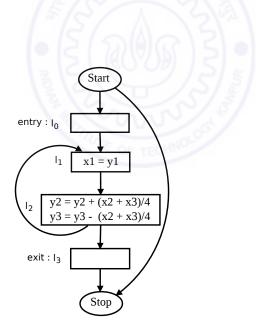

| 5.3  | Loop Flow Graph for the Code in Listing 5.1              | 60 |

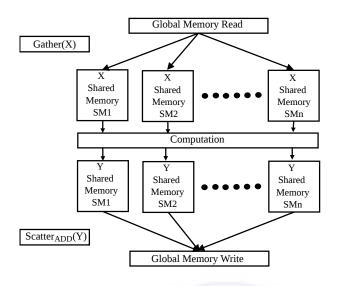

| 5.4  | Scatter/Gather for Simplified MOLDYN Kernel              | 66 |

| 5.5  | Compile Time Composition of Inspector                    | 73 |

| 6.1  | Performance of Matrix Multiplication                     | 90 |

| 6.2  | Performance of Matrix Vector Multiplication              | 91 |

| 6.3  | Performance of Jacobi 2D                                 | 92 |

| 6.4  | Performance of Heat 2D                                   | 93 |

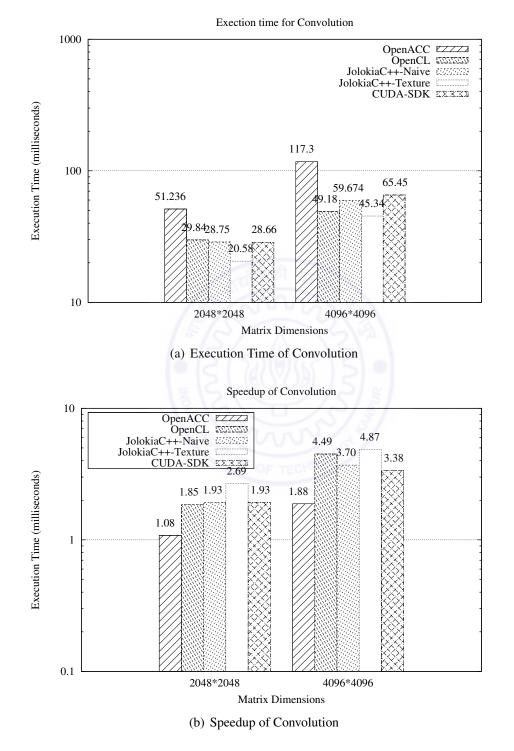

| 6.5  | Performance of Convolution                               | 94 |

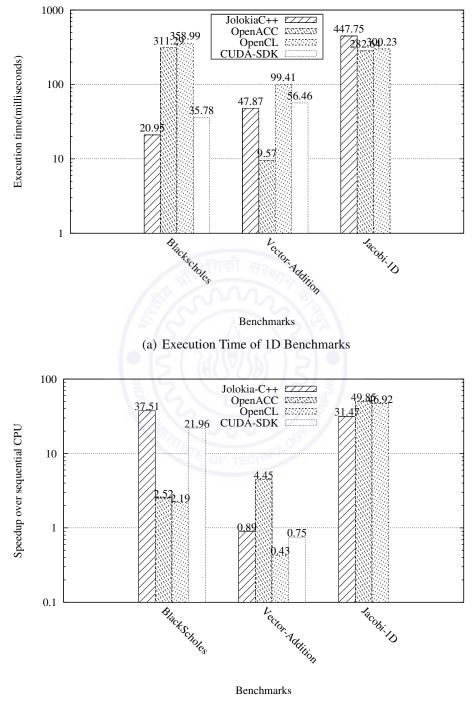

| 6.6  | Performance of 1D Benchmarks                             | 95 |

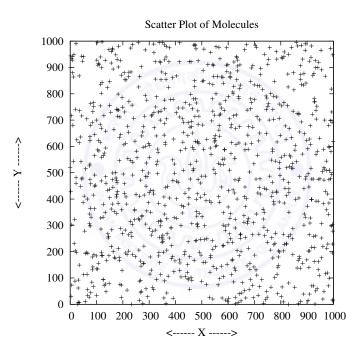

| 6.7  | Scatter plot of 1000 molecules                           | 96 |

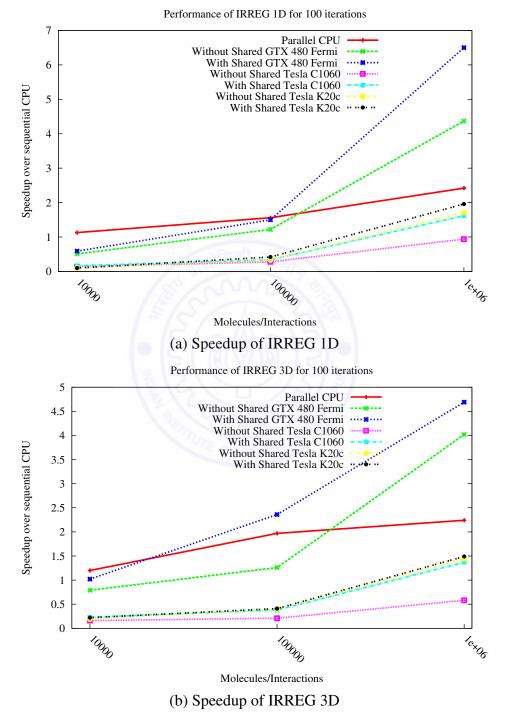

| 6.8  | Performance of IRREG kernel                              |    |

| 6.9  | Performance of MOLDYN kernel                             | 98 |

| 6.10 | Performance of NBF kernel                                | 99 |

| 6.11 | Data Transfer Overhead                                   | 00 |

# List of Algorithms

| 4.1 | Determining Block and Grid Dimension for linearized array | 43 |

|-----|-----------------------------------------------------------|----|

| 4.2 | Global Task-Level Data Flow Analysis                      | 48 |

| 4.3 | Task-Level Data Flow Variables Analysis                   | 48 |

| 4.4 | Memory Access Optimization                                | 50 |

| 5.1 | Loop Flow Analysis                                        | 62 |

| 5.2 | Global Flow Analysis                                      | 63 |

| 5.3 | Automatic Shared Memory Tiling                            | 64 |

|     | First Touch Policy                                        |    |

| 5.5 | Wavefront Generation                                      | 72 |

| 5.6 | Wavefront Regularization                                  | 72 |

| 5.7 | Intra-Loop Memory Access Mechanism                        | 74 |

| 5.8 | Lock-free Interblock Barrier                              | 76 |

# **List of Abbreviations**

| GPU     | Graphics Processing Unit                               |

|---------|--------------------------------------------------------|

| GPGPU   | General-Purpose Computing on Graphics Processing Units |

| CUDA    | Compute Unified Device Architecture                    |

| OpenACC | Open Accelerators                                      |

| OpenCL  | Open Computing Language                                |

| SM      | Streaming Multiprocessor                               |

| SP      | Streaming Processor                                    |

| SIMT    | Single Instruction Multiple Thread                     |

| DRAM    | Dynamic Random Access Memory                           |

| AST     | Abstract Syntax Tree                                   |

| BLAS    | Basic Linear Algebra Subprograms                       |

| TFG     | Task-Level Data Flow Graph                             |

| TFV     | Task-Level Data Flow Variable                          |

| AO      | Array Object                                           |

| OFG     | Operation-Level Data Flow Graph                        |

| LFV     | Loop Flow Variable                                     |

| LFG     | Loop Flow Graph                                        |

| AP      | Array Part                                             |

| FT      | First Touch                                            |

| FPGA    | Field Programmable Gate Array                          |

|         |                                                        |

## **Chapter 1**

## Introduction

Processor designers have turned towards architectures with increased degree of explicit parallelism in response to the challenges faced by frequency scaling. Today's hardware offerings range from general purpose chips with a few cores to many cores graphics processors (GPUs) that support large-scale data parallel computations. Graphics Processing Units (GPUs), with many-core architecture have led the race due to their floating point performance. However, adopting these architectures has been a process plagued with legacy issues. The problem of partitioning existing single-threaded applications to maximally utilize available multiple cores has been a challenging issue. Languages like OpenCL [11] and CUDA [2] greatly improved speed and responsiveness for a wide spectrum of applications by providing a standard interface for general-purpose programming of GPUs. However, using these languages effectively requires explicit management of numerous low-level details which involves use of communication and synchronization constructs. This burden makes GPU programming difficult and error-prone, preventing wide access to these powerful devices for most programmers. While high level abstractions serve well for parallel programming, their semantics is based predominantly on what happens in sequential architectures. As a result compilers for these languages provide limited scalability in performance for complex programming architectures like GPUs.

An alternate to writing parallel programs is to have a parallelizing compiler that can automatically parallelize sequential applications. Auto-parallelization differs from parallel programming in that the programmer does not have to worry about using parallel constructs in the program [12, 41]. It is the compiler's responsibility to take advantage of the parallelism existing in the underlying architecture. The advantage of this approach is that existing/legacy applications need not be modified, e.g. applications just need to be recompiled with a parallel compiler. Therefore, programmers need not learn new programming paradigms. However, this is achieved at the cost of reduced performance improvement.

The work presented in this thesis is based on a third approach, which is an annotation based approach. We present the design and implementation of a generic annotation based compiler framework that can be used to program GPGPUs where the programmer is only required to have a clear idea about those parts of a program that must be parallelized. We call our framework *JolokiaC++*. JolokiaC++ uses annotations to extend the C++ language to program GPUs. A JolokiaC++ programmer can exploit the parallelism of GPUs using annotations, without writing complex low level code as required by other mainstream approaches (OpenCL or CUDA). The JolokiaC++ complier translates a high-level annotated C program to efficient low-level CUDA code. This makes GPUs more accessible while effectively exploiting their computational power. We demonstrate the utility of JolokiaC++ by providing a comparison between JolokiaC++ code and CUDA code to show the ease of programming as also the performance improvement obtained when using JolokiaC++.

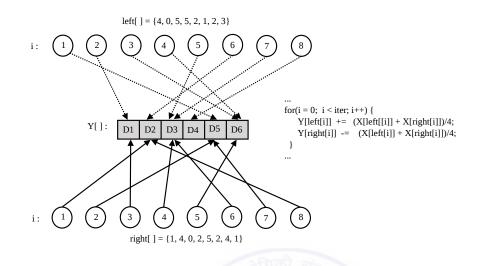

GPUs have become widely used for general-purpose computation, and have the potential to achieve high peak compute rates. This appealing property comes from the massively parallel architecture of GPUs. However, this leads to high sensitivity in their throughput to the presence of irregularities in memory access patterns in an application. Irregularities in an application may degrade GPUs performance by as much as an order of

# **1.1. KEY CHALLENGES FOR GENERAL PURPOSE PROGRAMMING ON GPU**

magnitude. When the memory access pattern is regular, the GPUs perform extremely well using high level programming models like OpenACC [10, 4]. However, a large number of interesting applications have irregular data access patterns. Efficient parallelization of codes with irregular accesses on the GPU is still a challenging problem. Hence, it is important to develop mechanisms which can help generate efficient parallel code for applications with irregular memory accesses. We overcome this problem by generating schedules which can regroup data and iterations of loop kernel in such a way that the number of consecutive independent iterations is maximized for execution on streaming multiprocessors.

# 1.1 Key Challenges for General Purpose Programming on GPU

We summarize the key challenges for obtaining high performance from general purpose GPU code as they are the main focus of our proposed framework.

#### **1.1.1 Lack of Memory Hierarchy Management support**

Performance of applications is highly dependent upon the efficient utilization of memory hierarchy. Unlike cache based systems the memory hierarchy of GPUs is under control of the programmer. GPUs use scratch-pad memory which requires explicit instructions to move data from global memory. Lack of compiler support to manage scratch-pad memory is a motivating factor to automate this process. Further, random access in irregular kernels leads to non-coalesced global access which reduces memory bandwidth utilization in GPU.

#### 1.1.2 Lack of Language Support

GPUs lack high level language support. Programmers need to know architectural intricacies to effectively utilize GPU features. We provide compile time and runtime support for a generic parallel construct like *for* in *JolokiaC++* to make it work on GPUs. We provide operators like *gpuIn* and *gpuOut* to simplify the data transfer between the CPU and GPU. In addition to this we introduce several operator annotations to guide the process of memory hierarchy optimizations.

#### 1.1.3 Thread Block Synchronization on GPU

In CUDA, \_\_\_**syncthreads()** is the barrier function which ensures proper intra-block communication. However, there is no explicit support for inter-block communication. Currently, this type of data communication occurs via global memory. It is followed by barrier synchronization via the CPU. That is, the barrier is implemented by terminating the current kernel's execution and relaunching the kernel. This is an expensive operation. To overcome this problem we use a lock-free barrier implementation for inter-block communication.

#### 1.1.4 Inadequate Parameter Modeling Support

Blocks and threads are the basic unit of execution on GPUs. However, the programmer has to experiment with a number of blocks and threads to get optimal performance. We provide annotations to model the number of threads per block to gauge the performance. To support modeling of parameters on GPU, we provide *tile* and *scratchpad* operators.

### **1.2 GPU Programming using JolokiaC++**

In this section, we illustrate the usefulness of programming with JolokiaC++ using an example.

**Example 1.1:** Listing 1.1 presents JolokiaC++ code to add two vectors, each containing 32 bit floating point numbers. A, B and C in the code are representatives for float arrays in C space. The parameters to *gpuIn* are the objects that are to be copied from CPU to GPU, while parameters to *gpuOut* are the objects to be copied from GPU to CPU. The *tile* operator provides information required for determining block and grid dimensions.

The snippet in Listing 1.2 shows the CUDA code required to perform the same task. It is also the code we expect the translator to generate while compiling the program in Listing 1.1. Notice the amount of low level detail that is hidden by the high level annotations in Listing 1.1. This illustrates the advantage of using JolokiaC++ as it allows the programmer to write simple high level code without compromising performance on a multicore architecture like GPU.

The annotations like gpuIn, gpuOut are provided by the user to assist JolokiaC++ compiler in code generation. In addition to these explicit annotations, JolokiaC++ can automatically infer information associated with array objects as implicit annotations to allow accessing array elements through primitive array types.

### **1.3 Our Contributions**

We have made the following contributions:

• We describe the design and implementation of JolokiaC++, a compiler framework to generate CUDA code from high-level language abstractions provided through implicit and explicit annotations. We explore compiler techniques to recognize high-level abstractions to exploit their semantics for parallelization.

Listing 1.1: JolokiaC++ Code for Vector Addition

```

#define N 4096

__global__ void vecAdd(int *A, int *B, int *C){

int idx = threadIdx.x + blockIdx.x * blockDim.x;

if(idx < N){

C[idx] = A[idx] + B[idx];

}

}

int main (void) {

int Host_a[N], Host_b[N], Host_c[N];

//Host array

int *Device_a , *Device_b, *Device_c;

//Device array

// Initialize Host array

// Declare and initialize grid and block dimensions

//Allocate the memory on the GPU

cudaMalloc((void **)&Device_a, N*sizeof(int));

cudaMalloc((void **)&Device_b, N*sizeof(int));

cudaMalloc((void **)&Device_c, N*sizeof(int));

//Copy Host array to Device array

cudaMemcpy(Device_a, Host_a, N*sizeof(int), cudaMemcpyHostToDevice);

cudaMemcpy(Device b, Host b, N*sizeof(int), cudaMemcpyHostToDevice);

//Make a call to GPU kernel

vecAdd <<< gridDim, blockDim>>> (Device_a, Device_b, Device_c );

//Copy back to Host array from Device array

cudaMemcpy(Host_c, Device_c, N*sizeof(int), cudaMemcpyDeviceToHost);

//Free the Device array memory

cudaFree(Device_a);

cudaFree(Device_b);

cudaFree(Device_c);

return 0;

```

#### Listing 1.2: CUDA Code for Vector Addition

- We present a compiler system extension to automate parallelization of data parallel regular kernels on GPUs. We introduce a set of automatic optimizations for GPU architectures, that includes memory optimizations that improve locality, reduce bank conflicts, and permit vectorization. The framework analyzes the operators supported by the language, identifies the off-chip memory access patterns, and optimizes the memory accesses through vectorization and coalescing to achieve high data access bandwidth. These optimizations are implemented in JolokiaC++.

- We present a compiler and runtime system extension to automate parallelization of irregular kernels with subscripted subscripts for execution on GPUs. We use a combination of compile time analysis and composition of runtime data and iteration reordering transformations to optimize the performance of irregular kernels with irregular memory accesses on GPUs.

- We evaluate the performance of the code generated by JolokiaC++ for kernels like Blackscholes, Matrix-Vector multiplication, Matrix-Matrix multiplication, Jacobi 1D and 2D, Heat 2D, Vector Addition and Convolution. We also evaluate the effectiveness of the framework for irregular memory access kernels: IRREG, MOLDYN and NBF. The performance of the kernels is presented both in terms of execution time and speedup. The speedup of optimized JolokiaC++ implementation for regular kernels ranges from 0.89 4242.21 as compared to OpenCL which ranges from 0.42 571.59 and OpenACC which ranges from 1.08 526.08. The speedup of shared memory composition of irregular kernels ranges from 0.59 11.23 as compared to the composition without shared implementation which ranges from 0.5 7.74. The speedup of almost all the regular kernels using optimized JolokiaC++ is better when compared with OpenCL and OpenACC implementations. The shared memory composition of the inspector/executor mechanism for irregular kernels performs reasonably well when compared with a sequential CPU based implementa-

tion and without shared composition. The speedup of optimized JolokiaC++ when compared with hand-written OpenCL and OpenACC implementation for regular kernels ranges from 0.52 - 17.13 and 0.199 - 79.56 respectively.

### **1.4 Organization of the Thesis**

The rest of the thesis is organized as follows. Background and Related work is discussed in Chapter 2. Chapter 3 describes the design and implementation of the language for annotations in JolokiaC++. Chapter 4 describes how to use language construct for regular kernels. It also discusses the optimizations supported by the framework. In Chapter 5, we describe the optimizations to improve the performance of irregular kernels with indirect memory accesses. In Chapter 6, we show the effectiveness of our approach on various benchmark codes and provide results for kernels with regular and irregular accesses. Chapter 7 concludes the thesis and gives directions which can be pursued to further improve GPGPU programming.

## **Chapter 2**

## **Background and Related Work**

Multi-core and many-core architectures have emerged as an elegant solution to meet the increased computational requirements of current applications while avoiding problems like chip overheating. The GPU is probably the dominant massively parallel architecture that is available. Nevertheless, taking advantage of this architecture has been a major concern for traditional serial programmers. Writing parallel codes for existing/new problems to work on current GPUs is a non-trivial task. One of the most difficult tasks in moving from serial to parallel programming is in fact adopting a completely new mindset. CUDA (Compute Unified Device Architecture) programming models high performance implementations for general purpose computational tasks on NVIDIA GPUs. However, manual development of optimized CUDA code for efficient data access is non-trivial. Hence, source to source translation of sequential programmers. In this chapter we present aspects which will help understand our work and relate it to other work in the field.

### 2.1 Basic Terms

We define some basic terms used throughout the thesis.

**Definition 2.1. (Kernel)** A function loaded onto the device (GPU) by the host (CPU) command is called a *kernel*.

**Definition 2.2.** (Annotation) An *annotation* in the JolokiaC++ programming language is a form of syntactic metadata used to annotate variables, operators, and functions.

**Definition 2.3.** (**Pragma**) A *pragma* is an explicit annotation interpreted differently in order to address the requirements of GPU hardware.

**Definition 2.4.** (Stencil Codes) *Stencil Codes* are computations that involve repeated updating of values connected with points on a multi-dimensional grid, utilizing only the values in a set of neighboring points.

### 2.2 Background

As our work develops annotation based compiler framework for GPUs, and generates CUDA code for such devices, we discuss the GPU parallel computing architecture and CUDA programming model in detail in this section.

#### 2.2.1 GPU Parallel Computing Architecture

The GPU parallel computing architecture contains a set of multiprocessors. Each streaming multiprocessor (SM) contains a set of processing cores called streaming processors (SPs). Fig. 2.1(a) shows the GPU parallel computing architecture with different memory spaces: global memory, shared memory, constant cache, texture cache, and registers. The off-chip global memory is a large memory and has very high latency. The shared memory is an on-chip memory present in each SM and is organized into banks. When multiple addresses belonging to the same bank are accessed at the same time, it results in bank conflict. Each SM has a set of registers associated with it. The constant and texture memories are read-only regions in the global memory space and they have on-chip read-only caches. Accessing constant cache is faster, but it has only a single port and hence it is beneficial when multiple processor cores load the same value from the cache. Texture cache has higher latency than constant cache, but it does not suffer greatly when memory read accesses are irregular and it is also beneficial for accessing data with spatial locality.

(a) GPU Parallel Computing Architecture

(b) CUDA Programming Model

Figure 2.1: CUDA Parallel Computing Architecture and Programming Model

#### 2.2.2 Execution Model

The parallel portions of an application are executed on the device (GPU) as kernels, with one kernel executed at a time. A CUDA kernel launches a grid of thread blocks (as shown in Figure 2.1(b)), a group of threads that should be executed concurrently. Each thread block consists of several warps, which are much smaller groups of threads. A warp is the smallest unit of hardware execution. The SM executes instructions from a warp in an SIMT (Single- Instruction Multiple-Thread) fashion. In SIMT execution, a single instruction is fetched and all the threads in the warp execute the same instruction in lockstep, except when there is control divergence.

#### 2.2.3 CUDA Programming Model

CUDA is NVIDIA's parallel computing architecture for GPUs. It is an interface which enables programmers to access the highly parallel hardware of programmable GPUs. CUDA is an extension of the C programming language, with the CUDA runtime library providing a collection of routines for device memory management, host-device stream synchronization, and execution control functions (among others). CUDA is a data parallel SIMT (Single Instruction Multiple Thread) architecture, in which the same programmer defined kernels execute on all launched threads. These threads are launched in batches of blocks and grids, where blocks are collections of threads and grids are collections of blocks.

#### **Kernel Performance Tuning**

When all threads of a warp execute a load, if all accessed locations fall into the same section, only one DRAM request will be made and the access is fully coalesced. When the access locations spread across burst section boundaries, coalescing fails, multiple DRAM requests are made and the access is not fully coalesced. Efficient use of global memory (DRAM) bandwidth is one of the important performance considerations for massively parallel processors.

#### 2.3 Related Work

GPUs are widely used for general-purpose computation and have the potential to achieve high peak compute rates. Programming models such as NVIDIA's Compute Unified Device Architecture (CUDA) [2, 3] and Khronos Group's Open Compute Language (OpenCL) [11, 35] facilitate general purpose programming for GPUs through APIs that expose the low-level details of the device architecture to the programmer. The programmer is expected to manually tune low-level code for a specific device in order to fully exploit its processing capability. On the other hand, OpenACC [10, 4] provides high level abstractions for accessing GPUs but it is unable to give good gains for codes with irregular memory access patterns. Rapidmind [58] is a parallel development framework that allows the user to write parallel programs using standard C++ language. The framework uses dynamic compilation to execute the program in parallel and targets x86, Cell BE and GPGPUs. PeakStream [53] is a parallel development framework similar to RapidMind. PeakStream programs are compiled into an intermediate language using a custom compiler and then just-in-time compiled at execution time. Both, RapidMind and PeakStream are not publicly available.

Sarkar et. al. [68] describes a matrix and non-matrix based generic framework for representing iteration-reordering transformations. Li et. al. [46] presents a transformation framework which performs A-transformations like permutation, skewing and reversal, as well as a transformation called loop scaling. An algebraic representation based unified data and control transformation for distributed shared memory machines is presented by Cierniak et. al. [25]. The advances in automatic parallelization and optimization of programs are to large extent based on the use of polyhedral model [19, 32, 21]. Baskaran et. al. [16, 15] gave a polyhedral model based compiler framework for affine loops. Their framework performs an empirical search for determining best loop transformation parameters, which includes loop tiling sizes and unrolling factors.

Polyhedral Parallel Code Generation (PPCG) for CUDA with multilevel tiling strategy and a code generation scheme for the parallelization and locality optimization of imperfectly nested loops is introduced by Verdooaege et. al. [74]. In order to overcome the load imbalance which may occur due to pipeline fill-ups and drain delay in GPUs, two new parallelism exposing transformations are proposed by Di et. al. [30]. An annotation based CUDA-free interface to implement stencil methods on GPU hardware is introduced by Unat et. al. [73]. Meng et. al. [49] presents a data-flow driven GPU performance projection for multi-kernel transformations. The transformation framework requires users to provide CPU code skeletons for a sequence of parallel loops. The framework can then automatically identify opportunities for multi-kernel transformations and data management. Majeti et. al. [47] presents a compiler-driven data-layout transformation framework for heterogeneous platforms. The data layout framework is integrated with the data parallel construct, forasync of Habanero-C, and enable the same source code to be compiled with different data layouts for various architectures. The framework requires the programmer or an auto-tuner to provide a schema of the data layout.

Programming Integrated Parallel System (PIPS) [8], an automatic parallelization system, can be used for source to source program optimization, program compilation, automatic parallelization etc. PIPS accepts programs written in C or Fortran77. It supports analysis techniques such as data flow, control flow, inter procedural analysis and dependence analysis with support for generating code for multiple architectures. Ongoing work in PIPS includes adding support for modern frameworks such as CUDA and OpenCL and inclusion of programming languages like Fortran90/95 and C99. These tools aim at simplifying the task of extracting parallelism for the programmer without compromising the maximum achievable performance gain. These tools work well for affine array access patterns with well understood semantics of popular benchmarked code.

OpenACC extends the familiar face of OpenMP pragma programming to encompass co-processors. It is a set of directive-based extensions to C, C++ and Fortran that allows code with annotations for offloading from a CPU host to an attached accelerator. When using OpenACC, the programmer has to manually annotate the source code with some pragmas that expose parallelism and might steer some data mapping. The PGI compiler then generates CUDA code for the GPU. The performance of the resulting mapping depends both on the quality of the code generated by the tool and the ability of the programmer in setting all the required pragmas. The annotations supported in OpenACC are explicit pragma based annotations. On the other hand, the annotations in JolokiaC++ include both explicit and implicit annotations. The implicit annotations are designed to exploit fine grain parallelism using operation-level data flow analysis. The explicit an-

```

{

#pragma acc region if(accelerate)

{

#pragma acc loop independent

for (int i = 0; i < N; i ++) {

#pragma acc loop independent

for (int j = 0; j < N; j ++) {

float sum = 0;

#pragma acc loop seq

for (int k = 0; k < N; k ++) {

sum += A[i * N + k] * B[k * N + j];

}

C[i * N + j] = sum;

}

}

}

```

Listing 2.1: Code snippet of Matrix Multiplication using OpenACC

notations in JolokiaC++ work at coarser level using task-level data flow analysis. Code Listing 2.1 and 2.2 shows the code snippet for Matrix multiplication using OpenACC and JolokiaC++ respectively.

CUDA-lite, an annotation based tool to automatically generate CUDA code from given annotated ANSI C code is presented by Ueng et. al. [71]. The annotations developed in the tool are complex and difficult to use. One of main reasons behind this is the fact that compiler analysis is not integrated in the tool. Samadi et. al. [67] proposed an adaptive input aware compilation system, called Adaptic, which automatically generates optimized CUDA code for a wide range of input sizes and dimensions from a high-level algorithmic description. The compiler framework proposed by Yang et. al. [76] optimizes GPGPU programs using a set of novel compiler techniques to improve GPU memory usage and distribute workload in threads and thread blocks. A mathematical model to capture and categorize memory access patterns of affine loops to improve the performance of GPU memory subsystem is presented by Jang et. al. [40]. Oancea et.

```

void matrix_mult(f64Array &A, f64Array &B, f64Array &C) {

f32Scalar pval;

_for(int i = 0; i < N; i++)

_for(int j = 0; j < N; j++) {

pval += aview(A, N, i, row) * aview(B, N, j, column);

C(i,j) = pval;

}

#pragma jolokia gpuIn(A,B,C) gpuOut(C) tile(16,16,1)

scatchpad(A,16,16,1) scatchpad(B,16,16,1)

matrix_mult(A,B,C);</pre>

```

Listing 2.2: Code snippet of Matrix Multiplication using JolokiaC++

al. [52] proposed a fully automatic approach to loop parallelization using a novel logical inference technique. An annotation guided dynamic compilation is presented by Grant et. al. [34]. A work on annotating user defined abstraction for enforcing traditional compiler optimizations is presented by Quinlan et. al. [55]. Broadway compiler [37] performs high-level semantic encapsulation of PLAPACK library functions. A new programming interface called OpenMPC is proposed by Seyong et. al. [44], to provide an abstraction to the complex CUDA programming model. Further, to overcome some of the inefficiencies of the original OpenMPC tuning scheme a new tuning strategy, called Modified IE (MIE) is proposed by Sabne et. al. [64].

Unlike the existing approaches, we present a novel annotation based compiler framework JolokiaC++, that has the potential to accomplish high performance for existing/new legacy codes to work on the GPU. A JolokiaC++ programmer can exploit GPU parallelism using annotations, without writing complex low level code as required by other mainstream approaches (OpenCL or CUDA). The JolokiaC++ complier translates a highlevel annotated C++ program to efficient low-level CUDA code. This makes GPUs more accessible while effectively exploiting their computational power.

Compile time data dependence analysis of loops accessing subscripted arrays is not

always adequate to exploit hidden parallelism that may manifest itself only at runtime. Traversing data dependences at run-time is necessary for some run-time reordering transformations. Taking this into consideration, a formal composition of runtime data and iteration reordering transformation at compile time to improve cache performance is given by Strout et. al. [69]. Irregularities in code have been widely studied for high performance computing on General-Purpose Graphics Processing Units(GPGPUs or GPUs for short) [45, 76, 78]. A considerable amount of research to find efficient ways for the compile and run-time support based on the inspector-executor technique is developed by Das et. al.[28]. Researchers have developed run-time data dependence analysis to handle non-affine memory references [54].

Saltz. et. al. [65, 27] describe a set of index set transformations that can efficiently solve a form of irregular problems that are start-time schedulable for distributed memory machines. Parallelization of Fortran and C programs with irregular access patterns is supported by the CHAOS [1] runtime library which is specifically targeted towards distributed memory systems that supports message passing or distributed shared memory. Software schemes presented in [50, 60, 62, 59] analyze dependence structure of the code accessing subscripted subscripts at runtime and try to run parts of it in parallel protected by synchronization. Rus et. al. [63] take this further by adding the ability to traverse all data dependences at run-time if necessary. They perform a hybrid (static and dynamic) data dependence analysis inter-procedurally. [48, 31] contributes in improving the memory hierarchy performance for irregular applications using data and computation reordering. A new approach of slice classification for automatic generation of optimized parallel code for N-body simulations is covered in [29]. Other software schemes [36] speculatively run the code in parallel and later recover if a dependence violation is detected.

The massive data parallelism offered by recent architectural enhancements in GPU's comes at the cost of a complex programming model. Researchers have developed several

strategies for overcoming the compilation challenges on the GPU. An auto-parallelization framework for optimization of Affine loop nests on GPGPUs is presented by Baskaran et. al. [17]. The C-to-CUDA by Baskaran et. al. [17], is the first automatic source-to-source compiler based on PLuTo [20]. A preliminary result of an annotation based automated tool for reducing GPU programming complexity is presented by Ueng et. al. [71]. Compiling irregular applications on a cell broadband processor using the inspector-executor approach has been presented by Bhatotia et. al. [18]. Strout et. al. [69, 43] presents the Sparse Polyhedral Framework (SPF) for generating efficient inspector and executor code for multi-core CPUs. The study of an irregular application's implementation on a graphics pipeline is covered in [72]. An extension to StarSs programming model for platforms with multiple GPUs proposed by Ayguade et. al. [14] provides an alternative programming model for exploiting functional parallelism based on building a task dependence graph at run-time with the help of explicit annotations. A comparative study of data-driven and topology-driven implementations of graph algorithms is given by Nasre et. al. [51]. They also devised hybrid approaches that combine both the techniques which outperform each of the two individually.

A speculative parallelization based mechanism to execute iterations of DOACROSS loops on GPU is described by Feng et. al. [33]. In their approach, the misspeculation check is also performed on the GPU. In case of misspeculation, the incorrectly executed iterations are identified and executed on the CPU if there are other misspeculated iterations depending on them; otherwise they are executed again on the GPU. Paragon [66] identifies possibly data parallel loops and runs them speculatively on the GPUs and also runs them sequentially on the CPU. In case of misspeculation, the data generated by the GPUs is ignored and the data generated by the CPU is used. Anantpur et. al. [13] work differs from both these approaches as they do not execute any iterations speculatively on the GPU. In their approach, the loop is executed sequentially on the CPU while the dependence computation is going on, so that in case if the number of levels in the loop is too

high to benefit from running on the GPU, the GPU run can be stopped and the data from the CPU run can be used. Kim et. al. [42] used a profiling based approach to speculatively parallelize loops on a cluster. It tries to optimize the communication and validation overheads. Jablin et. al. [39] presents an inspector executor based approach to handle GPU-CPU communication. However, we use an inspector executor based approach to handle the memory hierarchy of the GPU.

We present a compilation framework for applications with irregular accesses which can simplify general purpose programming of such applications on a GPU. We develop a framework which allows high level specification and control of computational granularity along with a good load balancing mechanism for scheduling and mapping of iterations and data respectively. We used the concept of dynamic scratch pad memory management which is well-known in the context of embedded systems [70] to manage the shared memory of a streaming multiprocessor. Prior work on run-time parallelization on multiple processors includes data and iteration partitioning for irregular applications [61]. In contrast to these, the work presented here extends the compiling support for the GPU in line with the inspector-executor paradigm. We propose the use of an automatic code generator for memory communication and run-time parallelization to deal with irregular kernels on the GPU.

## **Chapter 3**

## Language Design

Moores law states that the number of transistors on a chip will double every 18 to 24 months, and this has been true for the last 40 years. It appears to continue for another decade. But Moores observation has been simplified to mean a doubling of performance every 18 to 24 months, and that too has been true until now, but not anymore. This resulted in transition to multi and many core processors. As a result, high performance computing will have to make much more effective and efficient use of high degrees of parallelism available through multiple cores and GPU architectures. This requires the development of more sophisticated application code. The complex programming model of GPUs greatly increases the compile-time optimization difficulties for applications. While high level abstractions serve well for parallel programming, they are usually ill suited for the complex programming model offered by GPUs. As a result compilers for such languages provide limited scalability in performance.

In recent years, OpenMP has transitioned from being solely focused on shared-memory systems to include accelerators, embedded systems, multicore and real-time systems. OpenMP 4.0 [5, 6] includes support for accelerators, SIMD constructs to vectorize both serial as well as parallelized loops, error handling, thread affinity, and tasking extensions.

OpenMP 4.0 API provides several extensions to its task-based parallelism support.

Figure 3.1: Compilation Framework of JolokiaC++

Tasks can be grouped to support deep task synchronization and task groups can be aborted to reflect completion of cooperative tasking activities such as search. Task-to-task synchronization is also supported through the specification of task dependency. Our approach in task-level data flow analysis is very similar to that supported in OpenMP 4.0, however, it is adapted to the context of our language. And similarly, the operation-level data flow graph is also a data flow graph but at the level of operations (statements) inside a task. So, the two graphs are at different granularities.

In this Chapter, we describe the design and implementation of a generic annotation based compiler framework that can be used to program GPGPUs. The programmer is only required to have a clear idea about the parts of programs that will be parallelized. and requires very little knowledge of hardware architecture, and can gauge the performance to an acceptable level on GPUs. Unlike the existing approaches, JolokiaC++ uses annotations for extending C++ to program GPUs. A JolokiaC++ programmer can exploit the parallelism of a GPU using annotations and without writing complex low level code as required by other mainstream approaches like OpenCL or CUDA. JolokiaC++ complier translates high-level annotated C program to efficient low-level CUDA code. This makes GPUs more accessible while effectively exploiting their computational power.

### 3.1 Design of JolokiaC++ Framework

JolokiaC++ enhances C++ with an annotation language to enable the user to write GPU programs without worrying about the low level details of the underlying architecture. The high level annotation language allows a user to express data parallelism by specifying operations at the aggregate data collection level. The flow of control in the program for dynamic data types is made explicit at compile time.

Figure 3.1 shows the high level compilation framework implemented for JolokiaC++. The application developer writes a program in JolokiaC++ using explicit annotations specified through pragmas. These annotations provide implementation specific information about the language extensions to the compiler in a simple declarative manner. Further, implicit annotations are added to the language to provide high level abstractions for vector and scalar accesses. The semantic interpretation for these implicit annotations (associated with array objects) allows accessing array elements through primitive array types. We also introduce a way to specify the range of elements of the collection object by means of the *tile* operator. The *tile* operator enables automatic code generation for inter-thread memory access, thereby exploiting parallelism within a kernel by spawning threads/thread blocks.

We use a source-to-source compiler infrastructure, ROSE [57], to explore compiler techniques to recognize high-level abstractions and to exploit their semantics for automatic parallelization. Our compiler framework takes as input annotated C code that is functionally correct, but does not include any lower level device-specific performance optimizations. The framework analyzes operator annotations to determine off-chip memory access patterns, and optimizes these accesses through vectorization and coalescing to achieve high data access bandwidth.

In summary, the process of translation involves interpreting the semantics of the predefined operators and data types supported by the annotation language and generating the corresponding code for CUDA enabled GPUs using the hints provided through explicit

Figure 3.2: Translation spaces in JolokiaC++

annotations.

### 3.1.1 JolokiaC++ Programming Model

JolokiaC++ source code is intended to be compiled to CUDA, so that the resulting executable code runs on a CUDA enabled GPU. The JolokiaC++ virtual machine provides sufficient abstraction to the programmer to hide the communication details of the programming model. It provides unified view of different address spaces associated with CPU and GPU. This allows the programmer to focus on algorithms rather than dealing with the communication intricacies involved in using different memory spaces required for the execution of program on GPU.

To support this model JolokiaC++ introduces three spaces: 1) Jolokia space 2) C space and 3) Device space. These are depicted in Figure 3.2. Different views for scalar array

Figure 3.3: Translation of JolokiaC++ code

objects are created in different spaces as per the aliasing information provided through annotations. The use of a simple scalar object corresponds to the creation of a thread local variable in the kernel, resulting in use of streaming multiprocessors' registers. Pragmas are preprocessed to generate the annotations required for creating an alias on the device. The process of translation is shown in Figure 3.3.

### 3.1.2 JolokiaC++ Annotations

Explicit annotations exist in the input program in the form of data annotations, operator annotations or as pragma specifiers. Implicit annotations are implemented to simplify the translation of explicit annotations. To recognize annotations, we build an annotation grammar and the corresponding high-level ASTs using ROSE. This grammar is similar to the base language grammar. We added constructs to represent specific user-defined functions, data-structures, user-defined types etc in the grammar. The compiler recognizes the annotations within an application in much the same way it recognizes the syntax of the base language.

Listing 3.1: Data Annotation Example

```

void SAXPY(f64Scalar &A, f64Array &X, f64Array &Y, f64Array &S){

int xlen = X.length;

double *s = S.get_pointer();

double *x = X.get_pointer();

double *y = Y.get_pointer();

double a = A.get_data();

...

for (i = 0; i < xlen; i++){

s[i] = a * x[i] + y[i];

}

}</pre>

```

Listing 3.2: Semantic Interpretation of Statement S1 in Listing 3.1

#### **3.1.2.1 Data Type annotations**

Explicit data annotations like f32Array, f64Array, f32Scalar provide data abstraction for vectors and scalars of primitive type. The implicit annotations *array\_view* and *is\_array* are associated with data annotations. We associate attributes like *dimension*, *length* and *element* using implicit annotation *array\_view* to create a view of an array in C space. The scalar variable *dimension* holds the dimension of an array. The attributes *length* and *element* are collection variables. The attribute *length* is used to hold the length of an array in each dimension. Every occurrence of f32Array object is replaced by an *element* which is indexed by integer parameters. This annotation replaces object reference in Jolokia space to arrays in C by making use of the view created in C space. The *is\_scalar* annotation is used to holds the value of scalar variable. The annotations for scalar data types is created in order to provide flexibility in describing operator annotations.

**Example 3.1:** To exemplify the role of explicit data annotations, consider a JolokiaC++ code snippet given in Listing 1. Here **X**, **Y**, and **S** are declared as f64Array type variables and **A** is declared as f64Scalar type variable. Semantically, each array object declared in this code is interpreted as a single *dimensional* array of *length* N which can store N 64-bit floating point *elements*. Based on the number of parameters passed to an array object, the dimensions and the lengths corresponding to these dimensions are determined for each dynamically created array of appropriate type (double for this example). For the scalar object **S** in the code snippet, a 64-bit floating point (double) scalar variable is created.

To illustrate the significance of introducing scalar types, let us consider the statement S1 in Listing 1. Here, **a** is the scalar element (*selem*) associated with **A**. Also, **x**, **y** and **s** are the dynamic arrays associated with **X**, **Y** and **S** respectively. The semantic interpretation of statement S1 is as shown in Listing 3.2. In order to interpret operations applied between scalar and vector types (e.g \* operation between **A** and **X**) we introduce data type annotations for scalar variables. This allows us to carry out various operation

| Annotation | Semantics                                                        |

|------------|------------------------------------------------------------------|

| dalloc     | Allocates memory on GPU space for the object passed as param-    |

|            | eter to the annotation.                                          |

| dcpy       | Annotation to copy data from CPU space to GPU space for the      |

|            | object passed as parameter to it.                                |

| on_entry   | Returns a device pointer associated with object passed as param- |

|            | eter to the annotation.                                          |

| on_exit    | Annotation to copy data from CPU space to GPU space for the      |

|            | object passed as parameter to it.                                |

Table 3.1: CPU-GPU Memory Space Management Annotations

between scalar and array type variables.

#### **3.1.2.2 Operator annotations**

Operator annotations describe the semantics of the functions that operate on the data abstractions used for creating scalar and vector data types. For every function call that follows a Jolokia pragma, a function operator entry is created in an annotation file. The *on\_entry* and *on\_exit* annotations are placed within the function operator for each object instance passed to the *gpuIn* and *gpuOut* parameter of a Jolokia pragma. The *gpuIn* pragma specification provides information regarding the array object instance being read by the kernel function. Similarly, *gpuOut* is used for providing information regarding the writing of data into the array object instance. Using this information, we build a graph based on the operations performed on objects of array type. This graph is similar to an abstract syntax tree in a compiler. The graph provides sufficient information to optimize the intermediate representation of the code for the target architecture.

The *scratchpad* annotation is provided to specify the size of shared memory and to restructure memory access for coalesced global memory access. The *aview* operator annotation provides linearized access to multi-dimensional arrays for vectorization. The *stride* and *shift* operators allow the programmer to specify different memory access patterns. The *modify\_array* annotation is implemented to allow modifications to an alias

Listing 3.3: Example for gpuIn, gpuOut and Tile annotation

created in C space. The *alias* annotation describes aliasing relationships between the inputs and results. The *on\_entry* annotation allows retrieval of an object's view in GPU space. The *on\_exit* annotation is concerned with reflecting the changes made in the GPU space to an array created in C space. The *kernel* annotation is provided for composition of GPU kernels in the code. The *tile* annotation provides sufficient information required to launch a kernel on the GPU. The implicit CPU-GPU space mapping annotations and their semantics is presented in Table 3.1.

**Example 3.2:** In the example shown in Listing 3.3, we illustrate the use of *gpuIn* and *gpuOut* annotations associated with jolokia pragma. Each array type object can either have associated dynamic arrays, one on device (GPU) and one on host (CPU) each or it can have an associated dynamic array only on host. The dynamic array associated with objects **A**, **B** and **C** are required for invoking the device kernel associated with add function. This requires insertion of *on\_entry* annotation for each array object within the

```

void stencil(f32Array &A, f32Array &B){

B = shift(A,-1) + shift(A,0) + shift(A,1)

}

```

#### Listing 3.4: Shift Operator Example

```

void stencil(f32Array &A, f32Array &B){

for(i = 0; i < len; i++){

B[i] = A[i-1] + A[i] + A[i+1];

}

}</pre>

```

Listing 3.5: Semantic Interpretation of Shift Operator

function annotation. This would allow us to obtain device pointer associated with the every dynamic array existing on CPU. The result of vector addition stored in the device array associated with  $\mathbf{A}$  is returned back to the CPU by passing it as a parameter to *gpuOut*.

**Example 3.3:** Listing 3.3 also demonstrates the use of *tile* annotation associated with jolokia pragma. It is applied to define parameters (grid and block dimension) required to launch the kernel on the GPU.

**Example 3.4:** Listing 3.4 illustrates the use of shift operator. Its semantic interpretation on CPU space is shown in Listing 3.5.

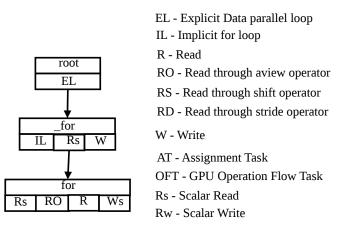

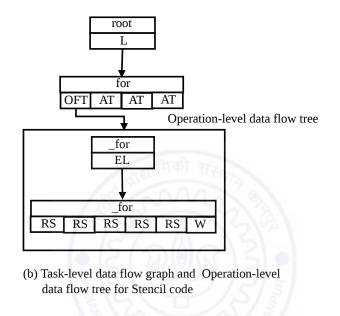

### 3.1.3 Task-Level Data Flow Graph

Before describing the task-level data flow graph we present an example to motivate its need. Listing 3.6 presents a snippet of JolokiaC++ implementation of data parallel code. A naive translation that does not take into account the flow of data among the statements executed on CPU and on GPU is presented in Listing 3.7. In this code the unnecessary *cudamalloc* and *cudamemcpy* calls are generated which could be inefficient or incorrect. Further, what we would like to generate the code similar to what a CUDA expert would

write. A sample of such a code is shown in Listing 3.8. To do so, we need to analyse the flow of data in the JolokiaC++ program. This is done using the task-level data flow graph as defined next, after a few helper definitions.

**Definition 3.1.** (**GPU Task**) The Jolokia pragma along with the function call that immediately follows it is defined as a GPU task.

**Definition 3.2.** (**CPU Task**) Maximal set of consecutive statements which do not contain any jolokia pragma is a CPU task. This set of statements are targeted for execution on the CPU.

**Definition 3.3.** (Task-Level Data Flow Graph) Let  $\mathcal{P}$  be a JolokiaC++ program. The nodes in a task-level data flow graph of  $\mathcal{P}$  represents CPU or GPU tasks, and the edges represent flow of data from one node to another. An edge from node  $n_1$  to node  $n_2$  exists in the task-level data flow graph of  $\mathcal{P}$ , if  $n_1$  follows  $n_2$  in program order. Note that, even though a GPU task is a function call, it represents a single node in the task-level data flow graph.

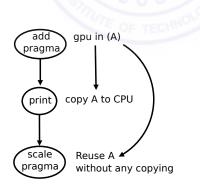

**Example 3.5:** The task-level data flow graph for the JolokiaC++ code given in Listing 3.6 is shown in Figure 3.4. Here, *add pragma* and *scale pragma* nodes correspond to *add* and *scale* functions that immediately follow a jolokia pragma. A node for the CPU task *print* also exists in the graph. To analyse the body of the function corresponding to a GPU task we use an operation-level data flow graph as described in the next section.

### **3.1.4 Operation-Level Data Flow Graph**

The operation-level data flow graph for a GPU task function  $\mathcal{F}$  is a graph where nodes correspond to the statements of  $\mathcal{F}$ , and the edges represent flow of data from one node to other. We use operation-level data flow graph to analyze the operations performed on

```

/* Task definition */

void add(f64Array &A,f64Array &B,f64Array &C){

A = B + C

}

void scale(f64Array &A, f64Scalar &S) {

A = S * A;

}

main() {

. . .

/* Task call site */

#pragma jolokia gpuIn(A,B,C) gpuOut(A) tile(BLK1,1,1)

add(A,B,C); /* GPU Task */

A); /* CPU Task */

print(A);

#pragma jolokia gpuIn(A,S) gpuOut(A) tile(BLK2,1,1)

scale(A,S); /* GPU Task */

}

```

Listing 3.6: Task-Level Data Flow Example

Figure 3.4: Task-Level Data Flow Graph

```

__global__ void add(float *A, float *B, float *C)

int idx = threadIdx.x + blockIdx.x * blockDim.x;

if(idx < N){

A[idx] = B[idx] + C[idx];

}

}

__global__ void scale(float *A, float S)

int idx = threadIdx.x + blockIdx.x * blockDim.x;

if (idx < N) {

A[idx] = S * A[idx];

}

}

cudaMalloc((void **)&Device_A, N*sizeof(float));

cudaMalloc((void **)&Device B, N*sizeof(float));

cudaMalloc((void **)&Device_C, N*sizeof(float));

//Copy Host array to Device array

cudaMemcpy(Device_A, Host_A, N*sizeof(int),

cudaMemcpyHostToDevice));

cudaMemcpy(Device_B, Host_B, N*sizeof(int),

cudaMemcpyHostToDevice));

cudaMemcpy(Device_C, Host_C, N*sizeof(int),

cudaMemcpyHostToDevice));

//Make a call to GPU kernel

add<<<qridDim, blockDim>>>(Device_A, Device_B, Device_C);

//Copy back to Host array from Device array

cudaMemcpy(Host_A, Device_A, N*sizeof(float),

cudaMemcpyDeviceToHost);

for(i = 0; i < N; i++)

printf("%f",Host_A[i]);

cudaMalloc((void **)&Device_A, N*sizeof(float));

cudaMemcpy(Device_A, Host_A, N*sizeof(int),

cudaMemcpyHostToDevice));

//Make a call to GPU kernel

scale<<< gridDim, blockDim>>>(Device_A, host_S);

//Copy back to Host array from Device array

cudaMemcpy(Host_A, Device_A, N*sizeof(float),

cudaMemcpyDeviceToHost);

//Free the Device array memory

cudaFree(Device_A);

cudaFree(Device_B);

cudaFree(Device_C);

```

Listing 3.7: A Naive Translation of Task-Level Data Flow Example

```

__global__ void add(float *A, float *B, float *C)

int idx = threadIdx.x + blockIdx.x * blockDim.x;

if(idx < N){

A[idx] = B[idx] + C[idx];

}

}

__global__ void scale(float *A, float S)

int idx = threadIdx.x + blockIdx.x * blockDim.x;

if(idx < N){

A[idx] = S * A[idx];

}

}

cudaMalloc((void **)&Device A, N*sizeof(float));

cudaMalloc((void **)&Device_B, N*sizeof(float));

cudaMalloc((void **)&Device_C, N*sizeof(float));

//Copy Host array to Device array

cudaMemcpy(Device_A, Host_A, N*sizeof(int),

cudaMemcpyHostToDevice));

cudaMemcpy(Device_B, Host_B, N*sizeof(int),

cudaMemcpyHostToDevice));

cudaMemcpy(Device_C, Host_C, N*sizeof(int),

cudaMemcpyHostToDevice));

//Make a call to GPU kernel

add<<<gridDim, blockDim>>>(Device_A, Device_B, Device_C);

//Copy back to Host array from Device array

cudaMemcpy(Host_A, Device_A, N*sizeof(float),

cudaMemcpyDeviceToHost);

for(i = 0; i < N; i++)

printf("%f",Host_A[i]);

//Make a call to GPU kernel

scale<<< gridDim, blockDim>>>(Device A, host S);

//Copy back to Host array from Device array

cudaMemcpy(Host_A, Device_A, N*sizeof(float),

cudaMemcpyDeviceToHost);

//Free the Device array memory

cudaFree(Device_A);

cudaFree(Device_B);

cudaFree(Device_C);

```

Listing 3.8: Translation after Task-Level Data Flow Analysis

objects of scalar and vector type. The analysis involves identifying the sequence of statements that are called when instantiation of threads happen within a **subtask**. A subtask corresponds to the subset of tasks targeted for execution on a streaming multiprocessor of a GPU. It represents one iteration of the innermost implicit for loop indicated through operator annotation. This operation flow analysis helps us to exploit data parallelism for threads within a subtask.

## Chapter 4

# **Regular Applications**

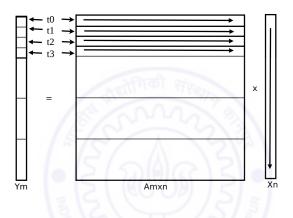

Memory accesses which are linear combinations of loop index variables are quite common in a variety of applications like dense-matrix linear algebra, finite-difference PDE solvers, image processing and scans/joins in relational databases. Array references with such access are called affine array accesses. Loops with affine array accesses are a natural consequence of the emergence of massively multi-threaded data-parallel computing platforms. Today's GPU computing platforms are designed with a heterogeneous memory architecture comprising multiple memory spaces where each space has specific characteristics. Mapping data arrays to the most appropriate memory space, based on their associated memory access patterns, can have a huge impact on overall performance.

We present a technique that uses operator annotations to systematically characterize affine access in loop nests. We present a methodology that optimizes memory performance of data-parallel architectures. The goal is to convey implementation-specific information to the compiler in a simple declarative manner through the hints provided by annotations, which helps to improve the performance of the given code. We evaluate the performance of our framework by considering BLAS and stencil codes.

aview(A, width, i, row) or aview(A, width, i) = A[i \* width + j] (a) Row major access of elements

shift(A, 0, C) = A[i \* width + (j + C)]

(c) Row major shifted access of elements

aview(A, height, i, column) = A[j \* height + i]

(b) Column major access of elements

stride(A, 1, C) = A[i \* width + (C \* j)]

(d) Strided access of elements

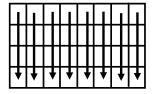

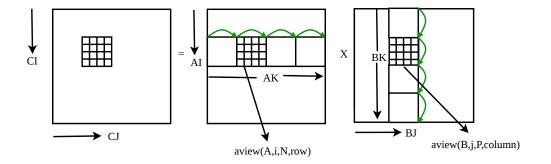

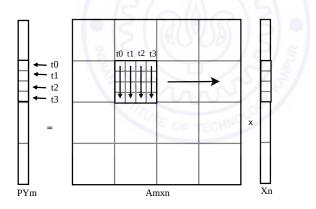

Figure 4.1: Memory Access Patterns and their Respective Operator Annotations with their Linearized Representation.

## 4.1 Memory Access Operators

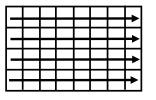

In this section, we present operator annotations that capture the memory access pattern present in a loop nest. The operator annotations *aview*, *stride* and *shift* are meant to provide the necessary information to represent affine memory access patterns. This in turn is used for optimizations presented in Section 4.2.2. Figure 4.1 presents examples of memory access patterns along with the associated operator annotations.

### **Operator** *aview*

The row linear and column linear memory access patterns refer to accesses in which a dimension of an array is contiguously accessed with respect to iteration space as shown in Fig. 4.1a and Fig. 4.1b respectively. The *aview* operator provides composition for row/column linear memory access patterns. It provides a linearized view of array elements associated with the object and has the following four parameters:

- 1. The collection object.

- 2. The limiting condition for the implicit loop iterator.

- 3. Iterator associated with the direction of access.

- 4. The direction of access.

The signature of the *aview* operator is as follows: **aview(DataType** objectName, **int** numberOfColumns, **int** explicitIterator, **int** accessDirection)

### **Operator** shift

A shifted memory access pattern refers to an access in which a dimension of an array is contiguously accessed with respect to the iteration space, but this contiguous access is shifted by some constant. The use of the *shift* operator and its access pattern is shown in Fig. 4.1c. The first parameter corresponds to the collection object. The second and third parameters are used to provide the amount of shift in the row and column directions respectively. The signature of *shift* operator is as follows:

shift(DataType objectName, int rowShift, int colShift)

### **Operator** *stride*

The use of the *stride* operator allows non-unit stride memory access. Fig. 4.1d illustrates its use. The first parameter corresponds to the collection object. The second and third parameters are used to provide the stride value for specific directions. The signature of the *stride* operator is as follows:

stride(DataType objectName, int rowStride, int colStride)

**Example 4.1:** The operators *shift* and *stride* can be combined to generate different access patterns. Listing 4.1 demonstrates some interesting combinations of these operators.

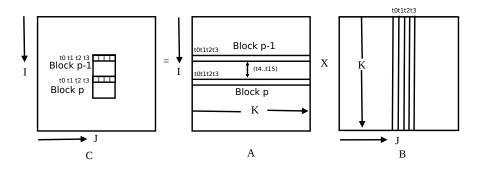

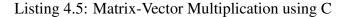

**Example 4.2:** To describe our programming model, we start with the matrix multiplication code example provided in Listing 4.2. The framework parallelizes a loop nest by associating one logical thread with some number of points in the iteration space of the nest. It then partitions and maps the logical threads onto physical ones, guided by annotations that the programmer employs to tune the code. The annotated code, using the *aview* operator and the data parallel \_for loop, is shown in Listing 4.3. The data parallel \_for loops (i and j) in the code get mapped to threads when parallelized. When used in conjunction with the *tile* operator, these loops correspond to a 2D thread configuration.

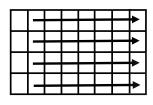

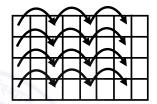

**Example 4.3:** The transformation framework provides linearized access for each *aview* operator as shown in Listing 4.4. Using *aview* and *tile* results in inter-thread and intra-thread access of elements in block ((i - tx)/BLOCK\_SIZE\_X, (j - ty)/BLOCK\_SIZE\_Y)) by thread (tx, ty) for array **A**, **B** and **C** as shown in Figure 4.2. The high level semantic interpretation of column linear memory access operation (memory access of **B** in Listing 4.3) results in coalesced global memory access by threads in a warp. The use of the data parallel \_for loop iterators (i and j) for accessing the elements of **C** indicates each thread accessing one element of the matrix. The row linear memory access of **A** leads to uncoalesced global memory access by threads in the warp. Using these interpretations our code generator generates naive CUDA code for GPU.

shift(stride(A,2,3),0,-4) = A[2\*i][3\*j-4] = A[(2\*i)\*width+(3\*j-4)]

Listing 4.1: Combination of Shift and Stride operator annotations

```

for(int i = 0; i < M; i++)

for(int j = 0; j < N; j++)

for(int k = 0; j < N; j++)

C[i][j] += A[i][k] * B[k][j];</pre>

```

Listing 4.2: Serial matrix multiplication code

Listing 4.3: Annotated Matrix-Multiplication Code

```

aview(A,N,i,row) = A[i * N + k]

aview(B,P,j,column) = B[k * P + j]

C(i,j) = C[i * M + j]

```