## CS698Y: Modern Memory Systems Lecture-16 (DRAM Timing Constraints)

# **Biswabandan Panda**

biswap@cse.iitk.ac.in

https://www.cse.iitk.ac.in/users/biswap/CS698Y.html

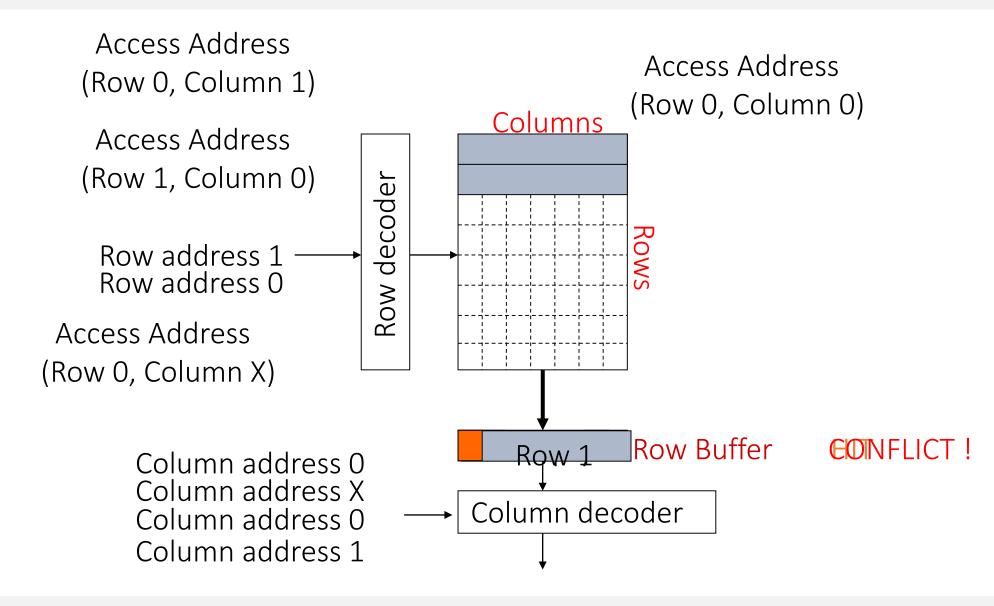

### Accessing a Row

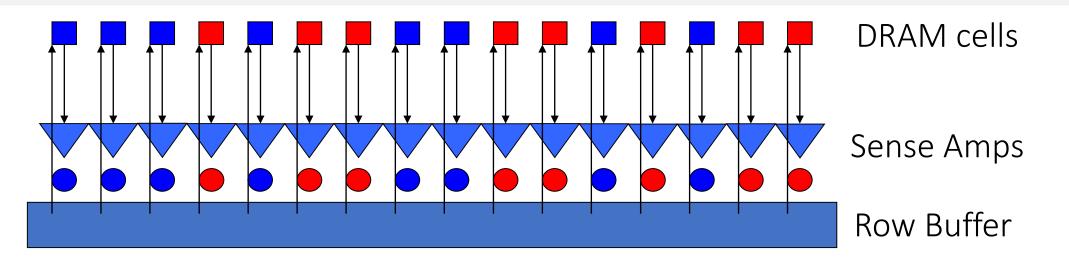

### **Row Buffer Operations**

Access to a closed row (Sequence of Commands):

ACT: Activate the row and place it into row buffer READ/WRITE: Reads or writes a column PRECHARGE: Close the row

Access to an open row (Sequence of Commands):

**READ/WRITE:** Reads or writes a column **PRECHARGE:** Close the row

### **DRAM Timing Constraints**

tRAS: Latency for Row Address Strobe

tRP: Latency for PRECHARGE

tRC: Row cycle time. Time gap between two row accesses (tRAS + tRP)

tCAS (tCL): Latency for Column Address Strobe (data from column to bus)

tRCD: Row to Column Delay, Latency of an ACT (gap between row access and data in sense amplifiers)

tCCD: Column to Column Delay

tRRD: Row to Row Delay (between two row ACTs)

tBURST: Burst length (how many bytes read/written)

### tRAS

tRAS: Latency for Row Address Strobe

The time interval between row access command and data restoration in a DRAM array. A DRAM bank can not be precharged until at least tRAS time after the previous bank activation

Minimum time a row must open

### **DRAM Refresh**

DRAM cells lose contents after a while,

Refresh command refreshes all rows (different avatars like all rows in one bank, all banks)

How to implement refresh?

What is the latency? How frequent? Look at tRFC and tREFI

Modern Memory Systems

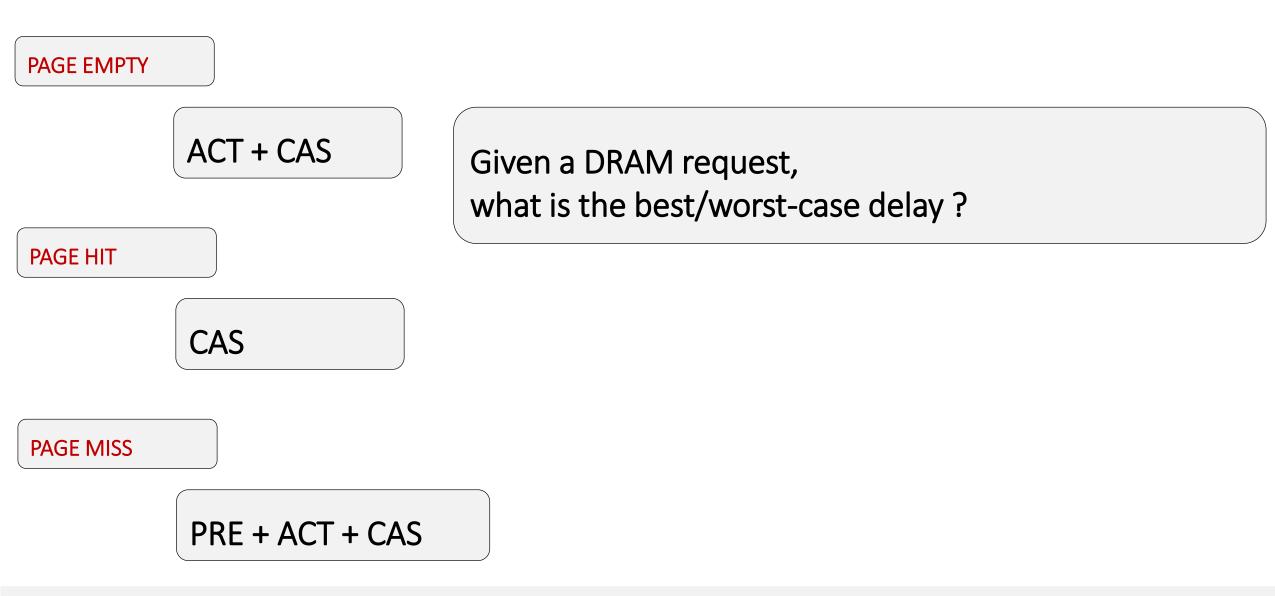

### **OPEN/CLOSED** Row Policies

#### **OPEN PAGE**

### After an access:

Keep the page in the row-buffer

Consecutive accesses to the same page : Row-buffer Hit

On an access to different page: Close the row and open the new one

#### CLOSED PAGE

### After an access:

Close the page

Consecutive accesses to different page : Low latency

On an access to different page: No need to close the row

### **OPEN/CLOSED** Row Policies

### OPEN :

Exploits spatial and temporal locality Access patterns ? Latency is limited tCAS

CLOSED : Exploits random access pattern Access patterns ?

### Let's Revisit the Latency

## Solve It [Courtesy: CS6810, Utah]

CL: 20ns RP + ACT + CL : 60ns ACT + CL : 40ns

For the following access stream, estimate the finish times

Req Time of arrival Open Closed

- X 0 ns

- Y 10 ns

- X+1 100 ns

- X+2 200 ns

- Y+1 250 ns

- X+3 300 ns

Note that X, X+1, X+2, X+3 map to the same row and Y, Y+1 map to a different row in the same bank. Ignore bus and queuing latencies. The bank is pre-charged at the start.

## Cheat Sheet (Timing constraints)

|              | Prev | Next | Rank | Bank   | Min. Timing            | Notes                             |

|--------------|------|------|------|--------|------------------------|-----------------------------------|

|              | Α    | Α    | S    | S      | tRC                    |                                   |

| A=row access | Α    | Α    | S    | d      | tRRD                   | plus tFAW for 5th RAS same rank   |

|              | Р    | Α    | S    | d      | tRP                    |                                   |

| R=col_rd     | F    | Α    | S    | S      | tRFC                   |                                   |

| W=col_wr     | Α    | R    | S    | S      | tRCD-tAL               | tAL=0 unless posted CAS           |

|              |      |      |      |        | Max(tBURS              |                                   |

| P=precharge  | R    | R    | S    | а      | T, tCCD)               | tBURST of previous CAS, same rank |

| F=Refresh    | _    | _    |      |        | tBURST+                |                                   |

|              | R    | R    | d    | а      | tRTRS                  | tBURST prev. CAS diff. rank       |

| s=same       |      |      |      |        | tCWD+                  |                                   |

| d=different  |      | -    |      | _      | tBURST+                | ADUDGT WARY CACINY SAME WARK      |

| u-uncrent    | w    | R    | S    | а      | tWTR                   | tBURST prev CASW same rank        |

| a=any        |      |      |      |        | tCWD+tBU<br>RST+tRTRS- |                                   |

|              | w    | R    | d    | а      | tCAS                   | tBURST prev CASW diff rank        |

|              | A    | w    | s    | a<br>S | tRCD-tAL               | CBORST PIEV CASW uni rank         |

|              | ^    | ••   | 3    | 3      | tCAS+tBUR              |                                   |

|              |      |      |      |        | ST+tRTRS-              |                                   |

|              | R    | w    | а    | а      | tCWD                   | tBURST prev. CAS any rank         |

|              |      |      |      |        | Max(tBURS              |                                   |

|              | w    | w    | S    | а      | T, tCCD)               | tBURST prev CASW same rank        |

|              |      |      |      |        | tBURST+tO              | •                                 |

|              | w    | w    | d    | а      | ST                     | tBURST prev CASW diff rank        |

|              | Α    | Р    | S    | s      | tRAS                   | -                                 |

|              |      |      |      |        | tAL+tBURS              |                                   |

|              |      |      |      |        | T+ tRTP-               |                                   |

|              | R    | Р    | S    | S      | tCCD                   | tBURST of previous CAS, same rank |

|              |      |      |      |        | tAL+tCWD               |                                   |

|              |      |      |      |        | +                      |                                   |

|              |      |      |      |        | tBURST+tW              |                                   |

|              | w    | Р    | S    | S      | R                      | tBURST prev CASW same rank        |

|              | F    | F    | S    | а      | tRFC                   |                                   |

|              | Р    | F    | S    | а      | tRFC                   |                                   |

### JEDEC Standard

| Standard<br>name                                       | DRAM cell<br>array clock | Cycle<br>time | I/O bus<br>clock | Data<br>rate    | Module<br>name | Peak<br>transfer<br>rate | Timings                                      | <u>CAS</u><br>Latency               |

|--------------------------------------------------------|--------------------------|---------------|------------------|-----------------|----------------|--------------------------|----------------------------------------------|-------------------------------------|

|                                                        | (MHz)                    | (ns)          | (MHz)            | ( <u>MT/s</u> ) |                | (MB/s)                   | (CL-tRCD-tRP)                                | (ns)                                |

| DDR3-800D<br>DDR3-800E                                 | 100                      | 10            | 400              | 800             | PC3-6400       | 6400                     | 5-5-5<br>6-6-6                               | 12.5<br>15                          |

| DDR3-1066E<br>DDR3-1066F<br>DDR3-1066G                 | 133.33                   | 7.5           | 533.33           | 1066.67         | PC3-8500       | 8533.33                  | 6-6-6<br>7-7-7<br>8-8-8                      | 11.25<br>13.125<br>15               |

| DDR3-1333F*<br>DDR3-1333G<br>DDR3-1333H<br>DDR3-1333J* | 166.67                   | 6             | 666.67           | 1333.33         | PC3-10600      | 10666.67                 | 7-7-7<br>8-8-8<br>9-9-9<br>10-10-10          | 10.5<br>12<br>13.5<br>15            |

| DDR3-1600G*<br>DDR3-1600H<br>DDR3-1600J<br>DDR3-1600K  | 200                      | 5             | 800              | 1600            | PC3-12800      | 12800                    | 8-8-8<br>9-9-9<br>10-10-10<br>11-11-11       | 10<br>11.25<br>12.5<br>13.75        |

| DDR3-1866J*<br>DDR3-1866K<br>DDR3-1866L<br>DDR3-1866M* | 233.33                   | 4.286         | 933.33           | 1866.67         | PC3-14900      | 14933.33                 | 10-10-10<br>11-11-11<br>12-12-12<br>13-13-13 | 10.56<br>11.786<br>12.857<br>13.929 |

### Some More Events

(Refer Chapter 11 of Memory Systems by Bruce Jacob) Try to understand TABLE 11.1 Find latencies for the following

Consecutive reads/writes to same rank

Consecutive reads to different ranks

Consecutive reads to different rows of same bank

Consecutive reads to different banks

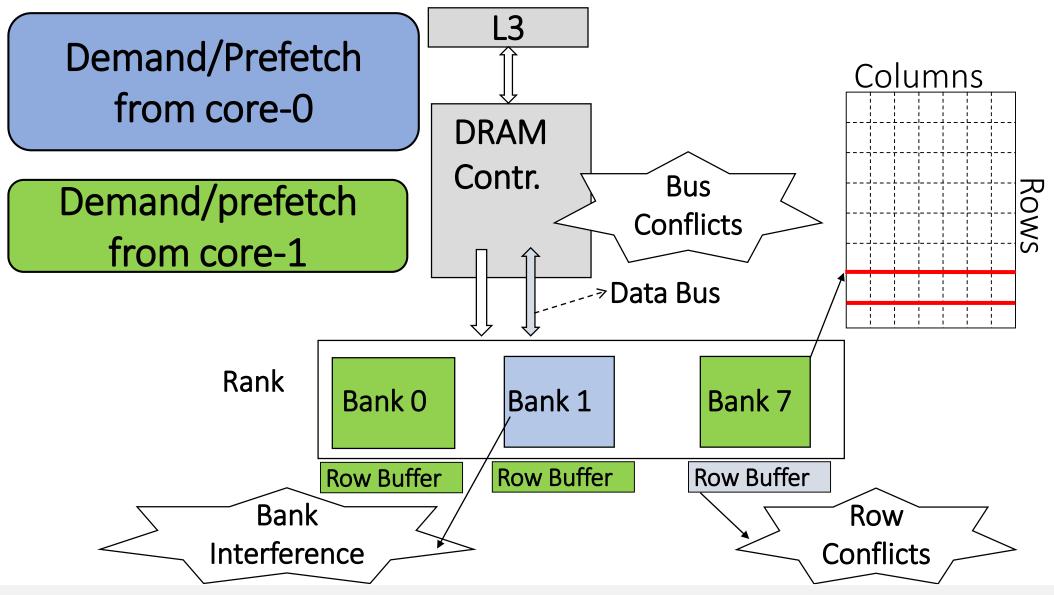

## **Conflicts of Interest**

Modern Memory Systems

Biswabandan Panda, CSE@IITK