# Lecture-6 (Pipeline Hazards) CS422-Spring 2018

## Hazards

- Limits to pipelining: Hazards prevent next instruction from executing during its designated clock cycle

- -<u>Structural hazards</u>: HW cannot support this combination of instructions (single person to fold and put clothes away)

- <u>Data hazards</u>: Instruction depends on result of prior instruction still in the pipeline (missing sock)

- -<u>Control hazards</u>: Caused by delay between the fetching of instructions and decisions about changes in control flow (branches and jumps).

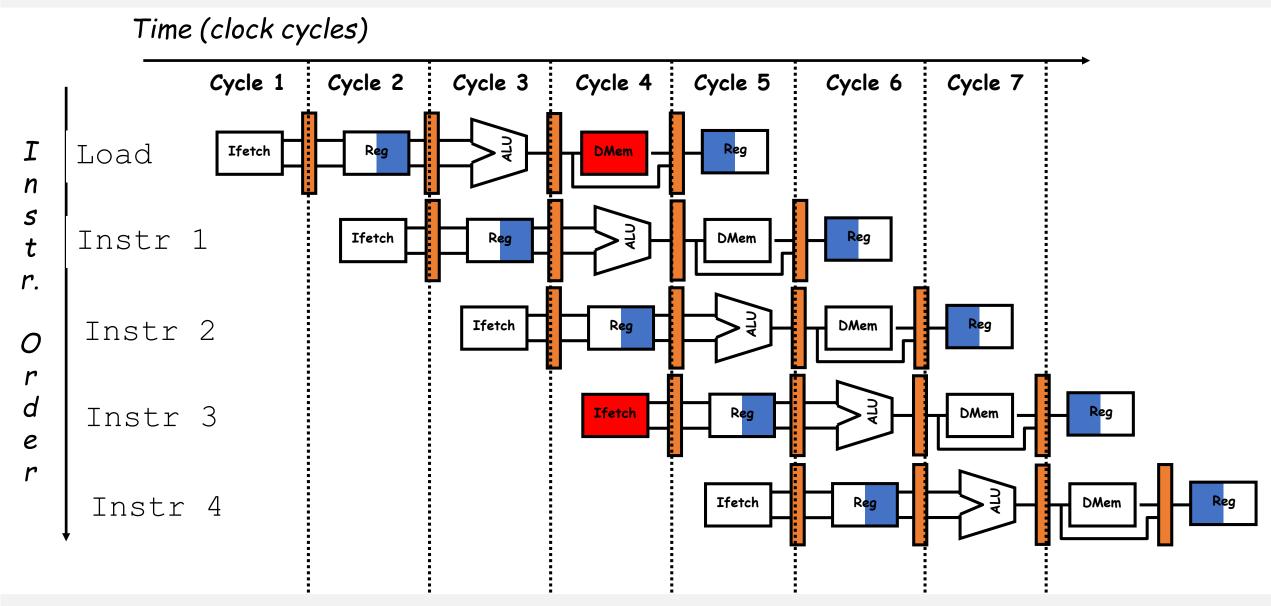

# One Memory Port/Structural Hazards

CS422: Spring 2018

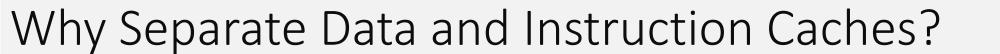

## Bubble

**CS422: Spring 2018**

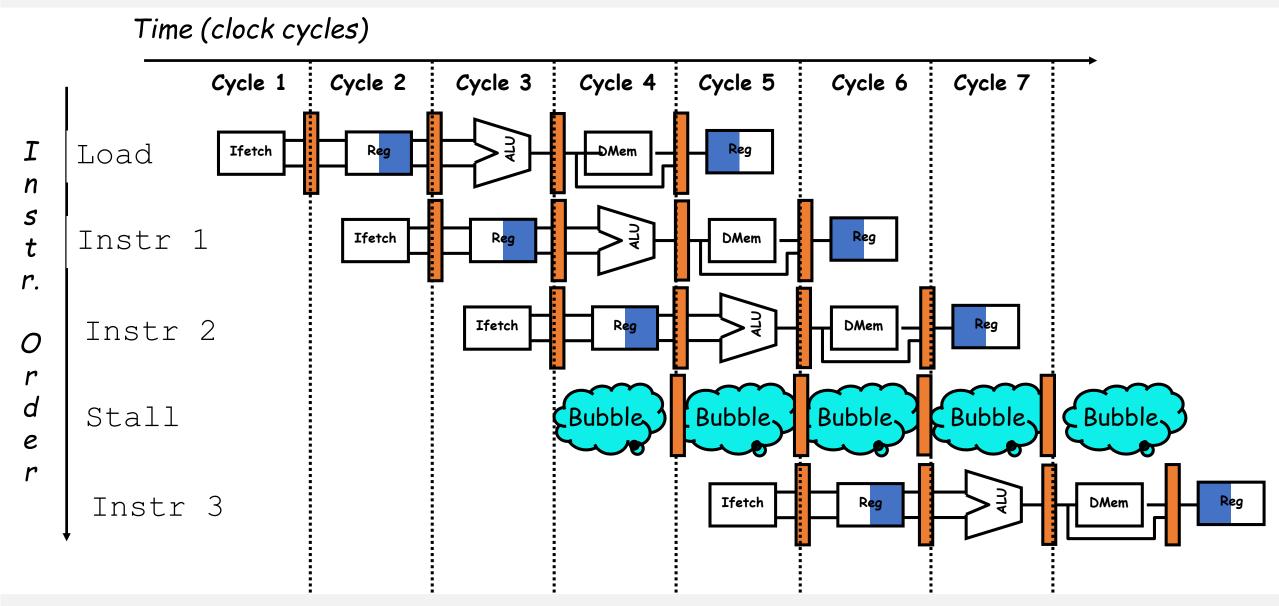

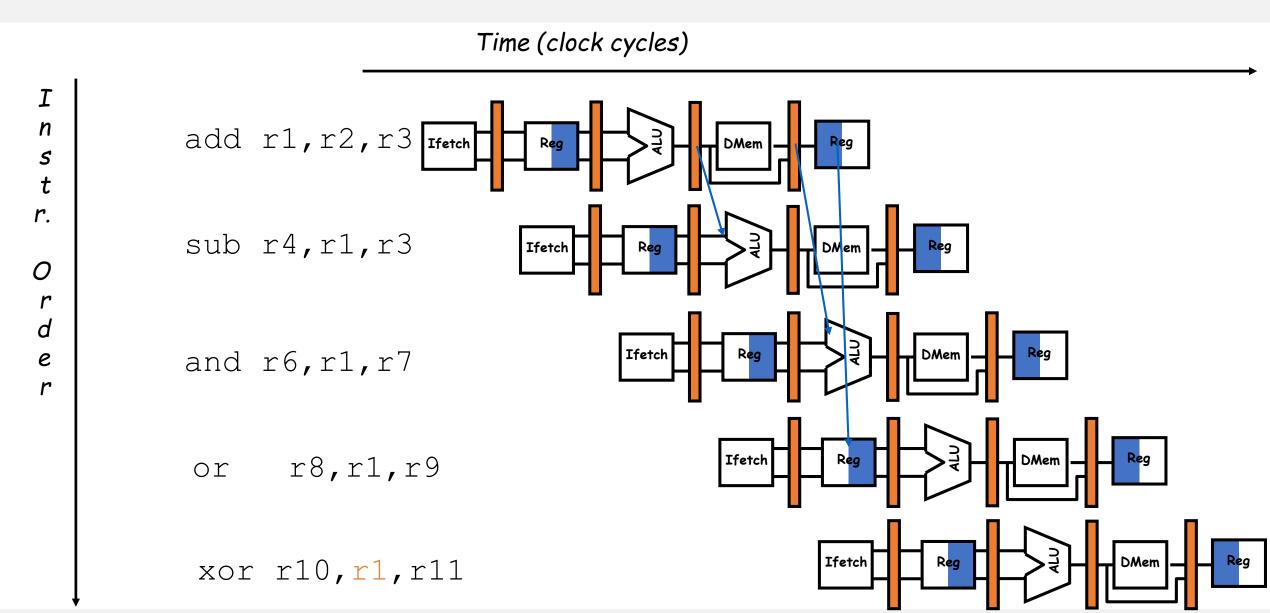

## Data Hazards

#### Time (clock cycles)

#### **RAW**

• Read After Write (RAW)

Instr<sub>I</sub> tries to read operand before Instr<sub>I</sub> writes it

I: add r1, r2, r3

J: sub r4, r1, r3

• Caused by a "Dependence" (in compiler nomenclature). This hazard results from an actual need for communication.

## WAR

Write After Read (WAR)

Instr<sub>I</sub> writes operand <u>before</u> Instr<sub>I</sub> reads it

I: sub r4,r1,r3

K: mul r6,r1,r7

- Called an "anti-dependence" by compiler writers. This results from reuse of the name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Reads are always in stage 2, and

- Writes are always in stage 5

## WAW

Write After Write (WAW)

Instr<sub>I</sub> writes operand <u>before</u> Instr<sub>I</sub> writes it.

→ I: sub r1,r4,r3

J: add r1,r2,r3

K: mul r6,r1,r7

- Called an "output dependence" by compiler writers This also results from the reuse of name "r1".

- Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Writes are always in stage 5

- Will see WAR and WAW in more complicated pipes

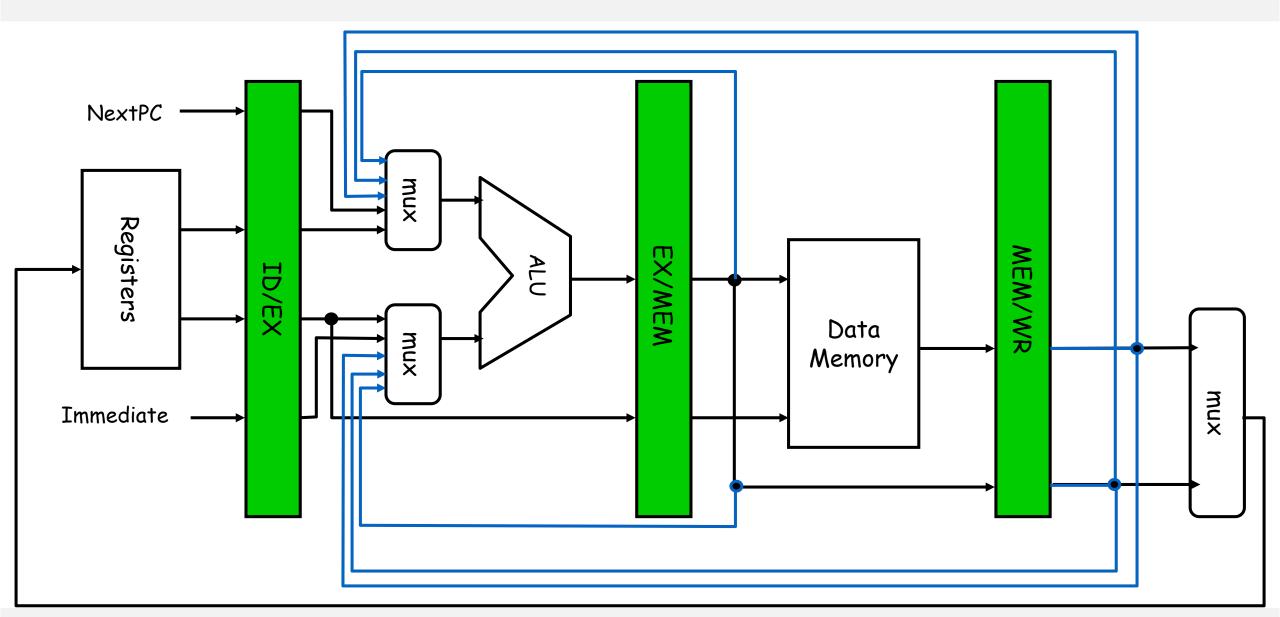

# Data Forwarding

# Hardware Change

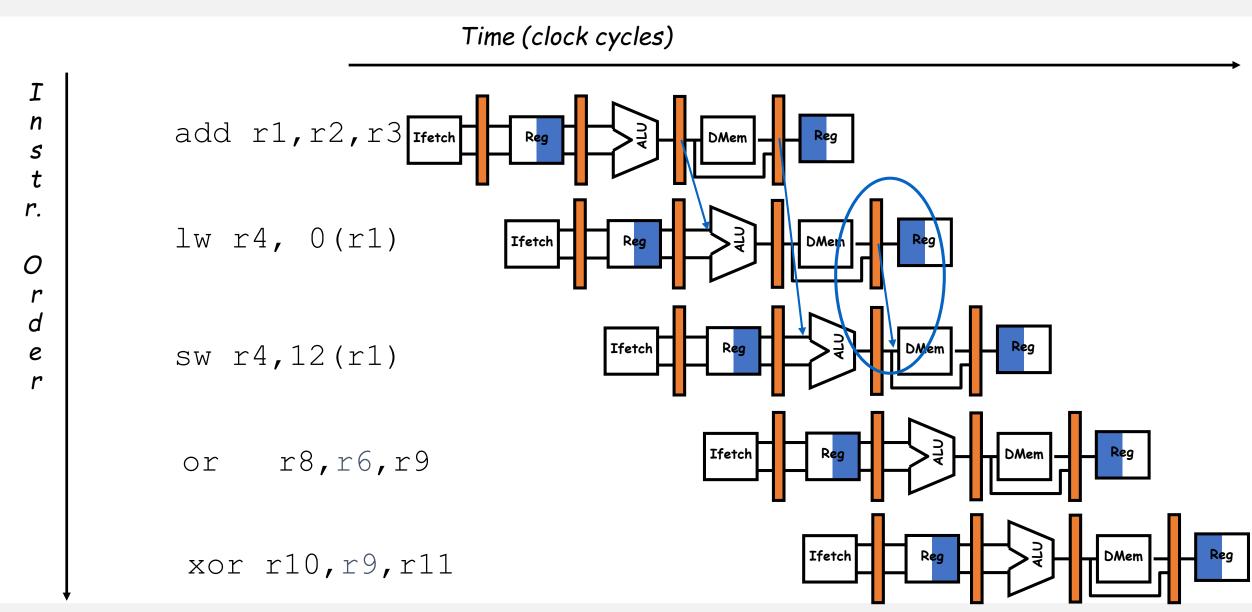

## Forwarding to Avoid LW-SW?

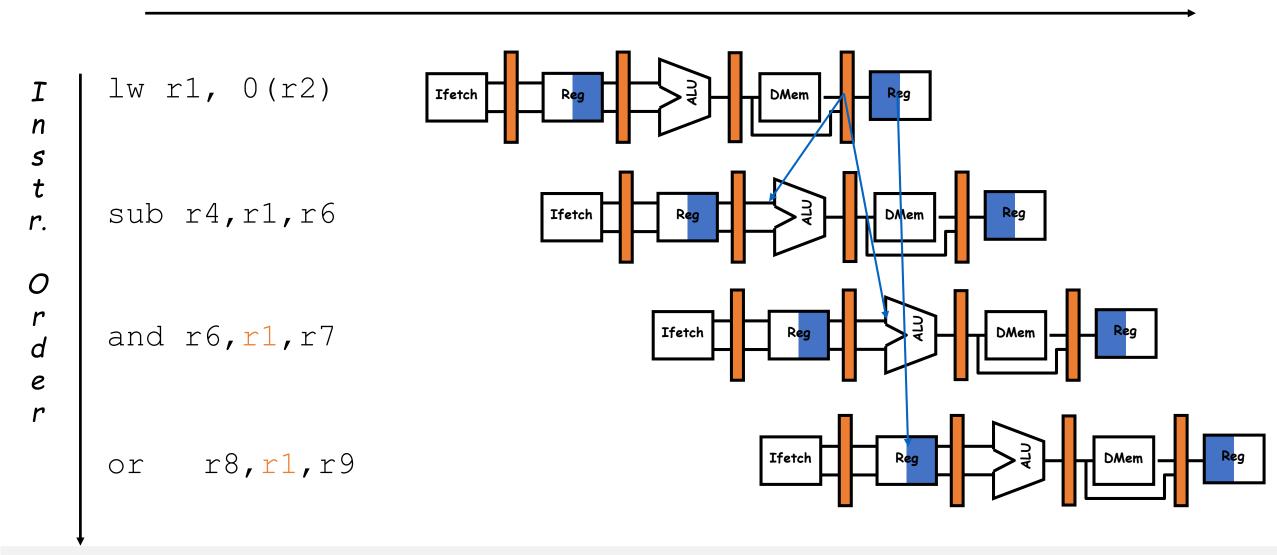

# Even With Forwarding?

Time (clock cycles)

**CS422: Spring 2018**

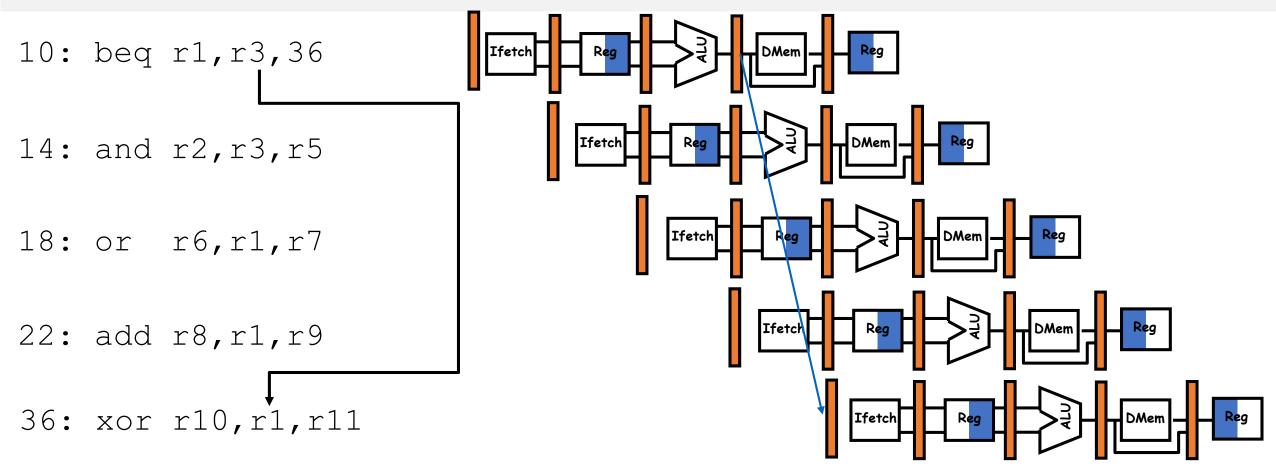

# Control Hazard on Branches with 3-stage Stall

What do you do with the 3 instructions in between? How do you do it?

Where is the "commit"?

## Branches

#### Conditional

- the target address is close to the current PC location

- branch distance from the incremented PC value fits into the immediate field

- for example: loops, if statements

#### **Unconditional** (jumps)

- transfers of control

- the target address is far away from the current PC location

- for example: subroutine calls

#### Branches

|   | qo | rs | rt | immediate |

|---|----|----|----|-----------|

| ш |    |    |    |           |

**Syntax:** BEQ \$1, \$2, 12

**Action:** If (\$1 != \$2), PC = PC + 4

**Action:** If (\$1 == \$2), PC = PC + 4 + 48

Immediate field codes # words, not # bytes. Why is this encoding a good idea?

Increases branch range to 128 KB.

Zero-extend or sign-extend immediate field? Sign-extend. Why is this extension method a good idea? Supports forward and backward branches.