Lecture-6 (10K feet view: Processor Core) CS422-Spring 2019

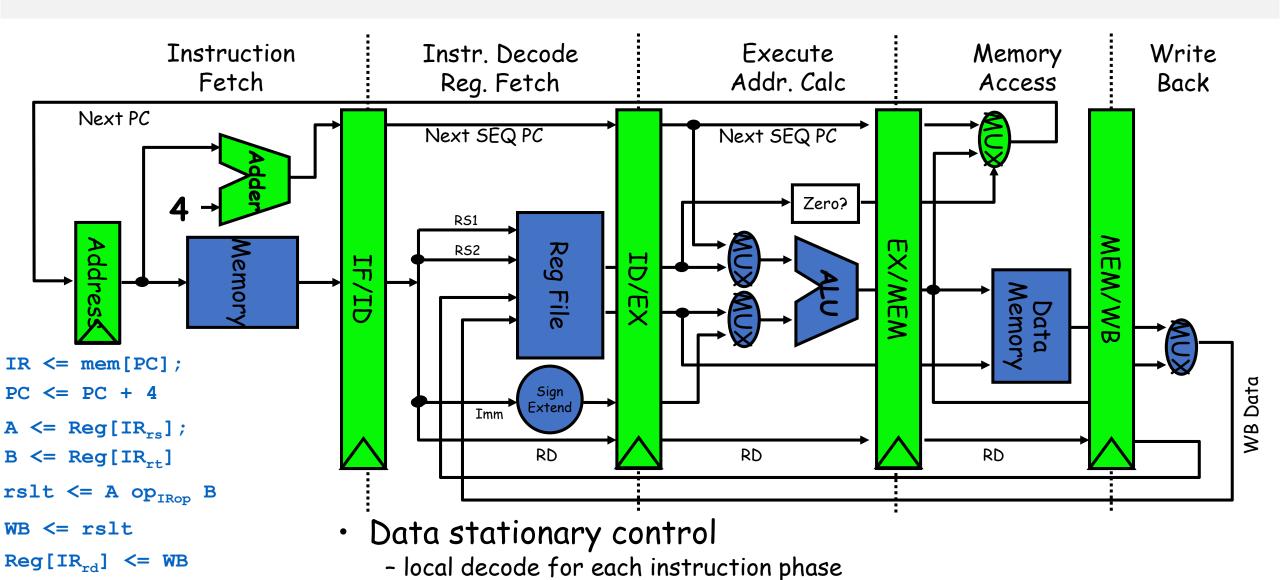

### Simple 5-stage Pipeline

/ pipeline stage

### Hazards

- Limits to pipelining: Hazards prevent next instruction from executing during its designated clock cycle

- -<u>Structural hazards</u>: HW cannot support this combination of instructions (single person to fold and put clothes away)

- <u>Data hazards</u>: Instruction depends on result of prior instruction still in the pipeline (missing sock)

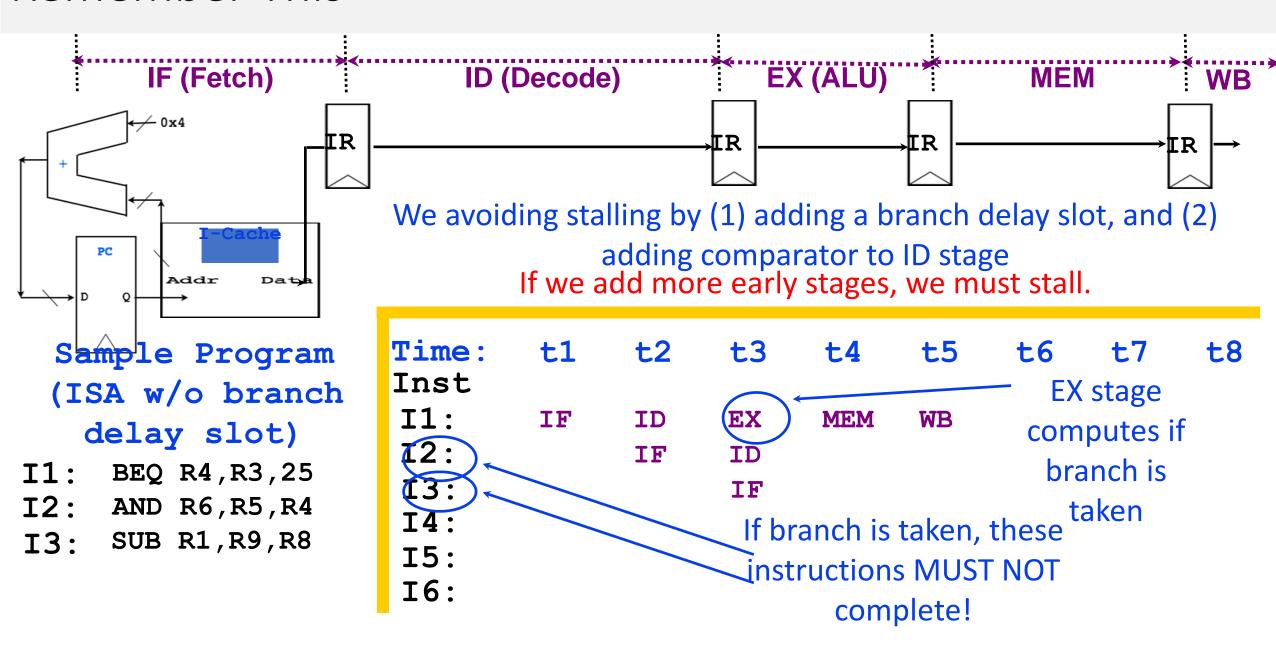

- -<u>Control hazards</u>: Caused by delay between the fetching of instructions and decisions about changes in control flow (branches and jumps).

### Data Hazards

• Read After Write (RAW)

Instr<sub>I</sub> tries to read operand before Instr<sub>I</sub> writes it

WAR and WAW too

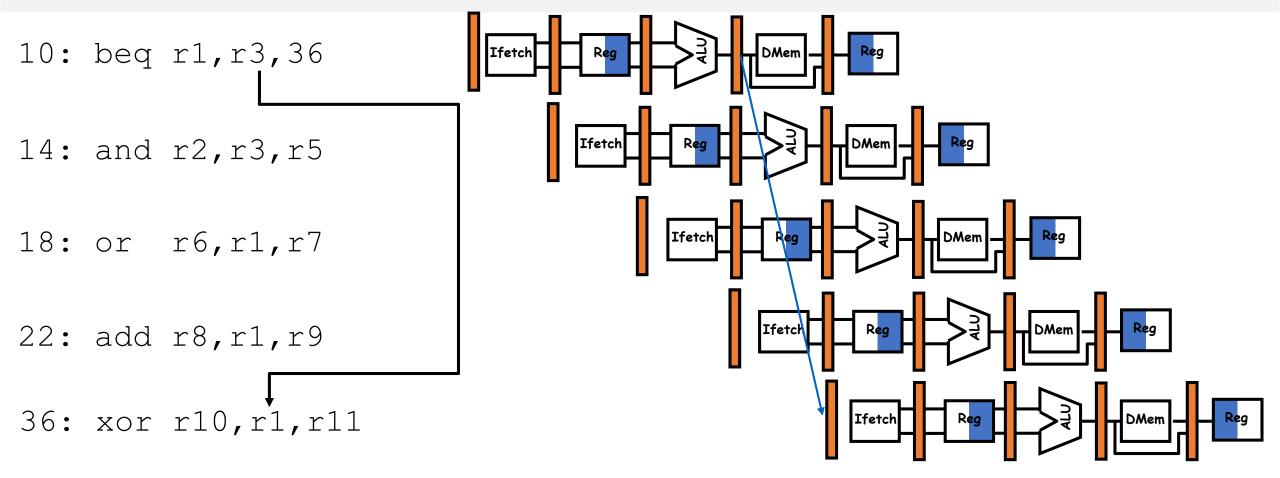

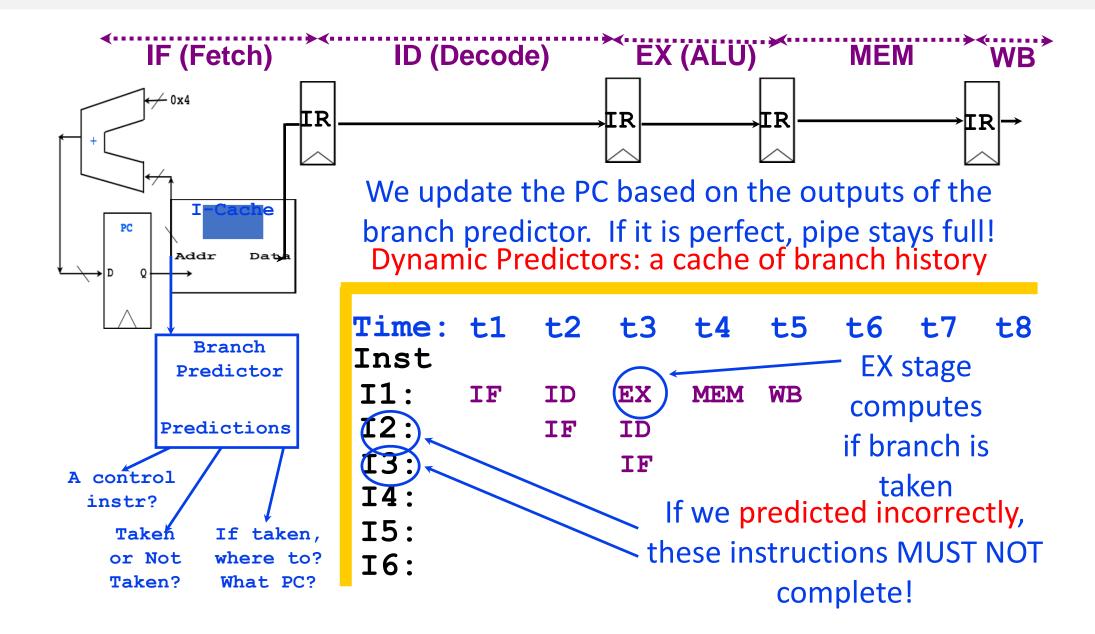

#### Control Hazard

What do you do with the 3 instructions in between? How do you do it?

Where is the "commit"?

#### Remember This

#### Welcome to Branch Prediction

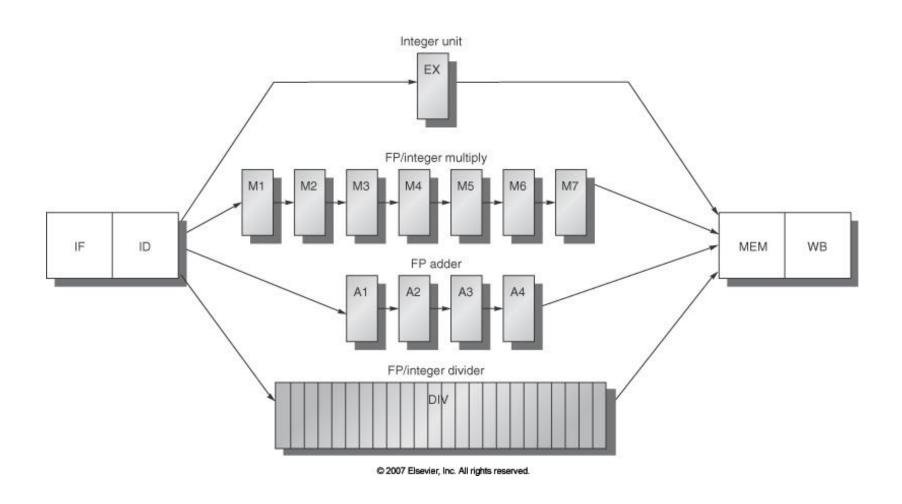

# Multi-Cycle Instructions

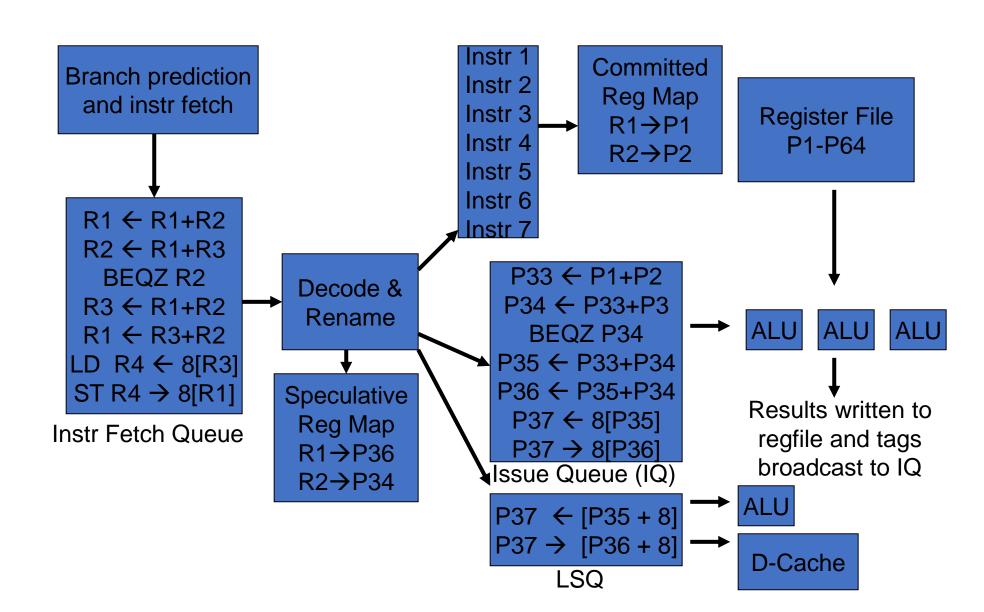

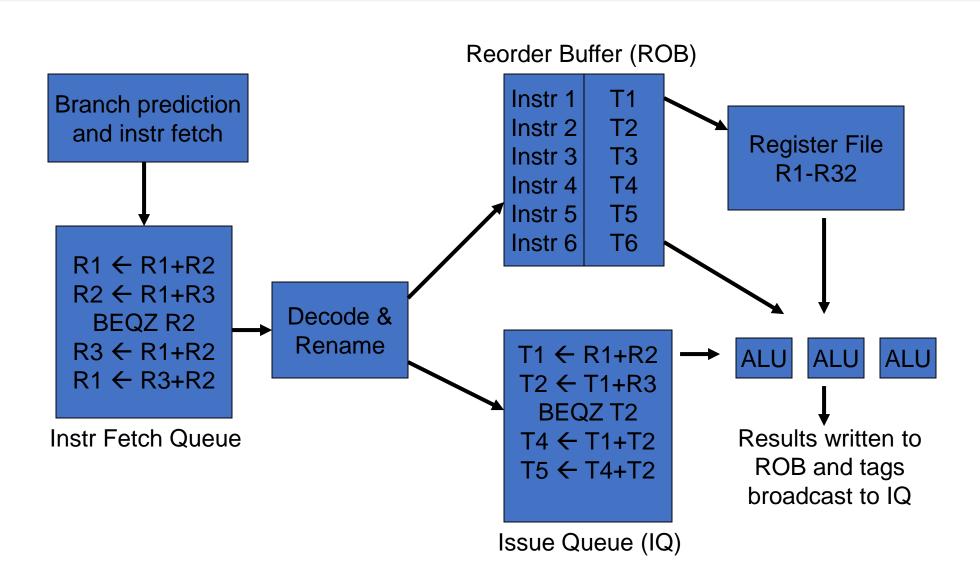

## Out-of-Order (O3) World

## O3 + LSQ + Multi Issue (SuperScalar)