# Lecture-3 (DRAM organization: 10K feet view) CS422-Spring 2019

# Why DRAM?

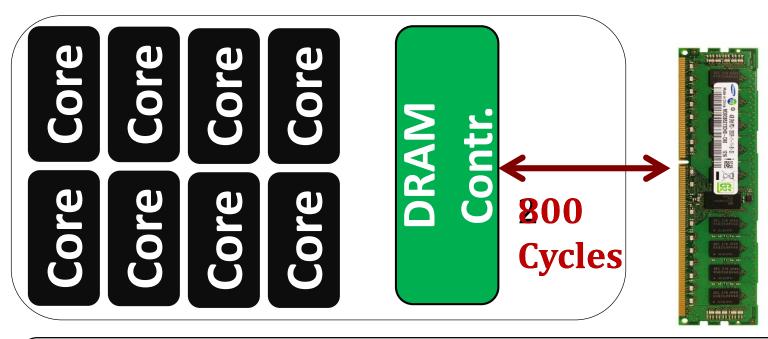

#### **Core count doubling every 2 years**

**Memory wall = Latency wall + Bandwidth wall**

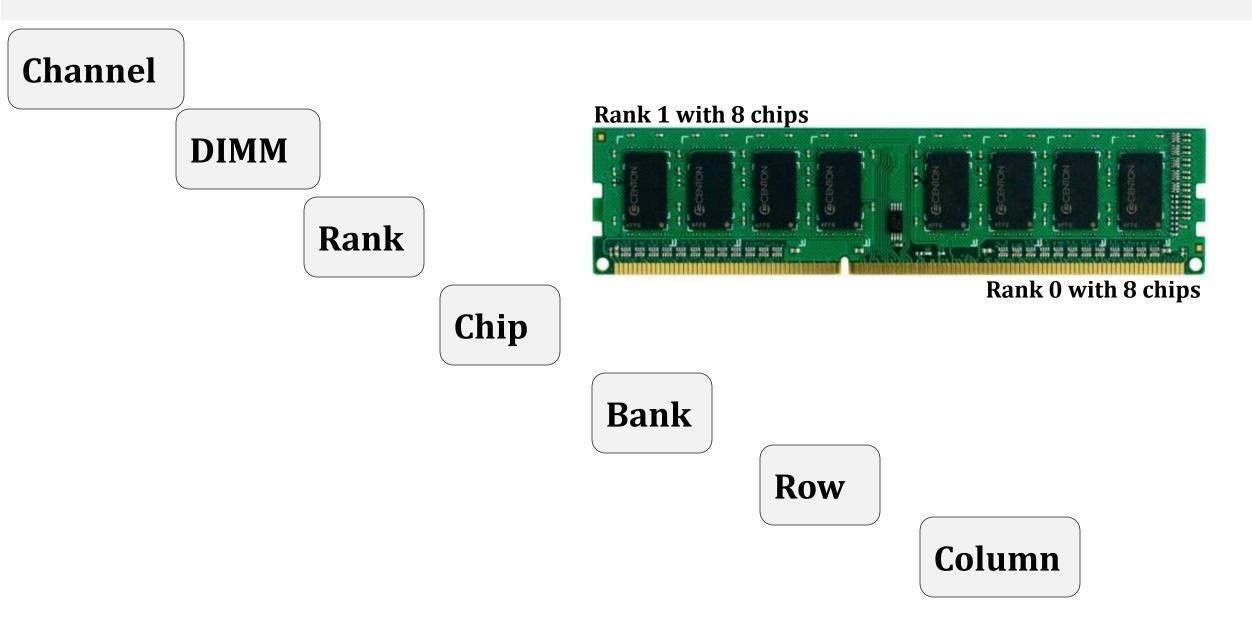

## **DRAM Organization**

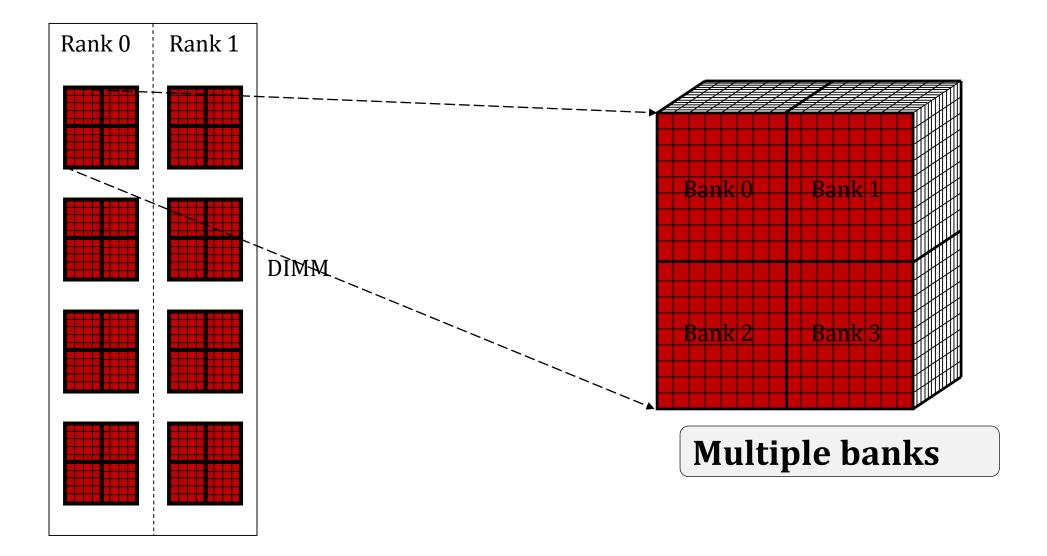

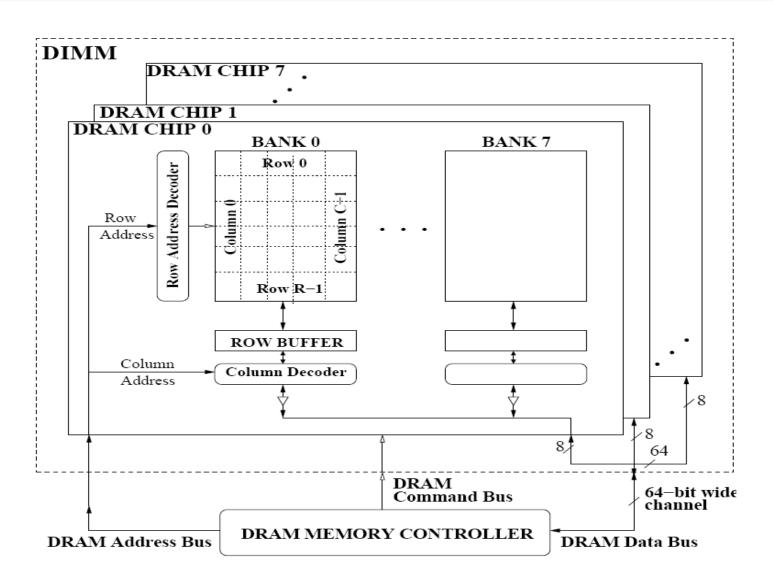

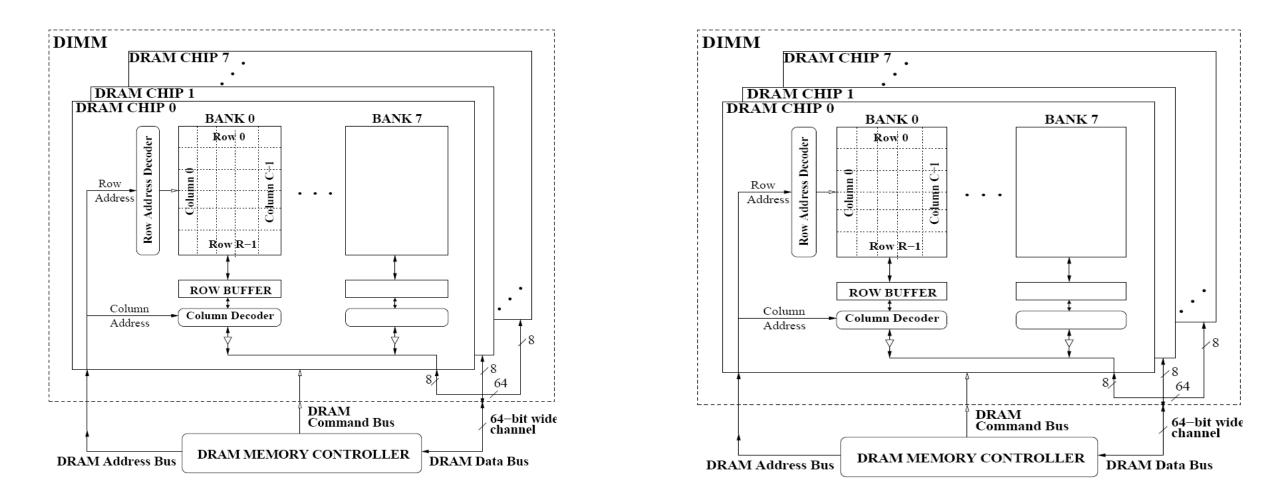

## Ranks, Banks, Rows, and Columns

## Ranks, Banks, Rows, and Columns

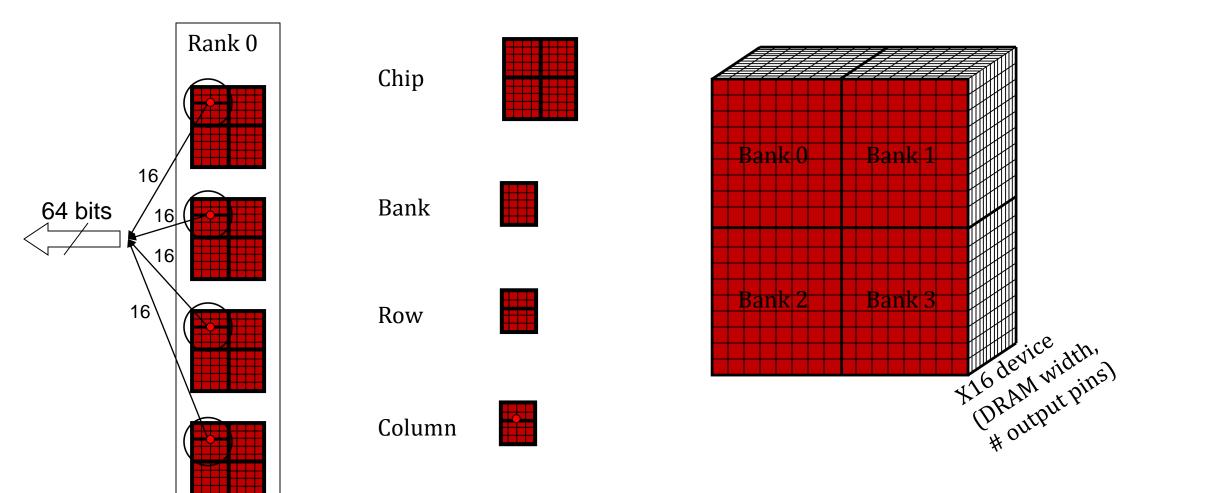

16-bit interface: 16 bits from each chip in one go

## Let's Dig Deep

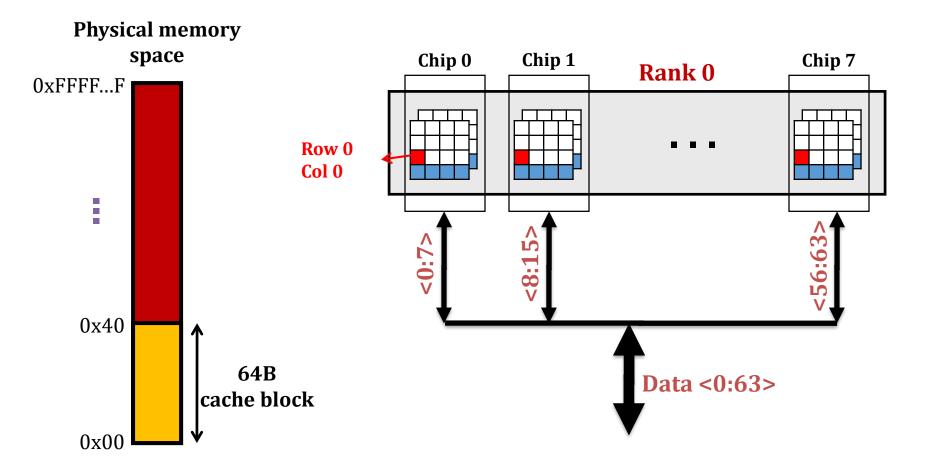

Each rank has 64-bit wide data bus

If a rank is of width x8 then # DRAM chips ??

What about x4, # DRAM chips ??

If a rank is of width x8 then # DRAM chips ?? 8

What about x4, # DRAM chips ?? 16

## Where is Your 1 bit?

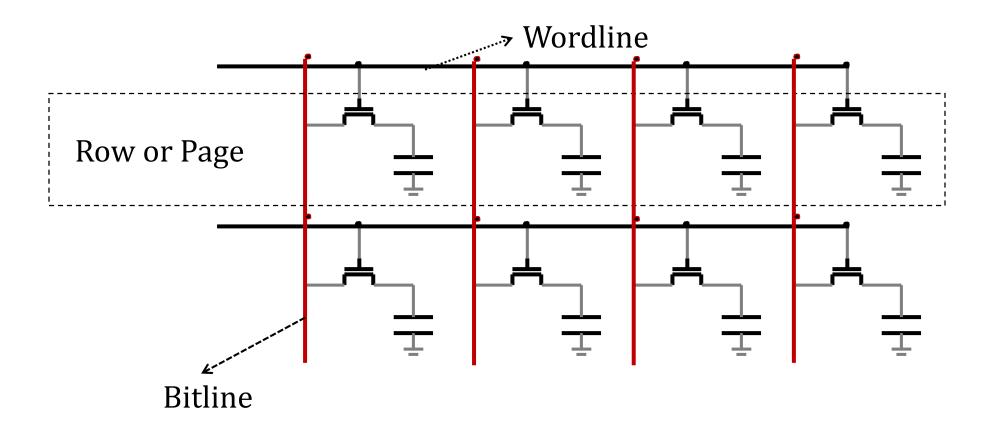

# Row (page) and Row buffer (Sense Amplifier)

#### Logically

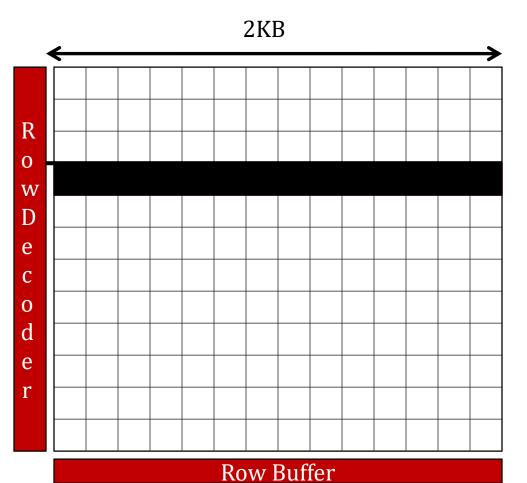

#### Each bank has a row buffer

Stores the last used row

Now Duller

Column mux

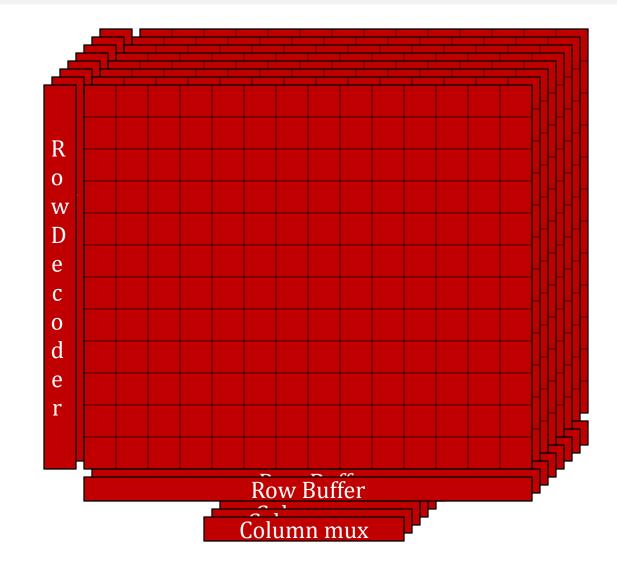

# Bank: Collection of DRAM Arrays

- DRAM Width

- x4 device

- x8 device

- Other possible widths

- x16

- x32

- x48

- x72

### An Example – 4GB DIMM

2Gb \* 8 DRAM Chips (one side of the rank)

Total 16 chips + 2 chips for ECC (for both the ranks)

64 bit + 8 bit ECC interface (72 bit wide DIMM)

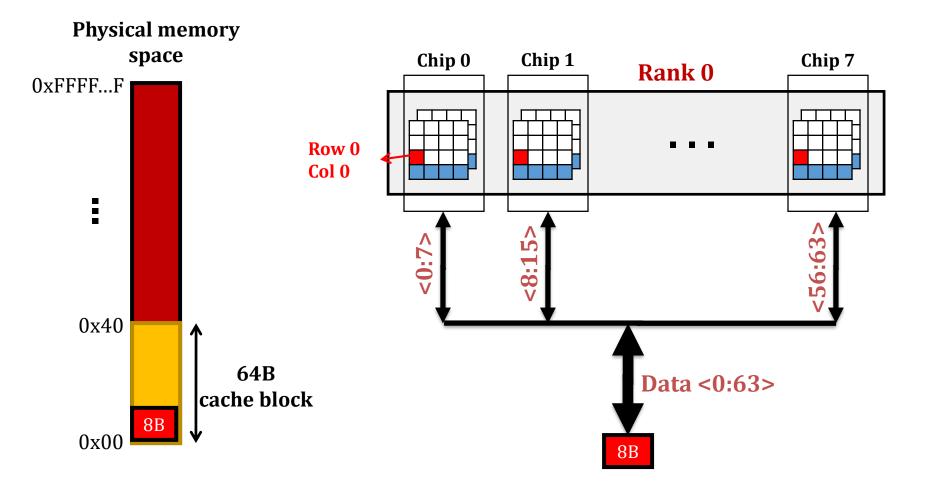

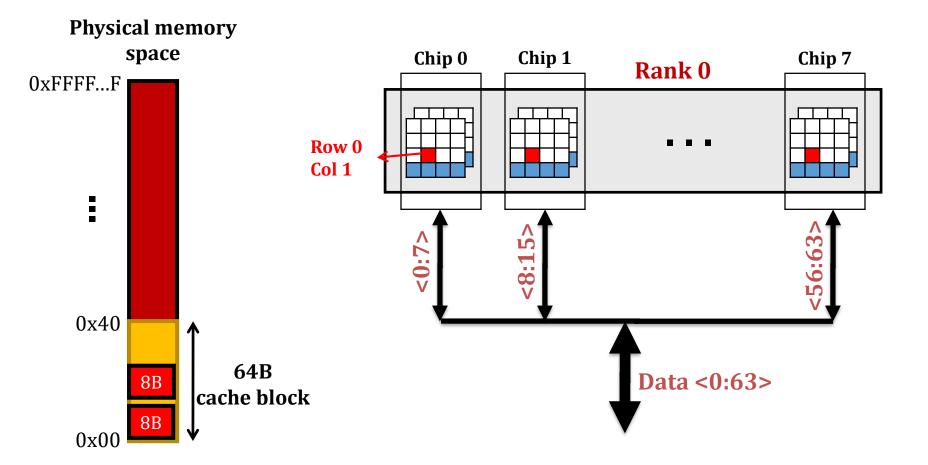

Transferring a 64B cache line will take 8 transfers of 8B each

8B will come from 8 chips (8 bits from one chip)

1 bit from each DRAM array assuming 8 DRAM arrays per bank

#### **Another View**

## **DRAM Channels**

#### 2 channels: 1 channel per controller

#### DRAM to LLC

**Physical memory** space Chip 1 Chip 7 Chip 0 Rank 0 0xFFFF...F . . . 56:63> <8:15> <0:7> 0x40 不 64B Data <0:63> cache block 0x00

```

DRAM to LLC [CMU 18-447]

```

```

DRAM to LLC [CMU 18-447]

```

### DRAM to LLC

8 cycles (DRAM IO): 1 cycle transfers 8 bytes from a column

# DRAM Address Mapping (1 Channel)

#### 2GB DRAM, 8 Banks, 16K rows, 2K Columns per bank

#### **Cache Interleaving: Consecutive cache blocks in consecutive banks**

| Row (14 bits) | High Column | Bank (3 bits) | Low Col. | Byte in bus (3 bits) |

|---------------|-------------|---------------|----------|----------------------|

|               | 8 bits      |               | 3 bits   |                      |

#### **Row Interleaving: Consecutive rows in consecutive banks**

|               | T             |                  |                      |

|---------------|---------------|------------------|----------------------|

| Row (14 bits) | Bank (3 bits) | Column (11 bits) | Byte in bus (3 bits) |