# Scabbard: An Exploratory Study on Hardware Aware Design Choices of Learning with Rounding-based Key Encapsulation Mechanisms

SUPARNA KUNDU and QUINTEN NORGA, COSIC, KU Leuven, Belgium ANGSHUMAN KARMAKAR, IIT Kanpur, India SHREYA GANGOPADHYAY, IIT Kharagpur, India JOSE MARIA BERMUDO MERA, PQShield, Oxford, UK INGRID VERBAUWHEDE, COSIC, KU Leuven, Belgium

Recently, the construction of cryptographic schemes based on hard lattice problems has gained immense popularity. Apart from being quantum resistant, lattice-based cryptography allows a wide range of variations in the underlying hard problem. As cryptographic schemes can work in different environments under different operational constraints such as memory footprint, silicon area, efficiency, power requirement, etc., such variations in the underlying hard problem are very useful for designers to construct different cryptographic schemes. In this work, we explore various design choices of lattice-based cryptography and their impact on performance in the real world. In particular, we propose a suite of key-encapsulation mechanisms based on the learning with rounding problem with a focus on improving different performance aspects of lattice-based cryptography. Our suite consists of three schemes. Our first scheme is Florete, which is designed for efficiency. The second scheme is Espada, which is aimed at improving parallelization, flexibility, and memory footprint. The last scheme is Sable, which can be considered an improved version in terms of key sizes and parameters of the Saber key-encapsulation mechanism, one of the finalists in the National Institute of Standards and Technology's post-quantum standardization procedure. In this work, we have described our design rationale behind each scheme.

Further, to demonstrate the justification of our design decisions, we have provided software and hardware implementations. Our results show Florete is faster than most state-of-the-art KEMs on software platforms. For example, the key-generation algorithm of high-security version Florete outperforms the National Institute of Standards and Technology's standard Kyber by 47%, the Federal Office for Information Security's standard Frodo by 99%, and Saber by 57% on the ARM Cortex-M4 platform. Similarly, in hardware, Florete outperforms Frodo and NTRU Prime for all KEM operations. The scheme Espada requires less memory and area than the implementation of most state-of-the-art schemes. For example, the encapsulation algorithm of high-security version Espada uses 30% less stack memory than Kyber, 57% less stack memory than Frodo, and 67% less stack memory than Saber on the ARM Cortex-M4 platform. The implementations of Sable maintain a trade-off between Florete and Espada regarding software performance and memory requirements. Sable outperforms Saber at least by 6% and Frodo by 99%. Through an efficient polynomial multiplier design, which exploits the small secret size, Sable outperforms most state-of-the-art KEMs, including Saber, Frodo, and NTRU Prime. The implementations of Sable that use number theoretic transform-based polynomial multiplication (SableNTT) surpass all the state-of-the-art schemes in performance, which are optimized for speed on the Cortext M4 platform. The performance benefit of SableNTT against Kyber lies in between 7 – 29%, 2 – 13% for Saber, and around 99% for Frodo.

CCS Concepts: • Security and privacy → Public key encryption; Hardware-based security protocols.

$Additional \ Key \ Words \ and \ Phrases: Post-quantum \ cryptography, Lattice-based \ cryptography, Learning \ with \ rounding, Key-encapsulation \ mechanism, Software implementations, AVX2, Cortex-M4, Hardware implementations, FPGA$

Authors' addresses: Suparna Kundu, Suparna.Kundu@esat.kuleuven.be; Quinten Norga, Quinten.Norga@esat.kuleuven.be, COSIC, KU Leuven, Kasteelpark Arenberg 10, Bus 2452, B-3001 Leuven-Heverlee, Belgium; Angshuman Karmakar, angshuman@cse.iitk.ac.in, IIT Kanpur, India; Shreya Gangopadhyay, gangopadhyay.shreya09@gmail.com, IIT Kharagpur, India; Jose Maria Bermudo Mera, josebmera@gmail.com, PQShield, Oxford, UK; Ingrid Verbauwhede, Ingrid.Verbauwhede@esat.kuleuven.be, COSIC, KU Leuven, Kasteelpark Arenberg 10, Bus 2452, B-3001 Leuven-Heverlee, Belgium.

#### 1 INTRODUCTION

Lattice-based cryptography has been one of the most discussed topics in public-key cryptography (PKC) for the past several years. Apart from being resistant to quantum attacks and hence a possible alternative for integer-factorization (IF) and discrete-log problem (DLP)-based cryptographic constructions, lattice-based cryptographic constructions are relatively simpler. Moreover, compared to IF and DLP, lattices offer lots of variations of underlying hard problems. This provides cryptographic designers with lots of maneuvering space to explore different designs to optimize and curate their cryptographic constructions for different applications. For example, from Ajtai's short-integer solution (SIS) [3] and Hoffstein et al.'s NTRU [59] in 1996 to Regev's learning with errors (LWE) [98] in 2005 and its subsequent variations such as Ring-LWE [81], Module-LWE [78], learning with rounding [8, 13], and recently discovered PLWE [99], CLWE [31], etc., the choice of computationally hard problems to design cryptographic schemes is in galore. Nevertheless, latticebased cryptography has not always been the most preferred choice for cryptographers. IF and DLP-based cryptography, which were invented a couple of decades earlier, had already well-established themselves in the existing public-key infrastructure. Due to lots of research on their implementation, side-channel security, cryptanalysis, etc., their theoretical and implementation aspects were well understood. Therefore, there was little incentive for theorists and practitioners alike to replace these classical cryptosystems with lattice-based cryptography even though Shor's [93, 101] algorithm and its detrimental effect on IF and DLP-based cryptography was known since 1994. This happened partly because quantum computing research was mostly restricted to the realm of theory, and there was skepticism about its physical existence in the future.

However, as the research on developing large-scale quantum computers gained momentum, the future of IF and DLP-based cryptosystems as mainstream PKC algorithms started looking bleak proportionately. Due to the recent advancements in the field of quantum computing, the adverse effects of quantum computers on our existing public-key infrastructure have become too hard to ignore further. Although the research in quantum-resistant PKC or post-quantum cryptography started a couple of decades ago, the watershed moment in the process of transitioning from classical PKC to PQC is the National Institute of Standards and Technology's (NIST) conclusion of a long and multi-staged standardization procedure [4] in 2022. NIST standardized PQC primitives such as public-key encryption (PKE) or keyencapsulation mechanism (KEM) Kyber [27], and digital signature schemes CRYSTALS-Dilithium [43], FALCON [46], and SPHINCS+ [11].

During NIST's standardization process, the cryptographic community witnessed many innovations in the design and implementation of PQC. Such as the introduction of module lattices [78] instead of more traditional standard [98] or ideal [81] lattices as a trade-off between speed and security, usage of central binomial distributions [7] instead of discrete Gaussian distribution for protection against potential side-channel attacks, just-in-time matrix generation in module lattices [68] and improvements in polynomial multiplications [24, 37, 62, 82] algorithms to improve efficiency, the introduction of error-correcting codes [23] to reduce the decryption failure rates of lattice-based cryptography, etc. These different designs went through a thorough and rigorous evaluation. For example, the non constant-time behavior of error-correcting codes was found to be highly vulnerable to side-channel attacks; similarly, the sparse distributions used in schemes such as LAC [80] were found to be unsuitable for generating secret polynomials. On the other hand, improvements in the NTT polynomial multiplications, such as using K-reduction algorithm [79], or just-in-time generation of module lattices, almost became the standard choice. Therefore, the NIST standardization process does not mark a zenith in the research and development of lattice-based or PQC; rather, it has established a framework and set a course for future advancement in POC.

In this work, we have decided to evaluate various design choices for constructing PQ KEM. We have particularly chosen the hard lattice problem learning with rounding (LWR). LWR is a relatively less used hard problem when designing lattice-based cryptographic schemes. The LWR problem is a de-randomized variant of the LWE problem where a deterministic rounding to a smaller modulus replaces the error sampling. This problem was introduced by Banerjee et al. [13] in 2012. Several works have been done on the hardness of the LWR problem and deduced that the LWR problem is as hard as the LWE problem [8, 9, 25]. Nevertheless, in the context of PQ KEM Saber [14], one of the finalists in the NIST procedure, we have seen quite some intriguing results on the LWR-based schemes. In particular, the major reasons that motivated us to explore the LWR-based PQ KEMs further are described below.

LWR-based schemes require fewer pseudo-random numbers than LWE-based schemes, as errors are not required to be sampled explicitly here. The error is generated inherently from rounding operations, which helps to gain better performance. The rounding modulus is smaller than the modulus of the LWE problem. Therefore for similar security levels, it results in smaller public-key sizes and ciphertext sizes. This also implies lesser bandwidth compared to the schemes based on the LWE problem. Although Kyber is based on the module-LWE (MLWE) problem, it also uses rounding on the encapsulation procedure (Compress function) to reduce the ciphertext size. In terms of performance, module-LWR (MLWR) based scheme Saber outperforms MLWE-based scheme Kyber in the cortex-M4 platform when an NTT-based multiplier is used for Saber (shown in Table 6). As NTT-based polynomial multiplication takes a similar amount of cycles for Saber and Kyber, Saber doesn't require expensive error sampling. Also, Saber's auxiliary functions, such as compress, decompress, encode, and decode operations, are simple and cheaper than Kyber's, thanks to its power-of-two moduli.

The choice of power-of-two moduli helps Saber achieve efficient hardware implementation as well. LWR-based schemes, in general, use Toom-Cook based polynomial multiplication instead of NTT-based polynomial multiplication. It helps to reduce the area requirements to implement LWR-based schemes in hardware compared to the LWE-based schemes. To perform NTT multiplication efficiently, the twiddle factors need to be stored in the memory. Also, the secret polynomial is smaller in the LWR-based scheme than LWE-based scheme, because in LWE-based scheme NTT needs to be performed on the secret polynomial, and it increases the memory requirement to store the secret key after the NTT. LWE-based schemes need to use a prime reduction algorithm (for Kyber, it is Montgomery and Barrett reduction), which also costs memory. However, no fancy reduction algorithm is required for LWR-based schemes due to its power-of-two moduli. All the factor mentioned above helps LWR-based schemes to a resource-scarce cryptographic application. There is already an implementation of MLWR-based KEM Saber in the application-specific integrated circuit (ASIC) available that uses the lowest area, lowest power, and low energy [48, 50].

There exist several physical attack *i.e.* side-channel attacks (SCA) and fault injection attacks(FIA) [10, 54, 63, 74, 84, 85, 94, 94] on both lattice-based signatures and KEMs. Since in this work, we are mostly concerned with KEMs, we will keep our discussion regarding physical attacks on PQC limited to KEMs only. Masking [34] is a well-known and provably secure countermeasure against SCA. The integration of the masking technique into a KEM scheme incorporates huge performance overhead. However, the performance overhead of the LWR-based KEM Saber after masking is comparatively less than the LWE-based scheme Kyber. State-of-the-art first-order masked Saber performs slightly better (4%) than Kyber [17, 56], but the performance difference between Saber and Kyber is considerably much for higher-order masking. State-of-the-art second-order and third-order masked Saber perform 53% and 48% better than Kyber, respectively [30, 75]. There are several components, such as arithmetic-to-Boolean conversion, Boolean-to-arithmetic conversion, compress, encode, and decode, that are cheaper when power-of-two modulus (used in LWR-based schemes) is used instead of prime modulus (used in LWE-based schemes). The secret and error of the

LWE instances in the LWE-based schemes are generated from the same seed. There is a fault attack on LWE-based KEM where the successfully injected fault in the seed results in an LWE instance where the error and secret are the same [97]. It breaks the hardness assumption of the LWE problem. However, as the LWR problem has no explicit error sampling, LWR-based schemes are naturally protected against this kind of fault attack.

Although NIST has selected Kyber as their first post-quantum secure KEM standard, several other standardization efforts are still in process, such as the Korean post-quantum competition (KPQC) [73]. It is currently in its second round. Smaug is based on a combination of MLWE and MLWR problems, and its design is inspired by the initial Scabbard paper [18]. Smaug [35] is one of the second-round KEM candidates. The currently selected PQC algorithms have been designed to address a variety of problems for many different applications. In particular, they have not been designed specifically for resource-constrained or Internet of Things (IoT) devices. Due to the rapid proliferation of these devices in almost every part of our digital ecosystem, they have become ubiquitous. However, due to their small sizes, it is often difficult to equip them with strong security measures. Due to these reasons often they become the weakest part of any security protocol. Therefore, there is an urgent need to design POC schemes specifically for these devices.

There are two ways to design lightweight schemes for resource-constrained devices: design new schemes (different design components, different parameters, etc.) from scratch for resource-constrained devices or implement the existing schemes in a lightweight manner by probably trading off efficiency or reducing the security. The work on designing lightweight PQC has just begun to gain attention [33, 45]. Recently, a lightweight MLWE-based KEM, Rudraksh, has been proposed for resource-constrained devices [76]. Therefore, we believe that our current work on studying the exploration of various design and parameter choices will have a valuable positive impact on the seamless transition from classical to PQC. We also think that this study will help construct efficient schemes and improve state-of-the-art practices. In fact, NIST historically includes and updates their already standardized cryptographic primitives with efficient ones. For example, NIST first standardized the elliptic curves digital signature algorithm in 1999 [88] and recommended 15 elliptic curves. After that, throughout the 2.5 decades, NIST has been modifying its recommended list of elliptic curves [86, 87], and the last modification was performed in 2023 [89]. Therefore, the progress achieved in this work will benefit to improve the state-of-the-art of post-quantum cryptography.

Contribution: We propose Scabbard, a suite with three new LWR-based key-encapsulation mechanisms (KEMs): Florete, Espada, and Sable. To implement these three schemes efficiently, we utilized one of the NIST's finalist KEMs, Saber's optimized software and hardware implementations, and modified it according to our scheme requirements. In this paper, we extend our earlier work, Scabbard's initial suite [18] by proposing parameters for several new security versions of previously proposed schemes and also implementing them in software. We also present unified hardware implementations of a (medium) security version of all these three schemes. Below, we briefly elaborate on all of our contributions.

- Florete is the first candidate of the Scabbard suite, and it is based on the ring-LWR (RLWR) hard problem. This KEM is designed to provide performance efficiency over the other LWE/LWR-based schemes. We proposed only the medium (NIST-3) security version in the initial paper. As an extension, we propose a low (NIST-1) and a high (NIST-5) security version of the Florete scheme in this paper. We show that all three security versions of Florete maintain the initial design rationale, and Florete performs better than most of the other lattice-based KEMs on the software platforms.

- Espada is the second scheme of this suite, and its hardness depends on the MLWR problem. However, the size of the polynomial used in this scheme is as small as 64, which is the first of its kind. The small polynomial size

makes this scheme suitable for resource-constraint devices and also highly parallelizable in hardware. In this paper, we propose a low and high-security version of the Espada. Together with the previous medium security version of Espada [18], this scheme now has three security versions, which broadens its applicability. We also show that all security versions of this scheme use less stack memory than most of the other lattice-based KEMs on the software platforms.

- We explored parameter sets similar to Saber's and obtained slightly reduced parameter sets that provide similar security. This new variant of Saber is the third scheme of our suite, Sable. It is based on the MLWR problem, and the polynomial used in this scheme is of the same size as Saber (256). This scheme can also be considered an efficient variant of Saber. We implemented all three security versions of Sable and show that it performs better than Saber and requires less stack memory on software platforms. We also show that Sable performs better than Saber and has less memory footprint when implemented on hardware platforms.

- We provide efficient implementations of all the schemes of Scabbard (also for all the security variants) on Intel's general-purpose processor and further optimize them with advanced vector instructions (AVX2). We also provide efficient implementations of Scabbard's schemes on the ARM Cortex-M4 platform. Low and high-security versions of Florete and Espada are implemented efficiently on all these software platforms for this paper. We compare our schemes with state-of-the-art schemes, such as the NIST standard Kyber, the Federal Office for Information Security's (BSI) standard Frodo, and several KPQC schemes on software platforms. We show that Florete performs better and Espada uses less amount of stack memory than most of the state-of-the-art KEMs on the Cortex-M4 platforms for all the security versions.

- MLWR-based scheme Saber is implemented using Toom-Cook (TC) based polynomial multiplication, but Chung et al. [36] improved its performance with a number-theoretic transformation (NTT) based polynomial multiplication and then Abdulrahman et al. [1] improved it even more. To show that this result can be extended for the schemes of our suite, we propose an implementation of Sable with number theoretic transformation (NTT) based polynomial multiplication on the Cortex-M4 platform and call it SableNTT. Our SableNTT not only performs better than SaberNTT (Saber with NTT-based polynomial multiplication) but also performs better than Kyber-Speed (Kyber's implementation optimized for speed).

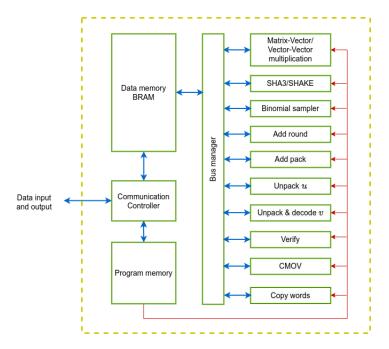

- We implement Florete, Espada, and Sable as full instruction-set coprocessor architectures on hardware (medium security version, NIST-3). By integrating and optimizing all building blocks, our design can compute all KEM operations in hardware: key generation, encapsulation, and decapsulation. As most individual components use non-multiples of 8-bit operands, hardware implementations become increasingly complex. We discuss our approach and optimized design, leading to reduced cycle counts and area counts. We utilize the polynomial multiplier architectures proposed in the initial paper. We show that our Sable implementation outperforms Saber, and all of the Scabbard schemes have comparable performance with state-of-the-art KEMs on hardware platforms.

# 2 PRELIMINARIES

# 2.1 Notation

We represent the set of integers modulo q by  $\mathbb{Z}_q$  for a positive integer q. We use  $\mathcal{R}_q^n$  to denote the quotient ring  $\mathbb{Z}_q[x]/(x^n+1)$  or  $\mathbb{Z}_q[x]/(x^n-x^{n/2}+1)$ . The ring with l length vectors over  $\mathcal{R}_q^n$  is denoted by  $(\mathcal{R}_q^n)^l$ , and the ring of  $m \times l$  matrices over  $\mathcal{R}_q^n$  is referred by  $(\mathcal{R}_q^n)^{m \times l}$ . We denote single polynomials by lower case letters and matrices

by upper case letters. We denote by  $\{x_i\}_{0 \le i \le t}$  to the set of t+1 elements  $\{x_0, x_1, \ldots, x_t\}$  from the same ring  $\mathcal{R}$ . If x is sampled from the set S according to the distribution  $\chi$ , then we use  $x \leftarrow \chi(S)$ . When x is generated from a seed seed x using some pseudo-random number generator according to the distribution  $\chi$  over the set S, then we denote it by  $x \leftarrow \chi(S)$ ; seed x. We denote the uniform distribution by x. The centered binomial distribution (CBD) with standard deviation  $\sqrt{\mu/2}$  is referred as  $\beta_{\mu}$ . We use x to indicate matrix-vector and vector-vector multiplications. Here, we use scaling down function x and x defined by x and during ties rounded upwards e.g. x and the rounding function x outputs the closest integer to the real number x and during ties rounded upwards e.g. x and x the multiplication of two x degree polynomials over the ring x is mentioned as x and x polynomial multiplication. We use x to represent multiplication between two polynomials, two vectors of polynomials, or one matrix and one vector of polynomials, depending on the context.

## 2.2 Learning with Rounding Problem

The decision version of LWE problem [98] states that given  $\mathbf{A} \leftarrow \mathcal{U}(\mathbb{Z}_q^{m \times l})$  and  $\mathbf{s}$  and  $\mathbf{e}$  are sampled according to following respective small distributions  $\beta_{\mu}(\mathbb{Z}_q^l)$  and  $\beta_{\mu}(\mathbb{Z}_q^m)$ , distinguishing between the LWE sample  $(\mathbf{A}, \mathbf{b} = \mathbf{A} \cdot \mathbf{s} + \mathbf{e}) \in \mathbb{Z}_q^{m \times l} \times \mathbb{Z}_q^m$  and  $(\mathbf{A}, \mathbf{b}') \in \mathbb{Z}_q^{m \times l} \times \mathbb{Z}_q^m$  is hard, when  $\mathbf{b}'$  is sampled uniformly from  $\mathbb{Z}_q^m$ . The LWR problem [8, 13] is a variation of the LWE problem, and the LWR sample is constructed as  $(\mathbf{A}, \mathbf{b} = \lfloor \mathbf{A} \cdot \mathbf{s} \rceil_p = \lfloor (q/p)\mathbf{A} \cdot \mathbf{s} \rceil) \in \mathbb{Z}_q^{m \times l} \times \mathbb{Z}_p^m$  where  $\mathbf{s} \leftarrow \beta_{\mu}(\mathbb{Z}_q^l)$ . Here, we do not need an explicit sampling of  $\mathbf{e}$  rather, it generates implicitly from rounding. The decision version of LWR problem states that given  $\mathbf{A} \in \mathbb{Z}_q^{m \times l}$ , it is hard to differentiate between the LWR sample  $(\mathbf{A}, \mathbf{b} = \lfloor \mathbf{A} \cdot \mathbf{s} \rceil_p) \in \mathbb{Z}_q^{m \times l} \times \mathbb{Z}_p^m$  and  $(\mathbf{A}, \mathbf{b}') \in \mathbb{Z}_q^{m \times l} \times \mathbb{Z}_p^m$ , where  $\mathbf{s} \leftarrow \beta_{\mu}(\mathbb{Z}_q^l)$  and  $\mathbf{b}' \leftarrow \mathcal{U}(\mathbb{Z}_p^m)$ .

Ring-LWE (RLWE) problem is a variant of the LWE problem based on structure lattice and is proposed in [81] to improve the practicality and efficiency of cryptographic schemes. In the RLWE,  $\mathbf{A}$ ,  $\mathbf{s}$ ,  $\mathbf{e}$ , and  $\mathbf{b}$  of the LWE are all replaced by polynomials of the ring  $(\mathcal{R}_q^n)$ . Similar to the RLWE, we can define the decision version of the RLWR problem, which states that the RLWR sample  $(\mathbf{a}, \mathbf{b} = \lfloor \mathbf{a} \cdot \mathbf{s} \rceil_p) \in \mathcal{R}_q^n \times \mathcal{R}_p^n$  and  $(\mathbf{a}, \mathbf{b}') \in \mathcal{R}_q^n \times \mathcal{R}_p^n$  are hard to distinguish, where  $\mathbf{s} \leftarrow \beta_\mu(\mathcal{R}_q^n)$  and  $\mathbf{b}' \leftarrow \mathcal{U}(\mathcal{R}_p^n)$ . The ring version offers better efficiency and practicality compared to the cryptosystem based on standard lattices of similar security. However, due to the presence of additional structures, many researchers are skeptical about their hardness. Therefore, as a trade-off between security and efficiency, the MLWR problem was introduced [78], which states that it is hard to differentiate between the MLWR sample  $(\mathbf{A}, \mathbf{b} = \lfloor \mathbf{A} \cdot \mathbf{s} \rceil_p) \in (\mathcal{R}_q^n)^{l \times l} \times (\mathcal{R}_p^n)^l$  and  $(\mathbf{A}, \mathbf{b}') \in (\mathcal{R}_q^n)^{l \times l} \times (\mathcal{R}_p^n)^l$ , where  $\mathbf{s} \leftarrow \beta_\mu((\mathcal{R}_q^n)^l)$  and  $\mathbf{b}' \leftarrow \mathcal{U}((\mathcal{R}_p^n)^l)$ . The rank of the underlying lattice of this MLWR problem is  $n \times l = n'$ . MLWR has less structure than RLWR, and the expensive matrix-vector multiplication of the standard LWR problem is replaced by efficient polynomial multiplication in the MLWR problem.

The module lattice-based problem can be used as generic construction, as all the MLWR problems with n = n' and l = 1 are classified as RLWR problems, and all the MLWR problems with n = 1 and l = n' are categorized as standard LWR problems. At this moment, there is no attack that provides any advantage to the adversary for MLWR or RLWR problems over the standard LWR problem. Therefore, if the rank of the underlying lattice problem is the same, then the security provided by the problem is the same. Henceforth, we will use the MLWR problem to denote different variations of the LWR problem.

#### 2.3 Construction of Generic LWR-based KEM

The LWR-based public-key encryption (PKE) scheme is used to construct an LWR-based key-encapsulation mechanism (KEM), and we illustrate the PKE scheme in Fig. 1. It consists of three algorithms (i) key-generation (LWR.PKE.KeyGen),

(ii) encryption (LWR.PKE.Enc), and (iii) decryption (LWR.PKE.Dec). Firstly, the LWR.PKE.KeyGen algorithm generates the public key and secret key pair. Secondly, the LWR.PKE.Enc algorithm uses the public key to encrypt the message m and to produce ciphertext. Lastly, the LWR.PKE.Dec algorithm decrypts the received ciphertext to the message m'.

Three quotient rings  $\mathcal{R}_q^n$ ,  $\mathcal{R}_p^n$ ,  $\mathcal{R}_t^n$  has been used here, and  $t . The constants <math>\epsilon_q = \log_2(q)$ ,  $\epsilon_p = \log_2(p)$ ,  $\epsilon_t = \log_2(t)$  are used to construct the constant polynomials  $h_2$ ,  $h_3$ , and by the vector of constant polynomials  $\mathbf{h}_1$ . Each coefficient of the constant polynomials  $h_2$  and  $h_3$  are  $2^{(\epsilon_q - \epsilon_p - 1)}$  and  $(2^{(\epsilon_p - B - 1)} - 2^{(\epsilon_p - \epsilon_t - 1)})$ , respectively. The value of each coefficient of the vector with constant polynomials  $\mathbf{h}_1$  is  $2^{(\epsilon_q - \epsilon_p - 1)}$ . The extendable-output function XOF:  $\{0, 1\}^{256} \longrightarrow \{0, 1\}^*$  is a pseudorandom number generator realized with SHAKE-128.

As the LWR-based schemes are not perfect, there is always a possibility of a decryption failure, i.e. the encrypted message m and decrypted message m' are not equal even when the scheme is executed properly. The decryption failure probability depends on the decryption noise d = v'' - v'. The decryption failure will not occur if the decryption noise d satisfies the following relation  $|d| \leq \frac{p}{2^{B+1}} (1 - \frac{1}{t})$  [29]. Therefore, if  $t = 2^{\epsilon}_t$  is large enough, then the decryption failure probability,  $\delta$ , becomes negligible. Eventually, it makes the corresponding LWR-based PKE scheme  $(1 - \delta)$  correct.

```

LWR.PKE.KevGen()

(1) \operatorname{seed}_{\pmb{A}} \leftarrow \mathcal{U}(\{0,\ 1\}^{256})

⊳ seed of the public matrix A

(2) \mathbf{A} \leftarrow \mathcal{U}((\mathcal{R}_a^n)^{l \times l}; \text{ seed}_{\mathbf{A}})

▶ A is generated using XOF function over seedA

(3) \operatorname{seed}_{\mathbf{s}} \leftarrow \hat{\mathcal{U}}(\{0, 1\}^{256})

▷ seed of the secret vector s

(4) \mathbf{s} \leftarrow \beta_{\mu}((\mathcal{R}_q^n)^l; \text{seed}_{\mathbf{s}})

\triangleright s is generated using CBD \beta_{\mu} over the XOF(seeds)

(5) \boldsymbol{b} \leftarrow ((\boldsymbol{A}^T \cdot \boldsymbol{s} + \boldsymbol{h_1}) \mod q) \gg (\epsilon_q - \epsilon_p) \in (\mathcal{R}_p^n)^l \quad \triangleright \text{ Performing rounding operation on } \boldsymbol{A}^T \cdot \boldsymbol{s} \text{ to create } \boldsymbol{b}

(6) return (pk = (seed_A, b), sk = (s))

\triangleright pk public key and sk secret key

LWR.PKE.Enc(pk = (seed_{\boldsymbol{A}}, \boldsymbol{b}), m \in R_2; r)

\triangleright pk is sent via insecure channel

(1) \mathbf{A} \leftarrow \mathcal{U}((\mathcal{R}_q^n)^{l \times l}; \text{ seed}_{\mathbf{A}})

\triangleright A is re-generated using XOF function over public seed<sub>A</sub>

(2) if: r is not specified:

(3) r \leftarrow \mathcal{U}(\{0, 1\}^{256})

⊳ seed of the s'

(4) \mathbf{s'} \leftarrow \beta_{u}((\mathcal{R}_{a}^{n})^{l}; r)

\triangleright s' is produced using CBD \beta_{\mu} over the XOF(seed<sub>s'</sub>)

(5) \boldsymbol{u} \leftarrow ((\boldsymbol{A} \cdot \boldsymbol{s}' + \boldsymbol{h}_1) \bmod q) \gg (\epsilon_q - \epsilon_p) \in (\mathcal{R}_p^n)^l

▷ Creates b' key contained part of the ciphertext

(6) v' \leftarrow \boldsymbol{b}^T \cdot (\boldsymbol{s}' \bmod p) + h_2 \in \mathcal{R}_p^n

(7) v \leftarrow (v' - 2^{\epsilon_p - B} m \mod p) \gg (\epsilon_p - \epsilon_t - B) \in \mathcal{R}_{2B,t}^n

▷ v message contained part of the ciphertext

(8) return c = (\boldsymbol{u}, v)

▷ Ciphertext c

\mathsf{LWR.PKE.Dec}(\mathit{sk} = \mathbf{s}, c = (\mathbf{u}, v))

\triangleright sk is stored and c is delivered via insecure channel

(1) v'' \leftarrow \boldsymbol{u}^T \cdot (\boldsymbol{s} \bmod p) + h_2 \in \mathcal{R}_p^n

(2) \quad m' \leftarrow (v'' - 2^{\epsilon_p - \epsilon_t - B}v + h_3) \text{ nod } p \gg (\epsilon_p - B) \in \mathcal{R}^n_{2B_t} \rhd \text{ Recover message by decoding the ciphertext } c

(3) return m'

```

Fig. 1. Generic LWR.PKE

The aforementioned LWR-based PKE scheme is indistinguishable against chosen plaintext attacks (IND-CPA) and can be converted to an indistinguishable under adaptive chosen ciphertext attacks (IND-CCA) KEM with a modified version of Fujisaki-Okamoto transformation [47] proposed by Hofheinz *et al*. [60]. Authors show that if the underlying PKE scheme is  $(1 - \delta)$  correct, then the KEM is also  $(1 - \delta)$  correct. The KEM is S bit post-quantum secure only when the failure probability  $\delta < 2^{-S}$  [64].

```

LWR.KEM.KeyGen()

(1) (pk\ sk) = ((seed_A,\ b),\ s) \leftarrow LWR.PKE.KeyGen() > The key-generation of the PKE is called to generate <math>(pk\ sk)

(2) pkh \leftarrow \mathcal{H}(pk)

\triangleright Hash of pk is part of the secret key

(3) z \leftarrow \mathcal{U}(\{0, 1\}^{256})

\triangleright random z is used by decapsulation in cases of decryption failure

(4) return (\overline{pk} = pk = (seed_A, b), \overline{sk} = (sk, z, pkh) = (s, z, pkh))

\triangleright public key pk, secret key sk

LWR.KEM.Encaps(\overline{pk} = (seed_{A}, b))

(1) m' \leftarrow \mathcal{U}(\{0, 1\}^{256})

⊳ message sampled

(2) m \leftarrow \operatorname{arrange\_msg}(m')

▶ message arranged for sending as input in LWR.PKE.Enc

(3) (\hat{K},r) \leftarrow \mathcal{G}(\mathcal{H}(pk),m)

\triangleright r is used as seed to generate s' in LWR. PKE. Enc during PKE encryption

(4) c \leftarrow \text{LWR.PKE.Enc}(pk, m; r)

\triangleright The encryption of the PKE is called to generate ciphertext c

\triangleright \hat{k} and ciphertext c are used to the generate shared key K

(5) K \leftarrow \mathsf{KDF}(\hat{K}, \mathcal{H}(c))

(6) return (c, K)

\triangleright ciphertext of the KEM is (c, K)

LWR.KEM.Decaps(\overline{sk} = (\mathbf{s}, z, pkh), pk = (seed_{\mathbf{A}}, \mathbf{b}), c)

(1) m'' \leftarrow LWR.PKE.Dec(s, c)

\triangleright The decryption of the PKE is called to decrypt c

(2) m' \leftarrow \text{original\_msg}(m'')

▷ Inverse of the arrange_msg to get back the original message

(3) (\hat{K}', r') \leftarrow \mathcal{G}(pkh, m') \triangleright r' is used to generate s' in re-encryption and \hat{K}' is used for shared key generation

(4) c_* \leftarrow \text{LWR.PKE.Enc}(pk, m'; r')

⊳ re-encryption with decrypted message m′

ightharpoonup equality check of the public ciphertext c and re-encrypted ciphertext c_*

(5) if: c = c_*

K \leftarrow \mathsf{KDF}(\hat{K}', \mathcal{H}(c))

\triangleright the equality check satisfies and K is the valid shared key

else:

(7)

K \leftarrow \mathsf{KDF}(z, \mathcal{H}(c))

\triangleright the equality check fails and K is an invalid shared key

(9) return (K)

```

Fig. 2. Generic LWR.KEM

The CCA-secure LWR-based KEM based on the CPA-secure LWR-based PKE is presented in Fig. 2. This KEM consists of three algorithms: (i) key-generation (LWR.KEM.KeyGen), (ii) encapsulation (LWR.KEM.Encaps), and (iii) decapsulation (LWR.KEM.Decaps). Here, the key-generation algorithm generates the public key and secret key pair  $(\overline{pk}, \overline{sk})$ . Secondly, the encapsulation algorithm uses the public key  $\overline{pk}$  to encrypt the message and to produce ciphertext c and the session key K. Lastly, in the decapsulation algorithm, we decrypt the received ciphertext to the message then we re-encrypt the decrypted message using the public key. If the re-encrypted ciphertext is equal to the received ciphertext, then the algorithm outputs the session key K; else outputs a random key. In these algorithms, we use two hash functions  $H: \{0, 1\}^* \longrightarrow \{0, 1\}^{256}$  realized by SHA3-256 and  $G: \{0, 1\}^* \longrightarrow \{0, 1\}^{512}$  implemented with SHA3-512. In LWR.KEM.Encaps and LWR.KEM.Decaps, the arrange\_msg:  $\{0, 1\}^{256} \longrightarrow \mathcal{R}_q^n$  function is used, which converts the 256 bits message to the message polynomial in  $\mathcal{R}_q^n$ . The inverse of arrange\_msg function or iginal\_msg:  $\mathcal{R}_q^n \longrightarrow \{0, 1\}^{256}$  is required in LWR.KEM.Decaps. It converts the message polynomial in  $\mathcal{R}_q^n$  to the 256 bits message.

# 3 SCABBARD SUITE OF LWR-BASED KEMS

We present the schemes of the suite Scabbard in this section. These schemes have been designed to improve the state-of-the-art of the efficient lattice-based KEM. This suite consists of three different designs of LWR-based KEMs (i) Florete, (ii) Espada, and (iii) Sable. All three schemes follow the generic LWR-based KEM construction. Florete is designed to achieve better performance. Espada is designed to use less memory footprint when implemented for resource-constrained devices and can also be implemented efficiently in hardware by using its high parallelism. Sable is

designed to provide a trade-off between performance and memory usage. As we can see from Fig. 1, for a LWR-based KEM, everything is the same except the choice of the ring/ module parameters n and l, the CBD parameter  $\mu$ , moduli q, p, t. Therefore, the polynomial multiplication, message encoding and decoding, and the secret sampler used in these three schemes are different. We will discuss these different aspects of the KEMs and describe their design rationale in the following sections. In Scabbard's KEMs design, one of the important aspects is we tried to maximally utilize already developed optimized software and hardware modules of LWR-based schemes.

#### 3.1 Florete: RLWR based KEM

This scheme is based on the RLWR hard problem, and therefore the ring/modulus parameter l is equal to 1. The public matrix A, secret vector s, and public key vector b are all polynomials and are elements of the ring  $\mathcal{R}_q^n$ . The parameter n and the ring  $\mathcal{R}_q^n$  vary for different security versions of Florete. We choose n=512 for the low-security version, n=768 for the medium-security version, and n=1024 for the high-security version. We are required to use an irreducible polynomial to construct the ring  $\mathcal{R}_q^n$  for the RLWR problem [81] (otherwise hardness of the RLWR problem reduces). Generally,  $x^n+1$  is chosen as an irreducible polynomial to construct the ring  $\mathcal{R}_q^n$ , but  $x^{768}+1$  is not an irreducible polynomial. Therefore, the irreducible polynomial  $(x^{768}-x^{384}+1)$  is applied to construct  $\mathcal{R}_q^n$  for n=768.

# **Polynomial Multiplication**

Polynomial multiplication is one of the fundamental operations performed during all three algorithms of a KEM, and it is one of the most time-consuming operations. The procedure of this multiplication depends on the two parameters of  $\mathcal{R}_q^n$ , which are n and modulus q. As mentioned earlier, we plan to utilize the optimized software and hardware modules developed for LWR-based schemes (e.g., Saber) during the NIST competition for easier adaptation. Polynomial multiplication is one of the modules whose implementation has been optimized in several works [16, 65, 82, 100]. LWR-based schemes can not use fast number theoretic transformation for polynomial multiplication because the modulus q and n are not co-prime (gcd(q, n) > 1). The next best option for the  $n \times n$  polynomial multiplication is utilizing Toom-Cook or Karatsuba multiplication, which has been used and optimized for the MLWR-based KEM Saber [82, 100]. Therefore, we have decided to re-purpose Saber's efficient 256 × 256 multiplier for Florete's  $n \times n$  multiplication. We use Saber's efficient 256 × 256 multiplier for implementing all three polynomial multiplications of Florete. The 256 × 256 polynomial multiplication of Saber is implemented by using a layer of Toom-Cook4 multiplication followed by two layers of Karatsuba multiplication, and the last stage is 16 × 16 schoolbook multiplication.

There is a small problem in using Saber's multiplier in Florete. We target to fit a coefficient of the multiplier polynomial fit into 16 bit space for efficient implementation in vector processors, small microcontrollers (e.g. Cortex-M4), etc. Even though the coefficients of the multiplier are less than or equal to 16 bit, we need to save some extra space when performing division by some g, which is a divisor of 2. The reason is  $gcd(g, q) \ge 2$ , and the inverse of g does not exist in  $\mathbb{Z}_q$ . In this case, let us assume g/g needs to be computed. If  $g = h * 2^w$ , where gcd(h, 2) = 1, then gcd(h, q) = 1 (as g is a power-of-2 modulus). We first compute  $g = h * 2^w$ , and then we multiply it with g and perform g right shift afterward. Therefore we need to store g0 extra bits while performing  $g \cdot g \cdot h^{-1}$ . There are several such divisions by g0, where g1 eneeded while using Toom-Cook multiplications. The maximum value of such g2 is equal to 1 for Toom-Cook 3-way multiplication, whereas g3 is equal to 3 for Toom-Cook 4-way multiplication. For the 512×512 polynomial multiplication, we use one extra layer of Karatsuba multiplication on top of Saber's 256 × 256 multiplication. Therefore, the g3 of the modulus g4 is g5 for Toom-Cook 3-way multiplication on top of the 256 × 256 multiplication. Here, the g6 need to be

$\leq$  12 (= 16 - 3 - 1) (It is not possible with Saber's modulus q, which is  $2^{13}$ ). We apply Toom-Cook 4-way multiplication on top of the 256  $\times$  256 multiplication for the 1024  $\times$  1024 polynomial multiplication. The modulus  $\epsilon_q$  need to be  $\leq$  10 (= 16 - 3 - 3) in this case.

Now, we will compare the number of  $256 \times 256$  polynomial multiplications used in Saber with Florete. As Saber is based on the MLWR problem, it has a module structure and the parameter l > 1. Therefore several  $256 \times 256$  polynomial multiplications are needed for matrix-vector multiplications (e.g.  $\mathbf{A} \cdot \mathbf{s}$ ) and vector-vector multiplications (e.g.  $\mathbf{b}^T \cdot \mathbf{s}'$ ), which are used in all three (key-generation, encapsulation, and decapsulation) algorithms of all three security versions of Saber. These exact numbers are provided in Table 1. For example, the key-generation, encapsulation, and decapsulation algorithm of the medium-security version of Saber requires 9, 12, and 15 polynomial multiplication ( $256 \times 256$ ), respectively.

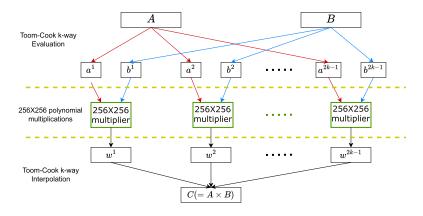

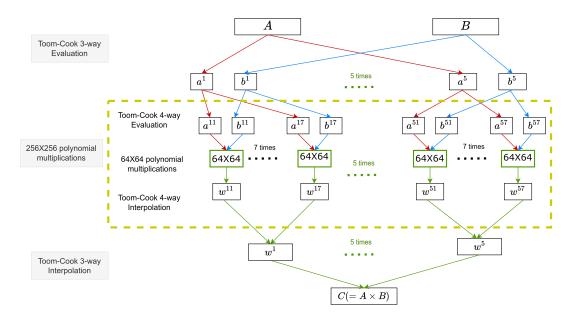

Fig. 3. Polynomial multiplication used in Florete. The values of k for low, medium, and security versions of Florete are 2, 3, and 4, respectively.

Florete is an RLWR-based scheme. So, all matrix-vector multiplications (e.g.  $\boldsymbol{A} \cdot \boldsymbol{s}$ ) and vector-vector multiplications (e.g.  $m{b}^T \cdot m{s}'$ ) are just a single polynomial multiplication in Florete. The key-generation, encapsulation, and decapsulation algorithms of Florete require 1, 2, and 3  $n \times n$  polynomial multiplications, respectively. As mentioned earlier, we apply an extra layer of Karatsuba multiplication on top of Saber's  $256 \times 256$  multiplication for  $512 \times 512$  polynomial multiplication of the low-security version of Florete. Here, we perform 3 256 × 256 polynomial multiplications for a 512 × 512 polynomial multiplication (as displayed in Fig. 3). There are some other steps which are interpolation and reduction, to complete the whole multiplication. However, the performance cost of these steps is negligible compared to the total number of polynomial multiplications. Therefore, the low-security version of Florete needs 3, 6, and 9 256 × 256 multiplications for the key-generation, encapsulation, and decapsulation algorithms, respectively. For a  $768 \times 768$  polynomial multiplication, an extra layer of Toom-Cook 3-way multiplication is added on top of  $256 \times 256$ multiplication. As we are applying Toom-Cook 3-way multiplication for 768 × 768 polynomial multiplication, we need to perform 5 = (2 \* 3 - 1),  $256 \times 256$  polynomial multiplications (as portrayed in Fig. 3). We are applying an extra layer of Toom-Cook 4-way multiplication for  $1024 \times 1024$  polynomial multiplication. So, we need to perform 7 = (2 \* 4 - 1),  $256 \times 256$  polynomial multiplications for a single  $1024 \times 1024$  multiplication (as shown in Fig. 3). We provide the number of 256 × 256 polynomial multiplications required by all the algorithms of all the security versions of Florete in Table 1. We have included the performance of multiplications used in Florete and Saber on the Cortex-M4 platform. More

detailed performance results are given in Sec. 5. We can see from Table 1 that the number of 256 × 256 multiplications

| Scheme<br>Name | Security | #256 × 2 | 56 multipl | lications | Multiplication on Cortex-M4<br>(x1000 clock cycles) |        |        |  |

|----------------|----------|----------|------------|-----------|-----------------------------------------------------|--------|--------|--|

| Ivallie        | ievei    | KeyGen   | Encaps     | Decaps    | KeyGen                                              | Encaps | Decaps |  |

|                | Low      | 3        | 6          | 9         | 121                                                 | 243    | 364    |  |

| Florete        | Medium   | 5        | 10         | 15        | 202                                                 | 405    | 607    |  |

|                | High     | 7        | 14         | 21        | 300                                                 | 600    | 900    |  |

|                | Low      | 4        | 6          | 8         | 149                                                 | 223    | 298    |  |

| Saber          | Medium   | 9        | 12         | 15        | 334                                                 | 446    | 557    |  |

|                | High     | 16       | 20         | 24        | 594                                                 | 743    | 891    |  |

Table 1. Comparison of the usage of  $256 \times 256$  multiplications in the algorithms of Florete with Saber.

used in the key-generation algorithm of the low-security version of Florete is less than the low-security version of Saber. The number of  $256 \times 256$  multiplications used in the encapsulation algorithm of the low-security version of Florete is the same as the low-security version of Saber, whereas the decapsulation algorithm of the low-security version of Florete uses 1 more  $256 \times 256$  polynomial multiplication than Saber. For the medium security, the number of  $256 \times 256$  multiplications used in the key-generation and encapsulation algorithms of Florete is less than Saber. The number of  $256 \times 256$  multiplications used in the decapsulation algorithm of the medium-security version of Florete is the same as Saber. Lastly, for the high security, the number of  $256 \times 256$  multiplications used in all the algorithms of Florete is less than Saber.

## Message Encoding and Decoding

Message encoding and decoding are done in the LWR-based KEM described in Fig. 2 by using the arrange\_msg and original\_msg, respectively. The secret payload/message (m') size is 256 bits in all the security versions of Florete, and the size of the polynomial is at least twice. So, we repeat the secret payload multiple times with the help of the arrange\_msg $\{0, 1\}^{256} \longrightarrow \{0, 1\}^n$  function and make its bit size the same as the size of any polynomial in the corresponding security version of Florete.

$$\text{arrange\_msg}(m') = \begin{cases} m' || m' & \text{if } n = 512 \\ m' || m' || m' & \text{if } n = 768 \\ m' || m' || m' || m' & \text{if } n = 1024 \end{cases}.$$

The original\_msg function is the counter function of arrange\_msg function and is used in the decryption algorithm. We define the original\_msg function for each security version of Florete below. For the low security version of Florete, the original\_msg :  $\{0, 1\}^{512} \longrightarrow \{0, 1\}^{256}$  is original\_msg(m'') = m' and  $b \in \{0, 1, ..., 255\}$

$$m'[b] = \begin{cases} 0 & \text{if } m''[b] + m''[b + 256] \le 0 \\ 1 & \text{else} \end{cases}.$$

For the medium security version of Florete, the original\_msg :  $\{0, 1\}^{768} \longrightarrow \{0, 1\}^{256}$  is original\_msg(m'') = m' and  $b \in \{0, 1, ..., 255\}$

$$m'[b] = \begin{cases} 0 & \text{if } m''[b] + m''[b+256] + m''[b+512] \le 1 \\ 1 & \text{else} \end{cases}.$$

For the high security version of Florete the original\_msg:  $\{0, 1\}^{1024} \longrightarrow \{0, 1\}^{256}$  is original\_msg(m'') = m' and  $b \in \{0, 1, ..., 255\}$

$$m'[b] = \begin{cases} 0 & \text{if } m''[b] + m''[b + 256] + m''[b + 512] \\ & + m''[b + 768] \le 2 \\ 1 & \text{else} \end{cases}.$$

The repetition of message bits during encoding helps to reduce the failure probability and eventually helps to achieve more security. Therefore, Florete can achieve the same level of security with a smaller modulus. Therefore, we can reduce the three modulus size  $\epsilon_q < \epsilon_p < \epsilon_t$  even further than Saber (or Kyber). It reduces the requirement of pseudo-random bytes to create the public matrix A in Florete compared to Saber, which has been supplied in Table 2. It eventually helps to reduce the public key size of Florete compared to Kyber (the exact public key sizes are shown in Table 3). Kindly note that we have not applied any error-correction code to reduce failure probability RLWE-based scheme LAC [80], as it leads to several attacks [41, 51, 55].

#### **Secret Distribution**

The coefficient of the secret s (or s') is sampled from centered binomial distribution,  $\beta_1$ . Therefore possible values of a coefficient of s (s') are  $\{-1, 0, 1\}$ . It enables the possibility of very fast multiplication in the processors. In this case, multiplication can be replaced by addition and subtraction only. This method is highly advantageous to the processor, where multiplication is way more costlier than addition or subtraction (e.g. MSP430 microcontrollers). Saber's secret coefficients are from  $\beta_5$ ,  $\beta_4$ , and  $\beta_3$  for low, medium, and high-security versions, respectively. In comparison, the secret coefficients of Florete are from  $\beta_1$  for all the security versions. It leads less pseudo-random number requirements for Florete than Saber, which has been provided in Table 2. We have shown the required clock cycles to generate the matrix A and the secret s for all the versions of Florete and Saber on the Cortex-M4 platform. More detailed performance analyses are shown in Sec. 5. The coefficients of the secret can be represented by 2 bits, which reduces the memory requirement to store the secret s (s') in hardware compared to Saber (Saber needs 4 bits to store a coefficient of s). It ultimately helps Florete to have smaller secret key sizes than Saber for all the security versions (the exact numbers are shown in Table 3).

| Scheme<br>Name | Security<br>level | pseudo-ra | andom bytes   | Performance on Cortex-M4<br>(x1000 clock cycles) |               |  |

|----------------|-------------------|-----------|---------------|--------------------------------------------------|---------------|--|

| Name           | level             | matrix A  | secret s (s') | matrix A                                         | secret s (s') |  |

|                | Low               | 704       | 128           | 68                                               | 18            |  |

| Florete        | Medium            | 960       | 192           | 83                                               | 32            |  |

|                | High              | 1280      | 256           | 110                                              | 34            |  |

|                | Low               | 1664      | 640           | 137                                              | 76            |  |

| Saber          | Medium            | 3744      | 768           | 313                                              | 72            |  |

|                | High              | 6656      | 768           | 545                                              | 75            |  |

Table 2. Comparison of pseudo-random byte used in Florete with Saber.

The centered binomial distribution is proposed by Alkim *et al.* [7] to replace the costly Gaussian distribution, which is hard to implement in constant-time. This distribution is used in NIST standardized Kyber and third-round finalist Saber. Therefore, we have decided to sample the secret using CBD. Here, we refrained from taking any aggressive decision for secret distribution, eg. fixing the hamming weight of the secret key like LWR-based scheme Round5 [23] or fixing the

weight of the secret vector like NTRU Prime [20]. This decision has been taken to avoid any new adversarial attack due to the choice of secret distribution. The Saber team proposed a lightweight version of Saber, named uSaber [14] 2 bits secret key coefficient. More specifically, they use a uniform distribution over 2 bits numbers. There is another lattice-based scheme proposed in the ongoing Korean PQC competition [73], called Smaug [35]. The secret key of this specific scheme has each coefficient sampled from the set  $\{-1, 0, 1\}$ .

# 3.2 Espada: MLWR based KEM

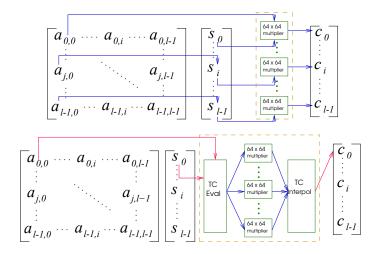

The next LWR-based KEM in the Scabbard is Espada. It uses MLWR as a hard problem, and this KEM also takes advantage of module lattices like Saber and Kyber. Therefore the matrix A is an element of the ring  $(\mathcal{R}_q^n)^{l\times l}$ , and the secret vector s is an element of the ring  $(\mathcal{R}_q^n)^l$ . However, the underlying quotient ring is  $\mathcal{R}_q^{64}$  (n=64) constructed by the help of cyclotomic polynomial  $(x^{64}+1)$ . Therefore the polynomial size of Espada is just 64, which is very small compared to the size of the polynomial in Saber or Kyber (their polynomials are of size 256). This design choice allows Espada to use less stack memory while executing in a reasonable amount of clock cycles when implemented in embedded devices, such as Cortex M4 microcontrollers. It can also be implemented in hardware with less area due to its small polynomial size. This scheme can also be implemented in hardware very fast by using multiple polynomial multiplication instances. It provides the flexibility to implement Espada using one or many polynomial multipliers depending on the application's requirements (as shown in Fig. 4), which is not possible for Saber or Kyber.

**Polynomial Multiplication** The ring modulus  $q=2^{15}$  for each version of Espada. Since  $\epsilon_q(=\log_2(q))=15$  and we want to restrict each coefficient of the polynomial in 16 bits of word length (described in Sec. 3.1), we cannot use Toom-Cook 4-way multiplication for the  $64\times64$  polynomial multiplication of Espada. So, we use a combination of Karatsuba and schoolbook multiplication for the  $64\times64$  polynomial multiplications. During the implementation of the matrix-vector or vector-vector multiplication, we take advantage of the lazy interpolation technique [82]. However, the interpolation step in Karatsuba multiplication is smaller than the interpolation step in Toom-Cook k-way multiplication for k>2. The lazy interpolation technique helps to significantly improve the performance of matrix-vector and vector-vector multiplication because the vector dimension l of Espada is large.

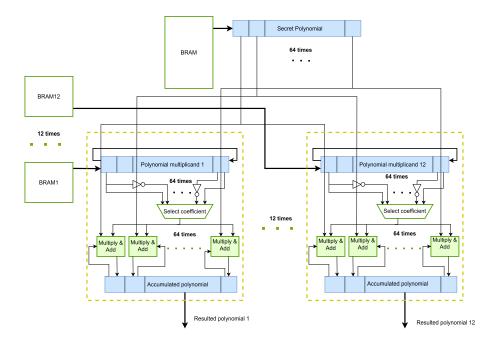

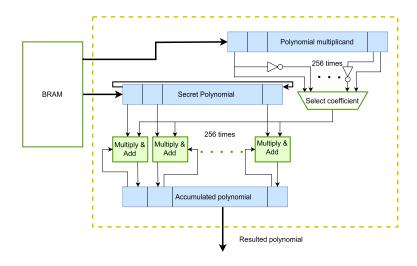

Saber or Kyber use  $256 \times 256$  polynomial multiplication, and utilizing multiple instances of this multiplication is expensive in hardware. In fact, Mera et~al.~[83] developed Saber's  $256 \times 256$  multiplier by using 7 parallel  $64 \times 64$  polynomial multiplication instances together with an evaluation (TC Eval) and interpolation (TC Inter) steps of Toom-Cook 4-way algorithm (as shown in Fig. 4). [83] shows that the  $64 \times 64$  schoolbook multiplication is already very fast in hardware. However, this implementation uses 28 DSP just for one  $256 \times 256$  multiplication. Therefore, using multiple such multiplications will make the whole design area expensive, and then there will not be much space left for other components. In Espada, the length of the polynomial is as small as 64, so the vector dimension l needs to be quite large in order to achieve the desired security. The values of l are 10, 12, and 15, corresponding to low, medium, and high-security versions of Espada (shown in Table 3). Therefore, this scheme can also be implemented in hardware very fast by employing l (the length of the vector) parallel  $64 \times 64$  polynomial multiplication instances while computing the matrix-vector (e.g.:  $\mathbf{A} \cdot \mathbf{s}$ ) and vector-vector (e.g.:  $\mathbf{b}^T \cdot \mathbf{s}'$ ) multiplication. In this work, we also utilize  $64 \times 64$  schoolbook multiplication as one polynomial multiplication in hardware in Espada. By design Espada has extremely parallelizable matrix-vector and vector-vector multiplication in hardware, and it aids Espada to achieve high throughput in hardware.

## Message Encoding and Decoding

Fig. 4. Comparison between the application of parallel  $64 \times 64$  polynomial multiplication in Espada (top) and Saber (bottom). The blue line represents parallel execution, and the red line denotes serial execution.

The degree of the polynomial for all the versions of Espada is 64, and the secret payload (m') size is 256 bits. So, we use one coefficient to hide multiple (4) bits of secret payloads and B = 4. Here, the function arrange\_msg :  $\{0, 1\}^{256} \longrightarrow \{0, 1, 2, \ldots, 15\}^{64}$  is arrange\_msg(m') = m and  $b \in \{0, 1, \ldots, 64\}$ , then m[b] = m'[4 \* b] || m'[4 \* b + 1] || m'[4 \* b + 2] || m'[4 \* b + 3]. The function original\_msg :  $\{0, 1, 2, \ldots, 15\}^{64} \longrightarrow \{0, 1\}^{256}$  is original\_msg(m'') = m' and  $b \in \{0, 1, \ldots, 255\}$ , then  $m'[b] = (m''[b_1] \gg b_2) \& 1$ , where  $b = 4 * b_1 + b_2$ .

# **Secret Distribution**

In Espada, the coefficient of the secret s(s') is sampled according to the centered binomial distribution,  $\beta_3$ , for all the security versions. So, each secret coefficient is from the set  $\{-3, -2, \dots, 3\}$ . These secret coefficients can be represented by 3 bits, but the unpacking becomes fairly costly in that case. Therefore, the cost-effective way to store the secret s is to reserve 4 bits for each coefficient.

# 3.3 Sable: an Alternate Saber

Sable can be viewed as an improved version of Saber. Like Saber, Sable uses the MLWR structure, and the underlying quotient ring of Sable is the same as Saber ( $x^{256} + 1$ ). In this scheme, we have readjusted the parameters of Saber. The modulus size of the quotient ring q for Sable is  $2^{11}$ , and it is smaller than Saber's modulus  $q = 2^{13}$  (shown in Table 3). The public-key modulus p of Sable ( $2^9$ ) is also smaller than Saber ( $2^{10}$ ) for the low and medium security version, which assists in Sable having shorter public keys (given in Table 3).

# **Polynomial Multiplication**

Sable can utilize the same  $256 \times 256$  polynomial multiplication, as the modulus is less than 13 bits. Also, the polynomial multiplication of Sable is less costly than Saber in hardware, thanks to its smaller modulus.

# Message Encoding and Decoding

The degree of the polynomial for all the versions of Sable is 256, which is the same as the secret payload (m'). Therefore, we use one coefficient for a single bit of secret payloads and B = 1. The function arrange\_msg :  $\{0, 1\}^{256} \longrightarrow \{0, 1\}^{256}$  is arrange\_msg(m') = m' = m and the function original\_msg :  $\{0, 1\}^{256} \longrightarrow \{0, 1\}^{256}$  is arrange\_msg(m'') = m'' = m'.

#### **Secret Distribution**

Like Florete, a coefficient of the secret vector is sampled from the CBD  $\beta_2$  in every version of Sable. Therefore, one secret coefficient can be stored as a 2 bits number, allowing Sable to have smaller secret keys. All these choices help Sable to reduce stack memory requirements when implemented in a microcontroller, and area requirements when implemented in hardware. More details regarding implementation are provided in Sec. 5 & 6.

## 4 PARAMETER SET

The lattice-based schemes whose hardness depends on the LWE problems or its variant, such as the (M/R)LWR problem, are solved by utilizing lattice reduction algorithms that construct a "sufficient orthogonal" basis from the given lattice. Currently the best-known algorithm for lattice reduction is the BKZ algorithm. Here, given one lattice or a basis of lattice, the attacker needs to find the block size or sub-lattice size required for recovering the shortest vector of the lattice while performing the BKZ algorithm. The security of a lattice-based scheme depends on the cost of the execution time of the BKZ algorithm on the underlying lattice. The BKZ algorithm also calls the shortest vector problem (SVP) solving oracle on sub-lattices. The cost of solving the LWE problem with block size  $\beta$  depends on the number of SVP oracle calls made by the BKZ algorithm and the cost of solving each SVP for dimension  $\beta$ . This cost is approximately  $2^{c\beta+o(\beta)}$  [6], where the value of c is approximately 0.292 in classical settings and 0.265 with Grover's speed-up algorithm [52] in quantum settings.

Dachman-Soled et al. [38] has introduced leaky-LWE-Estimator, the state-of-the-art toolkit to estimate the hardness of the underlying LWE problem for lattice-based schemes. This tool takes the n = dimension of the lattice, q = modulus,  $D_e$  = error distribution,  $D_s$  = secret distribution, and outputs the block size  $\beta$ . We have utilized this toolkit for the security estimation of our schemes. The post-quantum bit security is estimated as  $0.265 * \beta$  [5], and classical bit security is estimated as  $0.292 * \beta$  [15]. Since the post-quantum security is lower than classical security (0.292 \*  $\beta$  bit secure, we have mentioned only the post-quantum (PO) security of our schemes in Table 3.

We present the parameter sets of our schemes for three security levels in Table 3. For security level 1, PQ security of each of the KEMs is  $\geq 2^{100}$ , for security level 3, PQ security is  $\geq 2^{128}$ , and for security level 5, PQ security is  $\geq 2^{160}$ . LWE-based cryptosystem has another security factor which is failure probability. However, another type of attack is possible on LWR or LWR-based cryptographic schemes that exploit failure probability during decryption. As mentioned in Sec. 2.3, the failure probability should be  $\leq 2^{-S}$ , where S is the security of the KEM to maintain the IND-CCA security of the KEM. Therefore, for security level 1, 3, 5 in contrast with the PQ security, the failure probability we maintain  $\leq 2^{-100}$ ,  $\leq 2^{-128}$ ,  $\leq 2^{-160}$ , respectively for each of the KEMs. NIST security levels 1, 3, and 5 are represented by low, medium, and high-security levels in Table 3.

Table 3. Compare parameters and key sizes of Scabbard suite with Saber

| Scheme    | Security | Ring | g/Module | PQ        | Failure      |                                   | 1.11    | CBD              | n 1:     | Key sizes                  | for          |

|-----------|----------|------|----------|-----------|--------------|-----------------------------------|---------|------------------|----------|----------------------------|--------------|

| Name      | level    |      | ameters  | Security  |              | Mo                                | oduli   | $(\beta_{\eta})$ | Encoding | KEM (Byt                   |              |

|           |          | n:   | 512      | ,         |              | $\epsilon_q$ :                    | 11      | - 7.             |          | Public key:                | 608          |

|           | Low      |      |          | $2^{104}$ | $2^{-138}$   | $\epsilon_p$ :                    | 9       | $\eta = 1$       | B=1      | Secret key:                | 800          |

|           |          | 1:   | 1        |           |              | $\epsilon_t$ :                    | 2       |                  |          | Ciphertext:                | 768          |

|           |          | n:   | 768      |           |              | $\epsilon_q$ :                    | 10      |                  |          | Public key:                | 896          |

| Florete   | Medium   |      |          | $2^{157}$ | $2^{-131}$   | $\epsilon_p$ :                    | 9       | $\eta = 1$       | B=1      | Secret key:                | 1152         |

|           |          | 1:   | 1        |           |              | $\epsilon_t$ :                    | 3       |                  |          | Ciphertext:                | 1248         |

|           |          | n:   | 1024     | 220       | 165          | $\epsilon_q$ :                    | 10      |                  |          | Public key:                | 1184         |

|           | High     |      |          | $2^{220}$ | $2^{-165}$   | $\epsilon_p$ :                    | 9       | $\eta = 1$       | B=1      | Secret key:                | 1504         |

|           |          | l:   | 1        |           |              | $\epsilon_t$ :                    | 4       |                  |          | Ciphertext:                | 1792         |

|           | ,        | n:   | 64       | 2101      | 2-148        | $\epsilon_q$ :                    | 15      |                  | <b>.</b> | Public key:                | 1072         |

|           | Low      | 1    | 10       | 2101      | 2 140        | $\epsilon_p$ :                    | 13      | $\eta = 3$       | B=4      | Secret key:                | 1456         |

|           |          | l:   | 10       |           |              | $\epsilon_t$ :                    | 2       |                  |          | Ciphertext:                | 1088         |

| E an a da | Madium   | n:   | 64       | 2128      | 2-167        | $\epsilon_q$ :                    | 15      | 2                | D 4      | Public key:                | 1280         |

| Espada    | Medium   | 1:   | 12       | 2         | 2            | $\epsilon_p$ :                    | 13      | $\eta = 3$       | B=4      | Secret key:                | 1728<br>1304 |

|           |          | n:   | 64       |           |              | $\epsilon_t$ :                    | 3<br>15 |                  |          | Ciphertext: Public key:    | 1592         |

|           | High     | 11.  | 04       | 2168      | 2-162        | $\epsilon_q$ :                    | 13      | $\eta = 3$       | B=4      | Secret key:                | 2136         |

|           | High     | 1:   | 15       | 4         | 2            | $\epsilon_p$ : $\epsilon_t$ :     | 5       | $\eta - 3$       | D-4      | Ciphertext:                | 1632         |

|           |          | n:   | 256      |           |              | $\frac{\epsilon_l}{\epsilon_q}$ : | 11      |                  |          | Public key:                | 608          |

|           | Low      | 11.  | 230      | 2104      | $2^{-139}$   | $\epsilon_p$ :                    | 9       | $\eta = 1$       | B=1      | Secret key:                | 800          |

|           | Low      | 1:   | 2        | -         | 2            | $\epsilon_{p}$ :                  | 2       | ', -             | Б 1      | Ciphertext:                | 672          |

|           |          | n:   | 256      |           |              | $\frac{\epsilon_l}{\epsilon_q}$ : | 11      |                  |          | Public key:                | 896          |

| Sable     | Medium   |      |          | $2^{169}$ |              | $\epsilon_p$ :                    | 9       | $\eta = 1$       | B=1      | Secret key:                | 1152         |

|           |          | 1:   | 3        |           |              | $\epsilon_t^P$ :                  | 4       | ,                |          | Ciphertext:                | 1024         |

|           |          | n:   | 256      |           |              | $\epsilon_q$ :                    | 11      |                  |          | Public key:                | 1312         |

|           | High     |      |          | $2^{203}$ | $2^{-208}$   | $\epsilon_p$ :                    | 10      | $\eta = 1$       | B=1      | Secret key:                | 1632         |

|           | _        | 1:   | 4        |           |              | $\epsilon_t$ :                    | 2       |                  |          | Ciphertext:                | 1376         |

|           |          | n:   | 256      |           |              | $\epsilon_q$ :                    | 13      |                  |          | Public key:                | 672          |

|           | Low      |      |          | $2^{107}$ | $2^{-120}$   | $\epsilon_p$ :                    | 10      | $\eta = 5$       | B=1      | Secret key:                | 992          |

|           |          | 1:   | 2        |           |              | $\hat{\epsilon_t}$ :              | 2       |                  |          | Ciphertext:                | 736          |

|           |          | n:   | 256      |           |              | $\epsilon_q$ :                    | 13      |                  |          | Public key:                | 992          |

| Saber     | Medium   |      |          | $2^{172}$ | $2^{-136}$   | $\epsilon_p$ :                    | 10      | $\eta = 4$       | B=1      | Secret key:                | 1440         |

|           |          | 1:   | 3        |           |              | $\epsilon_t$ :                    | 3       |                  |          | Ciphertext:                | 1088         |

|           |          | n:   | 256      | 227       | 165          | $\epsilon_q$ :                    | 13      |                  |          | Public key:                | 1312         |

|           | High     | _    |          | $2^{236}$ | $2^{-165}$   | $\epsilon_p$ :                    | 10      | $\eta = 3$       | B=1      | Secret key:                | 1760         |

|           |          | 1:   | 4        |           |              | $\epsilon_t$ :                    | 5       |                  |          | Ciphertext:                | 1472         |

|           |          | n:   | 256      | - 107     | $2^{-139}$   | q:                                | 3329    | $\eta_1 = 3$     |          | Public key:                | 800          |

|           | Low      |      |          | $2^{107}$ | 2-139        | $\epsilon_p$ :                    | 10      |                  | B=1      | Secret key:                | 1632         |

|           |          | l:   | 2        |           |              | $\epsilon_t$ :                    | 3       | $\eta_2 = 2$     |          | Ciphertext:                | 768          |

| 77. 1     | N C - 12 | n:   | 256      | 2166      | 0-164        | q:                                | 3329    | $\eta_1 = 2$     | D 4      | Public key:                | 1184         |

| Kyber     | Medium   |      |          | 2100      | $2^{-164}$ 6 | $\epsilon_p$ :                    | 10      |                  | B=1      | Secret key:                | 2400         |

|           |          | 1:   | 3        |           |              | $\epsilon_t$ :                    | 3       | $\eta_2 = 2$     |          | Ciphertext:                | 1088         |

|           | U;l.     | n:   | 256      | $2^{232}$ | $2^{-174}$   | q:                                | 3329    | $\eta_1 = 2$     | D. 1     | Public key:                | 1568         |

|           | High     | 1.   | 1        | 2202      | 4 1,1        | $\epsilon_p$ :                    | 10      | n 2              | B=1      | Secret key:<br>Ciphertext: | 3168         |

|           |          | l:   | 4        |           |              | $\epsilon_t$ :                    | 4       | $\eta_2 = 2$     |          | Cipilertext:               | 1568         |

For comparing the key sizes of our schemes with Saber and Kyber, we also include the parameter sets of Saber in Table 3. The public key and secret key sizes of Florete are smaller than Saber, while the size of the ciphertext is slightly larger for Florete than Saber for all three security levels. The public key and secret key sizes of Florete are also smaller than Kyber for all three security versions. Even, the size of the ciphertext is the same for the low-security version of Florete and Kyber. Due to larger moduli and vector dimensions, the public key, secret key, and ciphertext sizes are bigger in Espada than in Saber for the same security level. However, the secret key size of Espada is smaller in Espada than in Kyber for all the security versions. In the case of any of the three security levels of Sable, the sizes of the public key, secret key, and ciphertext are smaller than in the case of the same security level of Saber and Kyber.

#### 5 SOFTWARE IMPLEMENTATION

In this section, we describe the implementation results of our schemes on the software platforms. We have implemented Scabbard's schemes on general-purpose intel processors using C and advanced vector instructions (AVX2). We also implemented Scabbard's schemes on the NIST-recommended ARM Cortex-M4 platform. As most of the PQC schemes are implemented in these two software platforms, we can compare the implementation results of our schemes with the state-of-the-art schemes and demonstrate the efficiency of our scheme.

#### 5.1 Results in C and AVX2

To implement our schemes on general-purpose intel processors using C and advanced vector instructions (AVX2), we use the GCC 6.5 compiler and optimization flags-O3. We also used -fomit-frame-pointer on an Intel (R) Core (TM) i7-6600 CPU running in 2.60GHz, and disabled hyperthreading, turbo-boost, and multicore support in our system following the standard practice. The performance results of Scabbard's schemes in portable C and AVX2 implementations are presented in Table 4. For comparison, we also include the performances of C and AVX2 implementation of NIST's third-round finalist Saber and NIST's standard Kyber together with BSI recommended [32] Frodo [29] (also in consideration of ISO for standard [53]) in the tables. This table also compares KPQC schemes Smaug [35], NTRU+ [69], and Tiger [90], which have been advanced to the second-round [73].

As we can see from Table 4, the performance of all three algorithms (key generation, encapsulation, and decapsulation) of Florete and Sable is better than all the other schemes, including Kyber, Frodo, and Saber, for all the security versions on C. All three algorithms of Florete and Sable perform better than Saber and Smaug in the AVX2 implementation as well for all the security versions. Algorithms of Espada take approximately twice as many clock cycles as Saber for all the security levels due to the use of more pseudo-random numbers and more  $64 \times 64$  multiplications. However, the slowdown factor for Espada's performance compared to Saber's decreases as the security order increases because the underlying lattice rank  $l \times n$  decreases in Espada compared to Saber as the security increases.

## 5.2 Results in Cortex-M4

We have implemented Scabbard's schemes on the NIST-recommended 32-bit ARM Cortex-M4 microcontroller (STM32F407-DISCOVERY development board) using the PQM4 [67] framework. For compilation, we have used arm-none-eabi-gcc compiler version 4.9.3. The PQM4 library uses a 24 MHz system clock to calculate clock cycles. The results of the implementations of Scabbard's schemes in a Cortex-M4 platform are presented in Table 5. We have also included the clock cycles spent in hashing, polynomial multiplication, and the remaining operations in this table. We have compared our implementations of Scabbard with the state-of-the-art schemes in Table 6. This table contains two implementations of Saber, one with NTT multiplication (SaberNTT [14]) and another with Toom-cook multiplication (Saber [14]). For

Table 4. Comparing performance of Scabbard schemes with Saber and kyber in portable C and AVX2 implementations

| Scheme Name | Security | C (X10 | 000 clock o | ycles) | AVX (X | 1000 clock | cycles) |

|-------------|----------|--------|-------------|--------|--------|------------|---------|

| Scheme Name | level    | KeyGen | Encaps      | Decaps | KeyGen | Encaps     | Decaps  |

|             | Low      | 43     | 66          | 83     | 31     | 43         | 47      |

| Florete     | Medium   | 64     | 104         | 143    | 45     | 66         | 75      |

|             | High     | 80     | 140         | 181    | 52     | 83         | 97      |

|             | Low      | 159    | 173         | 193    | 148    | 158        | 153     |

| Espada      | Medium   | 224    | 234         | 232    | 203    | 215        | 210     |

|             | High     | 336    | 351         | 352    | 310    | 324        | 317     |

|             | Low      | 55     | 69          | 76     | 38     | 45         | 41      |

| Sable       | Medium   | 101    | 126         | 137    | 63     | 74         | 71      |

|             | High     | 173    | 230         | 226    | 97     | 113        | 110     |

|             | Low      | 64     | 81          | 92     | 44     | 51         | 49      |

| Saber [14]  | Medium   | 116    | 143         | 154    | 73     | 85         | 82      |

|             | High     | 188    | 222         | 244    | 107    | 122        | 120     |

|             | Low      | 113    | 150         | 176    | 26     | 38         | 29      |

| Kyber [27]  | Medium   | 185    | 238         | 268    | 41     | 53         | 40      |

|             | High     | 301    | 341         | 382    | 49     | 66         | 51      |

|             | Low      | 1237   | 1382        | 1383   | -      | -          | -       |

| Frodo [29]  | Medium   | 2654   | 2819        | 2509   | -      | -          | -       |

|             | High     | 4225   | 4238        | 4465   | -      | -          | -       |

|             | Low      | 89     | 83          | 93     | 48     | 37         | 47      |

| Smaug [35]  | Medium   | 157    | 148         | 158    | 73     | 59         | 74      |

|             | High     | 251    | 251         | 267    | 127    | 115        | 128     |

|             | Low      | 339    | 110         | 164    | 18     | 15         | 12      |

| NTRU+ [69]  | Medium   | 335    | 154         | 233    | 16     | 18         | 16      |

|             | High     | 358    | 180         | 277    | 14     | 20         | 18      |

|             | Low      | 89     | 80          | 78     | -      | -          | -       |

| Tiger [90]  | Medium   | 104    | 122         | 127    | -      | -          | -       |

|             | High     | 123    | 162         | 176    | -      | -          | -       |

a fair comparison, we have also included implementation results of two versions of Kyber [67] and Frodo [28] (i) Kyber-Speed & Frodo-Speed: optimized to achieve speed, and (ii) Kyber-Stack & Frodo-Stack: optimized to reduce stack memory usage.