# Scabbard: a suite of efficient learning with rounding key-encapsulation mechanisms

Jose Maria Bermudo Mera, Angshuman Karmakar, Suparna Kundu, Ingrid Verbauwhede

imec-COSIC, KU Leuven

Kasteelpark Arenberg 10, Bus 2452, B-3001 Leuven-Heverlee, Belgium {firstname.lastname}@esat.kuleuven.be

**Abstract.** In this paper, we introduce Scabbard, a suite of post-quantum keyencapsulation mechanisms. Our suite contains three different schemes Florete, Espada, and Sable based on the hardness of module- or ring-learning with rounding problem. In this work, we first show how the latest advancements on lattice-based cryptography can be utilized to create new better schemes and even improve the state-of-the-art on post-quantum cryptography.

We put particular focus on designing schemes that can optimally exploit the parallelism offered by certain hardware platforms and are also suitable for resource constrained devices. We show that this can be achieved without compromising the security of the schemes or penalizing their performance on other platforms.

To substantiate our claims, we provide optimized implementations of our three new schemes on a wide range of platforms including general-purpose Intel processors using both portable C and vectorized instructions, embedded platforms such as Cortex-M4 microcontrollers, and hardware platforms such as FPGAs. We show that on each platform, our schemes can outperform the state-of-the-art in speed, memory footprint, or area requirements.

**Keywords:** Post-quantum cryptography  $\cdot$  Learning with rounding  $\cdot$  Key-encapsulation mechanism  $\cdot$  Lattice-based cryptography  $\cdot$  Hardware implementations  $\cdot$  FPGA  $\cdot$  Cortex-M4  $\cdot$  AVX2

## 1 Introduction

Lattice-based hard problems started to gain traction in cryptography with the introduction of Regev's learning with errors (LWE) [Reg04] and Lyubashevsky et al.'s [LPR10] ringlearning with errors (RLWE) as an alternative to integer factorization and elliptic-curve based cryptosystems. However, the launch of the National Institute of Standards and Technology's (NIST) post-quantum standardization program [NIS17] undeniably imparted a fresh impetus to the development of lattice-based cryptography. The majority of the 80 initial submissions in this program were based on lattices. During the first phase of the NIST competition designers incorporated many fresh ideas into the design of latticebased cryptography, e.g., the Falcon signature scheme [FHK<sup>+</sup>18] was designed based on Gentry, Peikert and Vaikuntanathan's framework [GPV07] for signatures instead of the more traditional Fiat-Shamir (with abort) [FS87, Lyu09] framework, Kyber [BDK<sup>+</sup>17], Saber [DKRV19], Dilithium [DKL<sup>+</sup>18] used module-lattices instead of more traditional standard or ideal lattices, Titanium [SSZ19] used the middle-product LWE [RSSS17] problem to construct a key-encapsulation mechanism (KEM) instead of LWE or RLWE, etc. During the latter phases, the cryptographic community is witnessing a substantial effort to improve the designs and implementations [KRS18, HOKG18, KBMSRV18, BUC19], come out with new physical attacks [ADP18, BP18, PPM17], and find better concrete security estimates [APS15, DSDGR20]. Such efforts have enriched the knowledge of lattice-based cryptography to an unprecedented level.

The primary motivation of our work is to show that carefully crafted decisions motivated by innovations in the lattice-based cryptography during last couple of years can lead to very efficient designs of cryptosystems. We want to show that due to changes at design level it is possible to instantiate our schemes by using off the shelf hardware and software implementations with small adaptations only. We also show that it is possible to improve the design of existing schemes using these advancements. Finally, we want to design KEMs with a particular focus on practicality. Our schemes should be efficient on a wide range of hardware and software platforms. To bolster confidence in our schemes we refrain from assuming aggressive assumptions in our design decisions which have been shown to be vulnerable to various attacks during past couple of years. We only use design elements which have stood the test of time by going through rigorous security evaluations during the lifetime of the NIST's standardization effort and, thus, elicit high confidence. Furthermore, we take into account the state-of-the-art cryptanalysis and security estimation techniques while proposing concrete instantiations of our designs. We conclude this section by briefly summarizing our contributions as below.

- 1. We propose Scabbard, a suite of new lattice-based KEMs. Our first scheme, named Florete, is a ring-learning with rounding (RLWR) based KEM. We used one of the third round finalists of NIST's program Saber's hardware and software implementations with some modifications for an efficient implementation of Florete. Our results show that Florete is one of the fastest KEMs when compared to other finalist KEMs in the NIST's post-quantum standardization procedure.

- 2. The introduction of module-lattices [LS15] opened up a whole spectrum of new lattices to designers who were earlier left with only standard or ring-lattices. Although, there exist module-lattice based schemes such as Kyber [BDK<sup>+</sup>17] and Saber [DKSRV18], it is beneficial to explore other constructions. Here, we propose the first of its kind module-learning with rounding (MLWR) with small degree polynomials named Espada, the second KEM in our suite. Espada has been designed to exploit parallelism on hardware platforms and achieves the lowest memory footprint among all KEM finalist in the NIST's standardization process on software platforms.

- 3. The errors in learning with rounding (LWR) based schemes are generated by rounding elements of one number field to another. Since these errors influence the security of the KEM, it is important to estimate them properly. In this work, we properly formalize the distribution of such errors. We combine this with state-of-the-art cryptanalytic methods to propose improved parameters for Saber. We also suggest a new design choice for Saber. Being an MLWR based scheme, Saber is very flexible and scalable in terms of security and resource utilization. We show that incorporating our design choices further boosts these characteristics. We also show that using our parameters it is possible to improve the hardware designs in the state-of-the-art and reduce the key-sizes, and hence the required bandwidth of Saber. We name this modified Saber as Sable and include it as the third KEM in our suite.

- 4. We provide efficient software implementations optimized for general-purpose Intel processors and Cortex-M4 micro-controllers for all our schemes, and propose hardware architectures for accelerate them on field-programmable gate arrays. We compare our implementations with the state-of-the-art to demonstrate the efficiency of our schemes. All our implementations strictly avoid branching on secret data and run in constant-time. All our sources are publicly available<sup>1</sup>.

<sup>1</sup>https://github.com/josebmera/scabbard

## 2 Preliminaries

We denote the set of integers  $\{0, \ldots, q-1\}$  as  $\mathbb{Z}_q$ . We refer to the quotient ring  $\mathbb{Z}_q[x]/(1+x^n)$ by  $\mathscr{R}_q^n$  unless otherwise stated. In this work, the moduli p and q are power-of-two integers (p < q). We denote the ring of  $(l \times m)$ -matrices over any ring R as  $R^{l \times m}$  and the ring of *l*-length vectors over any ring R as  $R^l$ . Polynomials are denoted by lower case alphabets, vectors are denoted by bold lower case alphabets, and matrices are denoted by bold upper case alphabets. If  $a \in \mathscr{R}_q^n$ , then the scaling down operation  $\lfloor \cdot \rceil_p : \mathscr{R}_q^n \to \mathscr{R}_p^n$  is defined by applying the rounding operator  $\lfloor \frac{p}{q}(\cdot) \rceil$  to each coefficient of a and is extended to vectors by applying it to each element. We denote the uniform distribution as  $\mathscr{U}$ . The centered binomial distribution (CBD) is denoted by  $\beta_{\eta}$ , where the standard deviation is  $\sqrt{\eta/2}$ . Sampling according to  $\beta_{\eta}$  is realized by calculating  $\sum_{i=0}^{\eta-1} (b_i - b'_i)$ , where  $b_i$  and  $b'_i$  are pseudo-random bits. Random sampling from any set S according to a distribution  $\chi$ is denoted by  $\leftarrow \chi(S)$  and  $\cdot$  represents the matrix-vector multiplication, vector-vector multiplication or polynomial multiplication depending on the context. The bits(x, i, j)operator is a selection function that takes as input positive integers x, i, j with  $i \ge j$  and outputs j consecutive bits of the positive integer x, ending at the *i*-th index, where the least significant bit (LSB) is the 1st index. It is extended to polynomials, vectors and matrices by applying it coefficient-wise.

#### 2.1 Learning with errors and its variants

The learning with rounding (LWR) by Banerjee *et al.* [BPR12] is a variant of the well known learning with errors (LWE) problem introduced by Oded Regev [Reg04]. An LWE sample is of the form  $(\mathbf{A}, \mathbf{b} = \mathbf{A} \cdot \mathbf{s} + \mathbf{e}) \in \mathbb{Z}_q^{m \times n} \times \mathbb{Z}_q^m$  whereas an LWR sample has the form  $(\mathbf{A}, \mathbf{b} = \lfloor \frac{p}{q} \mathbf{A} \cdot \mathbf{s} \rceil = \lfloor \mathbf{A} \cdot \mathbf{s} \rceil_p) \in \mathbb{Z}_q^{m \times n} \times \mathbb{Z}_p^m$ . Here, the error *e* is generated inherently because of the scaling from  $\mathbb{Z}_q$  to  $\mathbb{Z}_p$ , where p < q. The decisional version of LWR problem states that it is hard to distinguish between the LWR samples and  $(\mathbf{A}, \mathbf{u}) \in \mathbb{Z}_q^{m \times n} \times \mathbb{Z}_p^m$ , where  $\mathbf{s}$  is sampled from  $\chi(\mathbb{Z}_q^n)$  for a specific distribution  $\chi$ ,  $\mathbf{A}$  and  $\mathbf{u}$  are sampled uniformly from  $\mathbb{Z}_q^{m \times n}$  and  $\mathbb{Z}_q^m$  respectively.

Similar to the Ring-LWE problem introduced by Lyubashevsky *et al.* [LPR10], the decisional version of Ring-LWR problem states that it is hard to distinguish between the samples of the form  $(a, b = \lfloor \frac{p}{q}a \cdot s \rceil) \in \mathscr{R}_q^n \times \mathscr{R}_p^n$  from  $(a, u) \in \mathscr{R}_q^n \times \mathscr{R}_q^n$ , where *s* is sampled from  $\chi(\mathscr{R}_q^n)$  for a specific distribution  $\chi$ , *a* and *u* are sampled uniformly from  $\mathscr{R}_q^n$ .

Modules lattices [LS15] were introduced as a trade-off between standard and ideal lattices in terms of efficiency and security. The decisional version of Module-LWR problem states that it is hard to distinguish between the samples of the form  $(\mathbf{A}, \mathbf{b} = \lfloor \frac{p}{q} \mathbf{A} \cdot \mathbf{s} \rceil) \in (\mathscr{R}_q^n)^{l \times l} \times (\mathscr{R}_p^n)^l$  from  $(\mathbf{A}, \mathbf{u}) \in (\mathscr{R}_q^n)^{l \times l} \times (\mathscr{R}_p^n)^l$ , where *s* is sampled from  $\chi((\mathscr{R}_q^n)^l)$  according to the specific distribution  $\chi$ , **A** and **u** are sampled uniformly from  $(\mathscr{R}_q^n)^{l \times l}$  and  $(\mathscr{R}_q^n)^l$  respectively.

The rank of the underlying matrices in these problems is n for LWR and RLWR and  $l \times n$  for MLWR with very high probability. In the absence of efficient attacks that exploit the underlying algebraic structure to their advantage and when all other parameters such as q, p and  $\chi$  are kept the same, the security of all cryptosystems based on these lattices is considered the same if the rank of their underlying matrices is the same. The structure of Module-LWR is more generic as we can convert it to Ring-LWR by making l = 1 and n = n, and to standard LWR by setting l = n and n = 1. For the rest of this paper, we considered the structure of the Module-LWR problem as a generalized LWR problem.

#### 2.2 LWR key-exchange (KEX) protocol

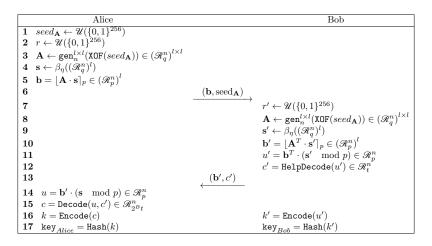

A generalized LWR based key-exchange (KEX) is shown in Protocol. 1. To accomplish this, we need another power-of-two modulus t such that t . Here, the function**gen**generates the public pseudo-random matrix**A**with the help of an extendable-outputfunction**XOF**and a 256-bit random**seed**. Unlike the classic Diffie-Hellman [DH76] KEX,LWR or in general LWE based schemes may not end up with same keys. This is due to hefact that the difference between the final polynomials Alice (<math>u) and and Bob (u') are not negligible. Hence we need an error correction scheme [Pei14, Din12] described in Sec. 2.4. A KEX is called IND-RND secure if the advantage of any adversary  $\mathscr{A}$  to distinguish the key  $k \in K$  (if K is the key space) generated by the KEX from a uniformly random chosen key  $k' \in K$  is negligible. It can be proven that the generalized LWR based KEX as shown in Protocol 1 is IND-RND secure if  $q/p \leq p/(2^B t)$ . This proof closely follows the security proof of Saber [DKSRV18].

Protocol 1: A generalized key-exchange scheme based on LWR

**Theorem 1.** LWR based KEX is IND-RND secure if  $q/p \le p/(2^B t)$ .

*Proof.* See Appendix A.

## 2.3 CCA secure LWR based KEM

The LWR based KEX is a noisy Diffie-Hellman key-exchange [DH76] and can be transformed to an indistinguishable against chosen plaintext attack (IND-CPA) secure public-key encryption (PKE), analogous to the transformation from a Diffie-Hellman key-exchange to the IND-CPA secure ElGamal PKE scheme. In the PKE, the message is added or XORed with each coefficient of the key k' of Bob in the KEX. The correctness of the PKE scheme also depends on the equality of the keys k and k' used in the KEX scheme. LWR based KEX and LWR based PKE are equivalent in terms of security and correctness. It is very simple to show that LWR based PKE scheme is IND-CPA secure if the underlying KEX is IND-RND secure.

Jiang *et al.* [JZC<sup>+</sup>17] provided a version of the Fujisaki-Okamoto transformation [FO99] to convert an IND-CPA secure LWR based PKE to an indistinguishable against chosen chiphertext attack (IND-CCA) secure key-encapsulation mechanism (KEM), when the underlying PKE scheme is not perfectly correct. The authors also proved that if the underlying PKE scheme is  $(1 - \delta)$  correct, then the KEM based on it will be S post-quantum secure where  $\delta \leq 2^{-S}$ .

Following Jian *et al.*'s construction, we provide generic algorithms for IND-CCA secure LWR based KEM (KeyGen, Encaps, Decaps) in Alg. 1, 2, and 3. For example, if we set n = 256, l = 3,  $q = 2^{13}$ ,  $p = 2^{10}$ ,  $t = 2^3$ ,  $\eta = 4$ , B = 1 we will get the Saber KEM.

In these algorithms, H and  $\mathscr{G}$  are hash functions.  $\mathbf{h}_1$ ,  $h_2$ , and  $h_3$  are constant polynomials with each coefficient set to  $2^{(\epsilon_q - \epsilon_p - 1)}$ ,  $(2^{(\epsilon_q - \epsilon_p - 1)} + 2^{(\epsilon_p - B - 1)} - 2^{(\epsilon_p - \epsilon_t - 1)})$ , and  $2^{(\epsilon_q - \epsilon_p - 1)}$  respectively. Here,  $\epsilon_q = \log_2 q$ , i.e.,  $q = 2^{\epsilon_q}$ , similarly  $p = 2^{\epsilon_p}$  and  $p = 2^{\epsilon_t}$ . These are used to calculate the rounding operators  $\lfloor \cdot \rfloor_p$  and  $\lfloor \cdot \rfloor_t$ . In KeyGen Alg. 1  $H(\mathbf{pk})$ is stored in the public key and the Decaps Alg. 3 returns a random value if it fails. These are the extra parts of this FO-transformation for achieving CCA security.

```

Algorithm 1: LWR.KEM.KeyGeneration

Data: nil

Result: pk = (seed_A, b), sk =

(\mathbf{s}, H(\mathbf{pk}), r)

1 seed<sub>A</sub> \leftarrow \mathscr{U}(\{0,1\}^{256})

\mathbf{2} \ r \leftarrow \mathscr{U}(\{0,1\}^{256})

3 \mathbf{A} \leftarrow \operatorname{gen}_{n}^{l \times l}(\operatorname{XOF}(seed_{\mathbf{A}})) \in (\mathscr{R}_{q}^{n})^{l \times l}

4 \mathbf{s} \leftarrow \beta_{\eta}((\mathscr{R}^n_q)^l)

5 \mathbf{b} = \mathtt{bits}(\mathbf{A} \cdot \mathbf{s} + \mathbf{h_1}, \epsilon_q, \epsilon_p) \in (\mathscr{R}_p^n)^l

//Rounding

6 pk \leftarrow (seed_{\mathbf{A}}, \mathbf{b}) \ r \leftarrow_{\$} \{0, 1\}^{256}

7 sk \leftarrow (s, H(pk), r)

s return

\mathtt{pk} = (seed_{\mathbf{A}}, \mathbf{b}), \mathtt{sk} = (\mathbf{s}, H(\mathtt{pk}), r)

Algorithm 2: LWR.KEM.Encapsulation

Data: pk = (seed_A, b)

Result: cipher_txt =

(c^\prime,b^\prime), \texttt{key} = K

1 m' \leftarrow_{\$} \{0,1\}^{256}

2 m = \operatorname{arrange}_m \operatorname{sg}(m')

3 (K', r') \leftarrow \mathscr{G}(m||H(\mathtt{pk}))

4 r' \leftarrow \mathscr{U}(\{0,1\}^{256})

5 \mathbf{A} \leftarrow \operatorname{gen}_{n}^{l \times l}(\operatorname{XOF}(seed_{\mathbf{A}})) \in (\mathscr{R}_{q}^{n})^{l \times l}

6 \mathbf{s}' \leftarrow \beta_{\eta}((\mathscr{R}^n_q)^l)

7 \mathbf{b}' = \mathtt{bits}(\mathbf{A}^T \cdot \mathbf{s}' + \mathbf{h_1}, \epsilon_q, \epsilon_p)

//Rounding

\mathbf{s} \ u' = \mathbf{b}^T \cdot (\mathbf{s}' \mod p) \in \mathscr{R}_p^n

9 c' = bits((u'+h_3-2^{\epsilon_p-\vec{B}}m),\epsilon_p,(\epsilon_t+m_1))

B)) \in \mathscr{R}^{n}_{2^{B}t} \ // \mathrm{HelpDecode}

10 K \leftarrow H(K', H(c'))

11 return

\texttt{cipher\_txt} = (c', b'), \texttt{key} = K

```

Algorithm 3: LWR.KEM.Decaps **Data:**  $pk = (seed_A, b), sk =$  $(\mathbf{s}, H(\mathbf{pk}), r), \mathtt{cipher\_txt} =$  $(c', \mathbf{b}')$ **Result:** key = K1  $u = \mathbf{b}' \cdot (\mathbf{s} \mod p) \in \mathscr{R}_p^n$ 2  $m'_1 = bits((u+h_2 2^{\epsilon_p - \epsilon_t - B}m$ ,  $\epsilon_p, B$ )  $\in \mathscr{R}_{2^B}^n$  //Decode  $m_1 = \text{original} msg(m'_1)$ 4  $m_2 = \texttt{arrange}_msg(m_1)$ 5  $(K'_1, r'_1) \leftarrow \mathscr{G}(m_2 || H(\mathrm{pk}))$ 6  $\mathbf{A} \leftarrow \operatorname{gen}_{n}^{l \times l}(\operatorname{XOF}(seed_{\mathbf{A}})) \in (\mathscr{R}_{a}^{n})^{l \times l}$ 7  $\mathbf{s_1}' \leftarrow \beta_\eta((\mathscr{R}^n_q)^l)$  $\mathbf{s} \; \mathbf{b_1}' = \mathtt{bits}(\tilde{\mathbf{A}}^T \cdot \mathbf{s_1}' + \mathbf{h_1}, \epsilon_q, \epsilon_p)$ //Rounding 9  $u'_1 = \mathbf{b}^T \cdot (\mathbf{s_1}' \mod p) \in \mathscr{R}_p^n$ 10  $c'_1 = bits((u'_1 + h_3 2^{\epsilon_p - B}m), \epsilon_p, (\epsilon_t + B)) \in \mathcal{R}_{2^B t}^n$ //HelpDecode 11 if  $c' = c'_1$  then return  $K = H(K'_1, H(c'))$ 1213 else return K = H(r, H(c'))14

#### 2.4 Error correction mechanism

The error correction mechanism contains three functions Encode, Decode, HelpDecode. Here, the target is to establish the following relation. Let, u and u' be the polynomials computed by Alice and Bob respectively and  $u_i$ ,  $u'_i$  be the *i*-th coefficient of the polynomial u and u'.

If  $|u_i - u'_i| < \epsilon$ , where  $\epsilon$  is the error tolerance, then  $\texttt{Encode}(\texttt{Decode}(u_i, \texttt{HelpDecode}(u'_i))) = \texttt{Encode}(u'_i)$  with high probability. If we take  $u'_i = x$  and  $u_i = y$ , then the functions Encode, HelpDecode and Decode are defined by Encode(x) = "first B bits of x",  $\texttt{HelpDecode}(x) = "\texttt{next } \epsilon_t$  bits of x" and  $\texttt{Decode}(y, \texttt{HelpDecode}(x)) = y - \texttt{HelpDecode}(x) \frac{q}{2^{B+\epsilon_t}}$ . These functions can be extended to polynomial by applying them coefficient-wise. It can

be shown that if the absolute value of error tolerance is bounded by  $\frac{q}{2^{B+1}} - \frac{q}{2^{B+\epsilon_t+1}}$  then the above requirement is satisfied.

**Theorem 2.** If x = y + e and  $|e| \le \frac{q}{2^{B+1}} - \frac{q}{2^{B+\epsilon_{t+1}}}$ , then

Encode(x) = Encode(Decode(y, HelpDecode(x))).

*Proof.* See Appendix B.

#### 2.5 Polynomial multiplication

There are two efficient algorithms for multiplying two polynomials  $a, b \in \mathscr{R}_q^n$ , the number theoretic transform (NTT) [Pol71] which runs in  $O(n \log n)$  and the Toom-Cook [Too63, Coo66, KO62] based polynomial multiplication that runs in  $O(n^{1+\epsilon}), 0 < \epsilon < 1$ . While the NTT is faster, it forces few constraints on the degree of the polynomial n and modulus q. Many RLWE and Module-LWE schemes [BDK<sup>+</sup>17, ADPS16, DKL<sup>+</sup>18] use this polynomial multiplication.

We will only discuss Toom-Cook multiplication or specifically Toom-Cook k-way here since it is the most relevant to our work. Given  $a, b \in \mathscr{R}_q^n$  a pre-processing stage, evaluation, is applied to create a vector of length 2k - 1 from each of a and b, where each element in the vector is a polynomial of length n/k. Each element from each vector can be further split into smaller polynomials by applying Toom-Cook k-way evaluation recursively until the polynomials are small enough to be multiplied with the corresponding polynomial in the other vector by the quadratic complexity schoolbook multiplication algorithm. After the multiplication stage, the Toom-Cook k-way interpolation is applied recursively on the results to get the resulting polynomial  $c = a \cdot b$ . The Toom-Cook 3-way and Toom-Cook 4-way algorithms are described in Alg. 4 and 5 in Appendix G. For more details on Toom-Cook multiplication we refer the interested reader to [Ber01, MKV20].

## 3 Our suite of LWR based KEMs

This section describes our Scabbard KEM suite. All of our schemes follow the generic KEM=(KeyGen, Encaps, Decaps) constructions as shown in Alg. 1, 2, and 3 respectively. Only the ring/module parameters (n, l), moduli  $(\epsilon_q, \epsilon_p, \epsilon_t)$ , encoding parameter (B), CBD parameter  $(\eta)$  and polynomial multiplication change in each scheme. Hence, in the description of our schemes we will only discuss these parameters that are unique to each scheme and their implications. We discuss in detail our design rationale, implementation strategies, challenges and our approaches to overcome them. We first discuss the shape of rounding-errors of LWR based cryptosystems which is very crucial to our designs.

#### 3.1 Rounding error : discrete vs. continuous uniform distribution

As we have discussed before, the errors in LWR based cryptosystems are generated inherently. A series of recent LWR based cryptosystems such as (Round2 [BBG<sup>+</sup>17], Saber [DKRV19], Lizard [CKLS18]) considered this error as continuous uniform in the interval (-q/2p, q/2p]. The following Theorem 3 shows that this error distribution is discretely uniform rather than continuous uniform as assumed earlier.

Consider LWR samples of the form  $(\mathbf{A}, \mathbf{b} = \lfloor \mathbf{A}.\mathbf{s} \rceil_p) \in (\mathscr{R}_q^n)^{l \times l} \times (\mathscr{R}_p^n)^l$ , with  $n \ge 1$ and  $q > p \ge 2$ . We can write  $\mathbf{b} = (b_1, b_2, \dots, b_l)$ , where  $b_i = (b_i^j)$ .

**Theorem 3.** Each coefficient of every polynomial of the rounding error vector follows a discrete uniform distribution over the set  $\{-q/2p, \ldots, q/2p - 1\}$ .

*Proof.* Let us consider the *j*-th coefficient of *i*-th polynomial of rounding error is *e* and  $bits(b_i^j, \epsilon_{q-p}, \epsilon_{q-p}) = \lambda$ . Then  $e = b_i^j - \lfloor (q/p) \lfloor b_i^j \rceil_p \rceil = \lfloor (q/p)f \rceil$ ,

$$\text{where } f = \begin{cases} -1 + \frac{1}{2} & \text{if } \lambda = \frac{q}{2p} \\ -1 + \frac{1}{2} + \frac{1}{2^{(\epsilon_{q}-p)}} & \text{if } \lambda = \frac{q}{2p} + 1 \\ \vdots \\ -1 + \frac{1}{2} + \dots + \frac{1}{2^{(\epsilon_{q}-p)}} & \text{if } \lambda = \frac{q}{2p} + 1 \\ 0 & \text{if } \lambda = 0 \\ \frac{1}{2^{(\epsilon_{q}-p)}} & \text{if } \lambda = 1 \\ \frac{1}{2^{(\epsilon_{q}-p)-1)}} & \text{if } \lambda = 1 \\ \frac{1}{2^{(\epsilon_{q}-p)-1)}} & \text{if } \lambda = 2 \\ \frac{1}{2^{(\epsilon_{q}-p)-1)}} + \frac{1}{2^{(\epsilon_{q}-p)}} & \text{if } \lambda = 3 \\ \vdots \\ \frac{1}{2^{2}} + \dots + \frac{1}{2^{(\epsilon_{q}-p)}} & \text{if } \lambda = \frac{q}{2p} - 1 \end{cases} \text{ So, } e = \begin{cases} -\frac{q}{2p} & \text{if } \lambda = \frac{q}{2p} \\ -\frac{q}{2p} + 1 & \text{if } \lambda = \frac{q}{2p} + 1 \\ 0 & \text{if } \lambda = \frac{q}{2p} - 1 \\ 0 & \text{if } \lambda = 0 \\ 1 & \text{if } \lambda = 1 \\ 2 & \text{if } \lambda = 2 \\ 3 & \text{if } \lambda = 3 \\ \vdots \\ \frac{q}{2p} - 1 & \text{if } \lambda = \frac{q}{2p} - 1 \end{cases}$$

As  $\lambda = \text{bits}(b_i^j, \epsilon_{q-p}, \epsilon_{q-p})$ , then  $\Pr[\lambda = \lambda'] = 1/2^{(\epsilon_{q-p})} = p/q, \forall \lambda' = \{0, 1, \dots, (\frac{q}{p} - 1)\}$ . Therefore,  $\Pr[e = e'] = p/q, \forall e' = \{-q/2p, -q/2p + 1, \dots, q/2p - 1\}$ . Hence, *e* follows a discrete uniform distribution over the set  $\{-q/2p, -q/2p + 1, \dots, q/2p - 1\}$   $\square$

While evaluating the security and failure probability of any LWE based cryptosystem, the variance of the error plays a very crucial role. The variance of the continuous uniform distribution and discrete uniform distribution are  $\frac{q^2}{12p^2}$  and  $\frac{q^2-p^2}{12p^2}$  respectively. As we can see  $\frac{q^2-p^2}{12p^2} < \frac{q^2}{12p^2}$ , considering the rounding error as continuous uniform overestimates the error distribution and consequently the concrete security estimation. Security of lattice-based cryptosystems is proportional to the ratio of standard deviation of error and moduli. Hence, to maintain security we have to decrease the moduli to compensate for the lower standard deviation of error. The parameter calculation of lattice-based cryptography is an optimization problem where the modulus, rank of the lattice, and standard deviation are the control variable. Whereas security and failure probability are the objective function. The standard procedure [ADPS16, BDK<sup>+</sup>17] to solve this problem is to exhaustively search over a wide range of control variables and choosing options which best satisfy the requirements. We have followed the same procedure to find parameters of our schemes. We have considered the above observation during the concrete security estimation of our cryptographic schemes in Sec. 4.1.

#### 3.2 Florete: Ring-LWR based KEM

Our primary focus while designing Florete was to maximally reuse the already very efficient hardware architectures and software modules [KRS18, KBMSRV18, RB20, MKV20] that have been developed for Saber for a more efficient KEM without compromising the security.

Since the introduction of binomial distributions in lattice-based cryptography, the polynomial multiplication has become the most computationally expensive operation in lattice-based cryptography. Although, in some platforms such as Cortex-M4 the pseudo-random number generation can take upto 50% of the total execution time [KRS18]. Due to our choice of moduli we are unable to use asymptotically faster number theoretic transform (NTT) based polynomial multiplications without using a larger NTT friendly prime (discussed in Appendix C). Hence, we resort to generic Toom-Cook polynomial multiplications. Below we describe the fundamental building blocks of Florete.

**Polynomial multiplication**: For our efficient implementation of Florete, we fix our quotient ring  $\mathscr{R}_q^n$  as  $\mathbb{Z}_q[x]/(x^{768} - x^{384} + 1)$ . Now, while multiplying two polynomials

$a, b \in \mathscr{R}_q^n$  during KeyGen, Encaps, and Decaps we first apply a Toom-Cook 3-way evaluation on a and b. This splits both of them into 2 \* 3 - 1 = 5 polynomials of length 256 each. To multiply these 256 length polynomials we use the efficient hardware and software routines to perform  $256 \times 256$  polynomial multiplications for Saber. Further we can join these results using Toom-Cook 3-way interpolation to get the result  $c = a \times b \in \mathscr{R}_q^n$  after reduction by  $(x^{768} - x^{384} + 1)$ . Since the computational cost for Toom-cook 3-way evaluation and interpolation are small (as shown in Alg. 4 in Appendix. G) the time to perform 5 individual  $256 \times 256$  polynomial multiplications is very close to the time to perform one  $768 \times 768$  polynomial multiplication using our strategy. Further, as we are working in RLWR, our underlying ideal lattice can be represented by a single public polynomial of length 768 whereas for Saber the underlying module-lattice needs 9 polynomials of length 256 each. A comparison of the required randomness and the number of  $256 \times 256$ polynomial multiplications to generate the LWR samples in Florete and in Saber is shown in Table. 1. We can see from this table that Florete gains in efficiency compared to Saber in both number of multiplications and pseudo-random number generation.

| Name    | Pseudo-random  | $256\times256$ multiplications |        |        |  |  |  |  |

|---------|----------------|--------------------------------|--------|--------|--|--|--|--|

| Traine  | number (Bytes) | KeyGen                         | Encaps | Decaps |  |  |  |  |

| Florete | 1152           | 5                              | 10     | 15     |  |  |  |  |

| Saber   | 4512           | 9                              | 12     | 15     |  |  |  |  |

Table 1: Required pseudo-random bytes for generating public matrix (A) and secret vector (s), and number of  $256 \times 256$  multiplications in Saber and Florete.

However, there is a small caveat in this arrangement. We want the coefficients of our polynomials to fit within 16 bits for efficient multiplication in vector processors, small microcontrollers, or FPGAs. While applying Toom-Cook interpolations we often need to divide the field elements by r, where  $r = 2^d \cdot m$  with gcd(m, 2) = 1. Since we are working in the power-of-two finite fields there exists no inverse of  $r = 2^d \cdot m$  where d > 1. To overcome this while dividing by r, first multiply the number by inverse of m in the field followed by right shift of d bits. Thus, if we limit ourselves to 16-bit word length then it means our  $\epsilon_q$  can not be more than 16 - d bits long for correct multiplication in  $\mathscr{R}_n^q$ . The maximum value of d in Toom-Cook 3-way and Toom-Cook 4-way interpolation is d = 1 and d = 3 respectively. Hence, to combine these two algorithms according to our strategy our  $\epsilon_q$  cannot be more than 12 bits long. Note that, in Saber's design  $\epsilon_q = 13$ , therefore this combination of multiplications do not work if we use Saber's parameters. Here, we utilize our observation on Sec. 3.1 to reduce the standard deviation of the error and reduction of  $\epsilon_q$  as a compensation to achieve our goal of  $\epsilon_q \leq 12$ . As we can see from Table 2, this reduces the post-quantum security of Florete than Saber by 12 bits but it is still high enough to qualify for NIST security level 3.

**Error correction and encoding**: Schemes like Round5 [BGML<sup>+</sup>18, BBG<sup>+</sup>17], LAC [LLZ<sup>+</sup>18] used error-correcting codes to reduce their failure probabilities of their KEMs. But these schemes open up many avenues of side-channel attacks [GMR20, DTVV19, GJY19, SC19, Son19]. This was one of the biggest reason for them not to qualify to the NIST's post-quantum standardization final round [AASA<sup>+</sup>17]. We used the error correction mechanism shown in Sec. 2.4 which is also used by Saber. In this mechanism, the size of the second rounding modulus t is proportional to the maximum error that can be corrected. As we need a very low failure probability,  $\epsilon_t$  should be large. And as  $\epsilon_t < \epsilon_p < \epsilon_q$  this imposes a limit on  $\epsilon_p$  and  $\epsilon_q$  as well. Here, we are working in ring  $\mathcal{R}_q^n$  with n = 768, with the only 256 bits of secret payload (m'). We can set B = 1and use each coefficient of our polynomial to embed each bit of secret with repetitions as **arrange\_msg**(m') = m' ||m'||m'. To recover the message we can take a majority vote as shown below

$$\texttt{original\_msg}(m_1[b]) = \begin{cases} 0 & \text{if } m_1'[b] + m_1'[b+256] + m_1'[b+512] \le 1 \\ 1 & \text{else} \end{cases}$$

As the error tolerance is increased due to the use of repetition we can reduce  $\epsilon_t$  without increasing the failure probability. This consequently helps to reduce  $\epsilon_p$  and  $\epsilon_q$  further.

Security levels: We have so far described Florete to target a NIST security level 3. Our strategy can be extended to provide a security level 1 version with n = 512 and using Karatsuba [KO62] to split the polynomial into three polynomials of length 256 for the multiplications. A security level 5 version can be provided with n = 1024 and using Toom-Cook 4-way to split the actual polynomial into 7 polynomials of length 256. We leave instantiation of different security levels of Florete as a future work. We provide the full parameter list of Florete in Table 2. Following the works of Alkim *et al.* [ABC19] and Chung *et al.* [CHK<sup>+</sup>20] it is possible to improve the speed of Florete further by using a larger NTT friendly prime. We discuss this in Appendix C.

#### 3.3 Espada: Module-LWR based KEM

The fundamental motivation behind designing our Module-LWR based KEM Espada was to have a scheme that is extremely parallelizable and has a small memory footprint in resource-constrained devices. Overall we also keep the performance on other platforms within the practical limits. As before we aim for  $\geq 128$  bits of post-quantum security.

If we look carefully, cryptosystems based on module-lattices are very suitable for parallel implementation. To recapitulate, in module-lattice based cryptosystems we need multiplications of the form  $\mathbf{A} \cdot \mathbf{s}$  or  $\mathbf{b} \cdot \mathbf{s}$  where  $\mathbf{A} \in (\mathscr{R}^n_q)^{l \times l}$  and  $b, s \in (\mathscr{R}^n_q)^l$ . On a detailed note, these multiplications are basically multiplications of  $a, b \in \mathscr{R}_a^n$  which can be performed in parallel. Unfortunately, due to the large size of n it is very costly in terms of area requirement to have multiple instances of polynomial multipliers. As an example, for Saber, where n = 256, the recent compact implementation by Bermudo Mera et al. [MTK<sup>+</sup>20] first splits each  $256 \times 256$  polynomial multiplication to  $7.64 \times 64$ polynomial multiplications which are then performed in parallel. This implementation avoids the 2-levels of Karatsuba multiplication as  $64 \times 64$  schoolbook multiplication is already very fast on the target hardware platform. The whole  $256 \times 256$  multiplier requires 28 DSP units, which is a more scarce resource than LUTs or FFs on FPGAs, and creating multiple instances of the  $256 \times 256$  would rapidly exhaust it. Another implementation by Roy et al. [RB20] focuses on high-speed implementation but it again requires prohibitively high area for parallel instantiations. Lastly, the implementation by Dang et al. [DFAG19] uses such a high number (256) of DSP units that even a single instance of the multiplier is only suitable for the most powerful FPGAs like the UltraScale+ family by Xilinx.

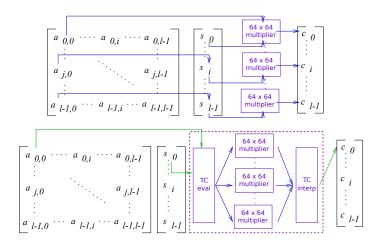

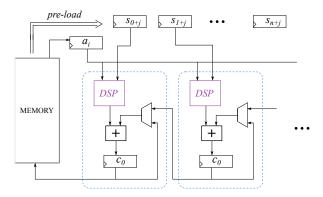

Therefore, if we make n smaller we can easily exploit the parallelism reducing the cost of creating multiple instances of multipliers. Depending on the value n and the implementation philosophy, one can either use a compact multiplier inspired by the small  $64 \times 64$  multipliers in [MTK<sup>+</sup>20] or an approach based on the fast schoolbook multiplier in [RB20]. As n is small both of them will be very fast and will require very low area. In this way the multiple instances of  $n \times n$  polynomial multipliers can perform the multiplications in batch. This is explained in Fig. 1, where we compare this approach to the use of small polynomial multipliers in parallel after applying Toom-Cook to break down a larger multiplication. Furthermore, in implementations of module-lattice based cryptosystems, the memory footprint is proportional to the size of one polynomial thanks to the *just-in-time* matrix generation and other techniques developed in the context of the NIST PQC competition [KBMSRV18, KRS18]. Considering this, we have optimally chosen n in Espada as 64. Keeping n small has another benefit. As the rank of the module-lattices

Figure 1: Comparison of parallel polynomial multiplication in Espada (top) with polynomial multiplication in Saber (bottom). The lines in blue and green denotes parallel and serial execution respectively. The components inside the boxes are implemented on hardware.

are multiples of n and the security is dependent on the rank of underlying matrix, having larger n often overshoots the security target. However, for small n we can have fine-grain control over security.

**Encoding and error-correction**: As our *n* is small and we are still considering a secret message payload of 256 bits, we set B = 4, i.e., we embed 4 secret bits in a single coefficient of the polynomial. However, according to Theorem 2, having a large *B* reduces the ability of the amount of error that can be corrected in our scheme. To compensate this, we have to increase  $\epsilon_t$ . As  $\epsilon_t < \epsilon_p < \epsilon_q$ , this further requires a larger  $\epsilon_p$  and  $\epsilon_q$  to achieve the desired failure probability of  $\leq 2^{-128}$ .

**Polynomial multiplication:** As can be seen in Table 2, our modulus is 15 bits long. Hence, as discussed in Sec. 3.2, in order to limit ourselves within 16 bits of wordlength, we cannot use algorithms such as Toom-Cook 3-way or 4-way multiplications. Hence, for software implementations we use two levels of Karatsuba to split each  $64 \times 64$ polynomial multiplication into 9  $16 \times 16$  polynomial multiplications. Also, in software implementation Toom-cook 4-way algorithm takes almost same time as 2-level karatsuba due to the interpolation and evaluation overhead. For hardware implementations we use a different approach which is described in Sec. 5. Further, as our l = 12 is quite large compared to other module-lattice based schemes, we use the lazy interpolation polynomial multiplication using this technique. We also use the optimized assembly routine from Kannwischer *et al.* [KRS18] for our microcontroller implementation.

**Others:** As we have reduced n, which in turn requires larger l and q for sufficient security and failure probability, we need to generate more pseudo-random numbers. Also we need to perform more  $64 \times 64$  polynomial multiplications compared to Saber. Despite this, as shown in Sec. 4.2 our software implementation is quite fast for both portable C and micro-controller implementation. Similar to Florete, we can instantiate two other variants of Espada satisfying NIST security level 1 and 5 by increasing or decreasing l. Also, it might be possible to create a MLWE based KEM that can be instantiated with n = 64 and NTT friendly parameters using similar strategies to the ones explained here.

#### 3.4 Sable: Alternate Saber

Sable is the third lattice-based KEM in our suite. As discussed in section Sec. 3.1, the Saber design used rounding error as continuous uniform distribution rather than discrete

uniform distribution. Due to a different standard deviation of error, we have to readjust other parameters, i.e.,  $\epsilon_p$ ,  $\epsilon_q$  and  $\eta$  to ensure that there is no significant drop in security. The updated parameters can be found in Table 2. We describe the rationale behind our choices below.

Secret distribution: We sample our secret values from the centered binomial distribution with  $\eta = 1$  that means secret coefficients can be -1, 0, 1 only. This enables very fast multiplication in the platforms where multiplications are costlier than addition and subtraction such as MSP430 microcontrollers as the multiplication instructions can be replaced by additions and subtractions only. A recent hardware implementation has been proposed utilizing the small values of the secret [RB20]. We show in Sec. 5.3 that our parameters can further improve the performance and area of that hardware implementation. Furthermore, due to our choice  $\eta = 1$ , the secret can be stored using only 2-bits per coefficient. This results in a smaller memory requirement for Sable. Please note that here we have refrained from aggressive choices of secret distributions such as fixing the hamming weight of secret polynomials like Round5 [BGML<sup>+</sup>18], using any error correcting code to reduce failure probability like LAC  $[LLZ^{+}18]$  or fixing the weight of the secret vector [BCLvV16]. We have stuck to binomial distribution to prevent the adversary from gaining any additional advantage due to the secret distribution. We discuss security implications in more details in Sec. 4.1. Currently, Saber team has produced another version called uSaber with 2 bits of uniform secret due to its advantage in implementation. This is very similar to our choice if we consider signed-bit representation.

**New design choice:** In Saber, we perform polynomial multiplications with the form of  $a \cdot s$ , where a is random in  $\mathscr{R}_q^n$  or  $\mathscr{R}_p^n$  and s sampled according to the distribution  $\beta_\eta$ . Saber has  $\eta = 5, 4, 3$  for LightSaber, Saber and FireSaber respectively. We realized that it is more beneficial to keep  $\eta$  equal across all variants and varying  $\epsilon_q$  and  $\epsilon_p$  instead of keeping  $\epsilon_q$  and  $\epsilon_p$  same and varying  $\eta$  as done in Saber. Since secrets have a particular distribution, it is easy to exploit this distribution for every efficient implementation. Hence, if  $\eta$  is kept same for different variants, the multiplier can be heavily optimized and used in all variants. Since the distribution of a is random in  $\mathscr{R}_q^n$  or  $\mathscr{R}_p^n$ , it is difficult to exploit the distribution of a for fast multiplication. In this case, the multiplier can be optimized for the maximum value of  $\epsilon_q$  and  $\epsilon_p$  only. This will work fine since  $\epsilon_p$  and  $\epsilon_q$  are power-of-two numbers. The recent implementation [RB20] for fast implementation of Saber exploits the special structure of the secret. However, they had to create additional hardware to support different  $\eta$  values. Since Saber designers stresses on the flexibility of the design, we think our design provides more flexibility than the original design. In addition to the fast polynomial multiplications, keeping a small  $\eta$  equal for all variants is also beneficial in masking. A recent paper on masking Saber  $[BDK^+20]$  mentioned that the binomial sampler requires the most complex algorithms for masking among all the components. It also becomes more expensive for larger  $\eta$ . Indeed easier masking has been cited as the main reason for proposal of uSaber in the Round-3 submission of Saber [BMD+20] and a smaller  $\eta$  offers advantages for masking. We note that Kyber adopted the same design choice in their Round-2 submission  $[ABD^+19]$ .

## 4 Concrete instantiations

#### 4.1 Security estimation

Like for other public-key cryptosystems, the concrete security of lattice-based cryptosystems is evaluated by calculating the time required by the best-known algorithm to solve the underlying computationally hard problem. For lattice-based cryptosystems this accounts to estimating the time to solve the underlying shortest vector problem using the block Korkine-Zolotarev [CN11, SE94] algorithm.

The state state-of-the-art solution which is used by almost all lattice-based schemes is using the *LWE-estimator* framework provided by Albrecht *et al.* [APS15]. Given  $(n, q, \sigma_e,$  secret distribution) where  $\sigma_e$  is the standard deviation of the error of a lattice based cryptosystem, this framework can compute the concrete security by estimating the run-time of all possible methods to solve the underlying hard lattice problem. Kindly note that, this estimator always considers error distribution as Gaussian distribution. Since the proposal of Applebaum *et al.* [ACPS09] to sample the secret from the same distribution as the errors most LWE based cryptosystems use  $\sigma_s = \sigma_e$ . However, in most LWR based cryptosystems [DKRV19, BBG<sup>+</sup>17, CKLS18] due to the rounding errors  $\sigma_s < \sigma_e$ . In this case, determining the concrete security of an LWR based cryptosystem using this framework while considering  $\sigma_e = \sigma_s$  will lead to overestimation of the security of the scheme <sup>2</sup>.

A new toolkit *leaky-LWE-Estimator* by Dachman-Soled *et al.* [DSDGR20] has been published recently to attack and estimate the hardness of the underlying LWE problem with side information. *Leaky-LWE-Estimator* considers  $(n, q, D_e, D_s)$  as input, where  $D_e, D_s$ are error distribution and secret distribution of a lattice-based cryptosystem respectively and outputs the security of that cryptosystem. Moreover, in this estimator, we have the flexibility to consider the error distribution of a cryptosystem as a discrete uniform distribution.

Since, any adversary instead of trying to solve the original LWR instance  $\mathbf{A}, \mathbf{b} = \mathbf{A} \cdot \mathbf{s} + \mathbf{e}_r$  can solve the easier instance  $(\mathbf{A}^{-1}, \mathbf{A}^{-1} \cdot \mathbf{b} = \mathbf{s} + \mathbf{A}^{-1} \cdot \mathbf{e}_r)$ , here  $e_r$  is the inherently generated rounding error. Therefore, to avoid the problem of overestimating the concrete security, we have estimated the security of the scheme using Ducas *et al.*'s framework by considering minimum of  $(n, q, D_e, D_s)$  and  $(n, q, D_s, D_e)$  estimations.

As can be seen in Table 2, we have considered CBD with  $\eta = 1$ . This means our secrets can have values in the set  $\{-1, 0, 1\}$ . Recently, few attacks [GMR20, DTVV19, GJY19, DDGR20] have been proposed on schemes that have considered some aggressive secret distributions mainly to reduce failure probabilities, such as considering fixed hamming weight binomial distribution as secret distribution with an error correcting code (like LAC [LLZ<sup>+</sup>18]) or fixed the number of 1's and -1's of the ternary secret polynomial (like Round5 [BGML<sup>+</sup>18]). Although, Dachman-Soled *et al*. [DDGR20] proved that if the secret has a fixed number of ±1 without knowing the exact amount of 1 and -1 (as in NTRU Prime [BCLvV16]), then the loss of security is negligible. Chen *et al*. [CCLS20] have also studied the some special ternary distributions and their security implications on lattice-based cryptography. To avoid adverse security implications we have refrained from taking any of such aggressive assumptions and used the standard binomial distribution where there is no fixed limit on the numbers of -1, 1, or 0. To the best of our knowledge, there does not exist any attack which can take advantage from binomially distributed secret distribution with  $\eta = 1$ .

#### 4.2 Parameters and performance

We compare parameters of Scabbard with Saber in Table 2. As we can see, for similar security levels, all the variants of Sable improve the key sizes of Saber. Further, if we consider the bandwidth usage of each scheme, i.e., the combined size of public-key and ciphertext we can see that the bandwidth usage of Florete (2048 bytes) is slightly smaller than Saber (2080 bytes) despite being an ideal-lattice based scheme. The bandwidth of Espada (2584 bytes) is expected to be higher than Saber due to larger moduli. However, this increase is less than 25%.

Software performance: We have compiled our portable C implementations and

<sup>&</sup>lt;sup>2</sup>Due to this reason the concrete security of Saber was overestimated in their previous submissions [DKRV19, DKSRV18]. This has been rectified in the round-3 submission [BMD<sup>+</sup>20]

| Scheme Name  | Ring | g/Module | PQ        | Failure     | Mo                 | duli | CBD              | Encoding | Key sizes   | for  |

|--------------|------|----------|-----------|-------------|--------------------|------|------------------|----------|-------------|------|

| Scheme Ivame | Pai  | rameters | Security  | probability | MO                 | uun  | $(\beta_{\eta})$ | Encoung  | KEM (Byt    | es)  |

|              | n:   | 768      |           |             | $\epsilon_q$ :     | 10   |                  |          | Public key: | 896  |

| Florete      |      |          | $2^{157}$ | $2^{-131}$  | $\epsilon_p$ :     | 9    | $\eta = 1$       | B=1      | Secret key: | 1152 |

|              | l:   | 1        |           |             | $\epsilon_t$ :     | 3    | ,                |          | Ciphertext: | 1248 |

|              | n:   | 64       |           |             | $\epsilon_q$ :     | 15   |                  |          | Public key: | 1280 |

| Espada       |      |          | $2^{128}$ | $2^{-167}$  | $\epsilon_p$ :     | 13   | $\eta = 3$       | B=4      | Secret key: | 1728 |

| 1            | l:   | 12       |           |             | $\epsilon_t^P$ :   | 3    | ,                |          | Ciphertext: | 1304 |

|              | n:   | 256      |           |             | $\epsilon_q$ :     | 11   |                  |          | Public key: | 608  |

| LightSable   |      |          | $2^{104}$ | $2^{-139}$  | $\epsilon_p$ :     | 9    | $\eta = 1$       | B=1      | Secret key: | 800  |

| 0            | l:   | 2        |           |             | $\epsilon_t^{P}$ : | 2    | ,                |          | Ciphertext: | 672  |

|              | n:   | 256      |           |             | $\epsilon_q$ :     | 11   |                  |          | Public key: | 896  |

| Sable        |      |          | $2^{169}$ | $2^{-143}$  | $\epsilon_p$ :     | 9    | $\eta = 1$       | B=1      | Secret key: | 1152 |

|              | l:   | 3        |           |             | $\epsilon_t^P$ :   | 4    | ,                |          | Ciphertext: | 1024 |

|              | n:   | 256      |           |             | $\epsilon_q$ :     | 11   |                  |          | Public key: | 1312 |

| FireSable    |      |          | $2^{203}$ | $2^{-208}$  | $\epsilon_p$ :     | 10   | $\eta = 1$       | B=1      | Secret key: | 1632 |

|              | l:   | 4        |           |             | $\epsilon_t^p$ :   | 2    | ,                |          | Ciphertext: | 1376 |

|              | n:   | 256      |           |             | $\epsilon_q$ :     | 13   |                  |          | Public key: | 672  |

| LightSaber   |      |          | $2^{107}$ | $2^{-120}$  | $\epsilon_p^q$ :   | 10   | $\eta = 5$       | B=1      | Secret key: | 992  |

| 0            | l:   | 2        |           |             | $\epsilon_t^P$ :   | 2    | ,                |          | Ciphertext: | 736  |

|              | n:   | 256      |           |             | $\epsilon_q$ :     | 13   |                  |          | Public key: | 992  |

| Saber        |      |          | $2^{172}$ | $2^{-136}$  | $\epsilon_p$ :     | 10   | $\eta = 4$       | B=1      | Secret key: | 1440 |

|              | l:   | 3        |           |             | $\epsilon_t^p$ :   | 3    | ,                |          | Ciphertext: | 1088 |

|              | n:   | 256      |           |             | $\epsilon_q$ :     | 13   |                  |          | Public key: | 1312 |

| FireSaber    |      |          | $2^{236}$ | $2^{-165}$  | $\epsilon_p^q$ :   | 10   | $\eta = 3$       | B=1      | Secret key: | 1760 |

|              | l:   | 4        |           |             | $\epsilon_t$ :     | 5    | , .              |          | Ciphertext: | 1472 |

Jose Maria Bermudo Mera, Angshuman Karmakar, Suparna Kundu, Ingrid Verbauwhedð

Table 2: Comparison of Scabbard suite with Saber

vectorized implementations using advanced vector instructions (AVX2) using GCC 6.5 having optimization flags -03 and -fomit-frame-pointer enabled on an Intel(R) Core(TM) i7-6600 CPU running at 2.60GHz. We also disabled hyperthreading, turbo-boost and multicore support as per standard procedure. For our Cortex-M4 implementations, all performance and memory measurements were taken using the easy to use the framework provided in [KRSS] on an STM32F4DISCOVERY board running at 24 MHz.

As we can observe in Table 3 and 4, Florete has better performance in all software implementations. In the Cortex-M4 platform, it performs better than Saber by 48% and 25%, 14% in KeyGen, Encaps and Decaps respectively. The KeyGen, Encaps algorithms of Florete perform 42%, 11% faster than Kyber respectively. Only the Decaps algorithm is 11% slower in Florete than Kyber. It requires larger memory due to the ring structure. However, it still requires less memory compared to NTRU [CDH<sup>+</sup>19] except Encaps.

Espada has the lowest memory footprint among all KEMs. It requires, 61%, 67%, 69% and 11%, 28%, 33% less memory than Saber and Kyber for KeyGen, Encaps and Decaps respectively. Espada (17856 Bytes) requires almost 4 times more pseudo-random numbers than Saber (4512 Bytes) and almost twice  $64 \times 64$  polynomial multiplications (for Espada 468 and for Saber 252). In software implementations, Keccak algorithm takes more than 50% of the execution time to generate the matrix and secret vector. Despite of all these disadvantages, the running time of this scheme in software is approximately 2.5 times slower than the Saber in the worst case, which we still believe that is suitable for practical scenarios. On the other hand, if one uses faster pseudo-random number generators than Keccak in software such as AES-CTR mode then better performances can be achieved. Kyber uses NTT multiplication which is an in-place algorithm in terms of memory. Despite this, Espada needs less memory than Kyber. Lastly, the performance and memory requirements of Sable are better than Saber in every platform. For a better insight into these results we have provided a breakdown of clockcyles on Cortex-M4 platform in Appendix D.

We have also included a concurrent work by Chung at al. [CHK<sup>+</sup>20] which employs

NTT to perform polynomial multiplication in Saber in the comparison. We have described how this strategy can be applied to Sable in Appendix C.2. Table 8 shows that even our preliminary implementation of NTT-Sable has better efficiency than NTT-Saber using this method. Although using a slower polynomial multiplication routine than NTT-Saber, we can see Florete still has better efficiency than NTT-Saber except Decaps (slower by 14%). We have sketched how Florete can also be implemented using NTT in Appendix C. We firmly believe when employed this method Florete will outperform all the KEMs in all of KeyGen, Encaps, and Decaps.

| Scheme Name  | Security | C (X10 | 00 clock o | cycles) | AVX (X | 1000 clock | cycles) |

|--------------|----------|--------|------------|---------|--------|------------|---------|

| Scheme Ivame | level    | KeyGen | Encaps     | Decaps  | KeyGen | Encaps     | Decaps  |

| Florete      | Medium   | 86     | 147        | 193     | 58     | 87         | 97      |

| Espada       | Medium   | 334    | 354        | 350     | 258    | 273        | 267     |

|              | Low      | 79     | 106        | 116     | 54     | 64         | 58      |

| Sable        | Medium   | 152    | 186        | 207     | 80     | 95         | 89      |

|              | High     | 240    | 285        | 308     | 125    | 143        | 144     |

|              | Low      | 88     | 129        | 120     | 66     | 76         | 73      |

| Saber        | Medium   | 159    | 201        | 215     | 107    | 118        | 112     |

|              | High     | 265    | 315        | 338     | 149    | 173        | 165     |

|              | Low      | 154    | 209        | 250     | 271    | 335        | 310     |

| Kyber        | Medium   | 252    | 324        | 365     | 537    | 594        | 557     |

|              | High     | 400    | 515        | 566     | 874    | 969        | 907     |

| NewHope      | Low      | 136    | 205        | 231     | 76     | 121        | 124     |

| межноре      | High     | 265    | 404        | 448     | 139    | 224        | 233     |

Table 3: Performance comparison in portable C and AVX2 implementation of Scabbard with other lattice-based KEMs.

| Scheme Name                     |        | M4 perfor<br>0 clock cy |        | Corte  | ex-M4 mer<br>(bytes) | nory   |

|---------------------------------|--------|-------------------------|--------|--------|----------------------|--------|

| Selicine Rame                   | KeyGen | Encaps                  | Decaps | KeyGen | Encaps               | Decaps |

| Florete                         | 439    | 814                     | 953    | 18252  | 18420                | 18420  |

| Espada                          | 2343   | 2568                    | 2497   | 2896   | 2120                 | 2000   |

| Sable                           | 745    | 1004                    | 1028   | 6184   | 5992                 | 5496   |

| $\mathrm{Saber}^\dagger$        | 846    | 1098                    | 1112   | 7488   | 6560                 | 6568   |

| NTT-Saber [CHK <sup>+</sup> 20] | 658    | 864                     | 835    | 27440  | 29080                | 30176  |

| Kyber*                          | 763    | 923                     | 862    | 3276   | 2964                 | 2988   |

| NTRUhrss701*                    | 153104 | 377                     | 869    | 27560  | 7400                 | 20552  |

| NTRUhps2048677*                 | 143734 | 821                     | 815    | 28504  | 9036                 | 19728  |

| Frodo*                          | 79325  | 79699                   | 79145  | 26600  | 51976                | 72592  |

Table 4: Comparison Scabbard with NIST finalist KEMs on Cortex-M4 for security level 3 \* Collected from pqm4 [KRSS] <sup>†</sup> Collected from the official website of Saber for high-speed version.

## 5 Hardware acceleration

The design of new cryptographic schemes prioritizes the security first and foremost. Efficiency also plays an important role in the design decisions, but it is usually considered in theoretical terms, i.e., algorithmic complexity, which often leads to software efficiency. The short development cycle of software allows fast prototyping and a better feedback loop between developers and designers. However, as we explained in Sec. 1, one of the motivations of this work is to show that hardware efficiency can also be taken into account as part of the design cycle of cryptographic schemes with a successful outcome.

**HW/SW vs full HW design strategies**: There are two approaches towards hardware acceleration. A HW/SW co-design implements only the most computationally expensive operations on hardware to provide more flexibility and reduce the design cycle at the expense of not achieving the highest performance. A full HW implementation achieves the highest performance but it requires a longer development cycle. The purpose of the hardware implementations is to demonstrate the benefits of our design decisions rather than providing thoroughly optimized processors for the highest performance. Therefore, we choose a HW/SW co-design approach.

If we look at Table 9 in Appendix D, we can observe that the two critical operations in our schemes are polynomial multiplication followed by hashing. As we discussed in Sec. 3 and 4.2, pseudo-random number generation is based on Keccak to make our schemes fairly comparable to the state-of-the-art. At this moment there is a lack of transparency regarding the choice of pseudo-random number generators (PRNG). NIST encourages to use one of the NIST standardized symmetric-key schemes but never specified Keccak. It is quite possible that in the future more efficient constructions may replace the Keccak based PRNG, both in our schemes as well as in NIST finalists. Also, KEMs like Kyber  $[ABD^+21]$  or Saber  $[BMD^+20]$  have proposed alternative constructions in their recent NIST submissions using pseudo-random number generators based on AES-CTR named Kyber90s and Saber90s, respectively. Including a Keccak hardware, e.g., the official implementation [Kec], incurs in the same area overhead for any scheme because the functions used are identical. Hence, it does not provide a scientific added value when it comes to comparing different schemes among them. On the other hand, including a Keccak module in hardware would benefit the overall performance of the schemes in the same way that a full hardware implementation outperforms SW/HW co-design approaches.

Since our design decisions were centered around improving the polynomial multiplication in our KEMs, our goal is to demonstrate the improvements in our cryptographic designs using off the shelf and state-of-the-art implementations of polynomial multiplications in hardware. Future works exploring different hardware architectures exploiting more specific properties of each scheme can come later as it has always happened when designing new schemes. In fact, it is very common in the literature to focus on optimizing the polynomial multiplication exclusively when researching on accelerating lattice-based cryptography [ACC<sup>+</sup>20, CHK<sup>+</sup>20, KRS18, LS19, MKV20, MTK<sup>+</sup>20]. Also there is a lot of precedence of outsourcing the most computationally expensive components to hardware accelerators in elliptic-curve or Rivest-Shamir-Adleman cryptography [GFSV09, LXJL11]. Lastly, with our implementations we also demonstrate that different trade-offs between area and performance in hardware implementations can be achieved by exploring the design space of the cryptographic scheme rather than by exploring different hardware architectures.

**HW/SW interface**: We implement our hardware on a Xilinx Zynq device that integrates FPGA and ARM processors. The communication between them is based on the AXI interface. The commands are transferred in parallel as a single word of 64-bits, that indicates the base address for the memory accesses and the operation performed. The overhead introduced by the commands is negligible since it is only  $0.2\mu s$  per command. The data is transferred in a stream free from addressing information and we use the DMA provided by Xilinx to achieve high performance on bulky data transfers. The data transfer of one polynomial (of 256 coefficients), one vector and one matrix takes  $2.7\mu s$ ,  $4.4\mu s$  and  $14.9\mu s$ , respectively. While this overhead is relevant when compared to the multiplication time in hardware (see Table 6), it can be avoided by having a full hardware implementation. However, as we explained before, our goal is to demonstrate how to achieve efficiency by design rather than providing high performance architectures for given schemes. Also, as we show in Sec. 5.4, our co-processors are effective in accelerating the polynomial arithmetic and set the base around which a full hardware implementation shall be built.

#### 5.1 Florete on hardware

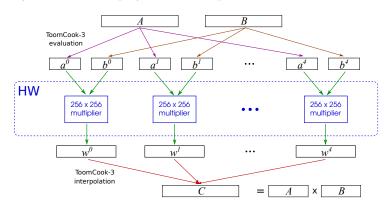

Following a complexity theory analysis, schemes built upon ideal lattices are inherently efficient by design. As we have described in Sec. 3.2, generating an RLWR sample in Florete requires a  $768 \times 768$  polynomial multiplication, that in turn can be decomposed into 5  $256 \times 256$  polynomial multiplications applying Toom-Cook 3-way. This means 45% less multiplications than a module lattice-based scheme offering the same security level, e.g., Saber or Kyber, which require 9  $256 \times 256$  polynomial multiplications for matrix-vector multiplication. However, this comes at the price of a large memory overhead in software. The challenge in hardware is to maintain the benefit in performance over module lattice-based schemes while achieving a comparable area.

The first decision when designing an accelerator for Florete is whether to break down the big  $768 \times 768$  polynomial multiplication into smaller polynomial multiplications or implement a schoolbook algorithm. If we opt for the former, we only need to implement the Toom-Cook 3-way evaluation and interpolation to wrap up the  $256 \times 256$  polynomial multiplier, which can be implemented as the existing architectures in the literature. If we opt for the latter, the resulting hardware will be 3 times slower and 3 times bigger than the state-of-the-art  $256 \times 256$  polynomial multipliers [DFAG19, RB20]. Moreover, since we are following a HW/SW co-design approach rather than an full hardware approach, we can first apply Toom-Cook 3-way on software, and then reuse any  $256 \times 256$  polynomial multiplier available in the literature to perform the 5 multiplications on hardware. This allows a more fine grain tuning of the implementation since we can trade-off area for speed depending on the needs of our application. Fig. 2 summarizes the data flow and the partition between software and hardware. Instantiating 5  $256 \times 256$  multipliers in parallel yields to a 5 times larger area while achieving the same performance for a  $768 \times 768$ multiplication as for a single  $256 \times 256$  multiplication. Alternatively, we can utilize as little area as for a single  $256\times256$  multiplication to perform the full  $768\times768$  multiplication in 5 times more clock cycles. Since we want to show that the improved efficiency is due to our design of Florete rather than to a carefully optimized implementation, we choose to instantiate only one  $256 \times 256$  polynomial multiplier.

Figure 2: Proposed HW/SW partition for a Florete accelerator

Regarding the choice for the  $256 \times 256$  polynomial multiplier, we consider the three options available in the literature. The first [DFAG19] implements a schoolbook multiplier

that instantiates 256 multiply-and-accumulate (MAC) units in parallel to perform the innermost loop in a single clock cycle, thus iterating only over the outermost loop. The MAC units are implemented using the DSP primitives available in the FPGA. The problem of this approach is that such a large number of DSP units is only available in the most high end FPGAs, like the UltraScale+ family of Xilinx where it has been implemented. In more standard devices the available number of DSPs imposes a limitation for implementing this approach. The second option  $[MTK^+20]$  implements a  $256 \times 256$  multiplier that uses Toom-Cook 4-way to break down one multiplication into 7  $64 \times 64$  polynomial multiplications that are performed in parallel by compact units. While the performance is worse than the previous method, the design is very compact and it can be applied directly on any FPGA requiring only 28 DSP units, and for any coefficient size for both operands. The third option [RB20] implements a shift register based approach as in the first option, but eliminates the need of DSP units by taking advantage of the fact that the coefficients of one operand, the secret vector, are small. Instead, custom MAC units based on a coefficient-wise shift-and-add are implemented. In addition to this, the latency is halved by embedding the negacyclic convolution in the multiplication. We cannot take advantage of this because the result should be unwrapped for the interpolation of Toom-Cook 3-way. Furthermore, we cannot take advantage of the same shift-and-add MAC units because prior to the  $256 \times 256$  multiplication the operands grow due to the Toom-Cook 3-way evaluation. Therefore, we implement a design based on  $[MTK^+20]$ . Results are discussed in Sec. 5.4 and compared to other implementations in our suite and in the state-of-the-art.

#### 5.2 Espada on hardware

Module lattices are in general friendly towards parallelization due to the matrix-vector multiplication. Furthermore, when we use an algorithm to break a large polynomial multiplication into several smaller polynomial multiplications, e.g., using Toom-Cook, we are generating new parallelisms. However, the latter comes with a computational overhead due to the evaluation and interpolation steps of such algorithm. The parameter choices for Espada seek to exploit the inherent parallelism of matrix-vector multiplication even further while avoiding the extra cost of breaking down large polynomial multiplications. This translates into compactness by design in single instruction single data (SISD) processors as shown in Sec. 4.2. The drawback of Espada with respect to other lattice-based KEMs is the increased number of polynomial multiplications and randomness requirements. The challenge in hardware is to exploit the parallelism effectively to bring Espada performance close to the state-of-the-art.

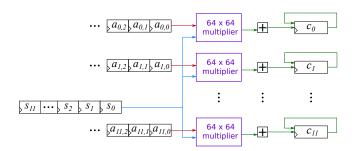

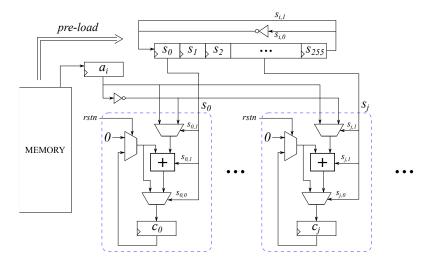

Fig. 3 shows our proposed architecture to exploit the parallelism of Espada's matrixvector multiplication. For a public matrix of dimension  $l \times l$ , l polynomial multipliers are instantiated in parallel. Each of the parallel multipliers is fed with a row of the public matrix. The second operand. which is the corresponding polynomial of the secret on each iteration, is the same for all multipliers. Each multiplier reads and writes data to a small local memory implemented as LUT-based RAM to avoid the large penalization of accessing in parallel the system memory. This distributed memory is also filled at the same time as the polynomials are being transferred to the memory to minimize the loading penalization. The second operand can be sent simultaneously to all multipliers, so it does not incur an additional overhead. The result accumulated on the *i*-th multiplier corresponds to the *i*-th row-vector product. Note that this architecture exploits the parallelism at matrix-vector level while still leaves room for a certain trade-off between area and performance with the design of the  $64 \times 64$  polynomial multipliers.

The proposed parameters for achieving a NIST security level 3 with Espada is set as l = 12. While allowing a high degree of parallelization, this also imposes an important constraint on the design of the  $64 \times 64$  polynomial multipliers. Figure 4 shows a parameterizable architecture for such multiplier. The number of arithmetic units, implemented with

Figure 3: Parallel architecture for matrix-vector multiplication in Espada

native DSP primitives for efficiency, can be increased or decreased for achieving a higher performance or a lower area utilization. In our implementation, this circuit will be instantiated 12 times in parallel. To guarantee that the FPGA resources will not be exhausted, we choose 4 DSP units per polynomial multiplier, which add up to 48 overall. In Sec. 5.4 we include performance and area results and discuss them in detail.

Figure 4: Architecture of the compact  $64 \times 64$  polynomial multiplier used for Espada

#### 5.3 Sable on hardware

In contrast with Florete and Espada that are not similar to existing schemes, the design of Sable is close to Saber. As explained in Sec. 3.4, our contribution here is on the selection of more efficient parameters for Saber by applying the latest results of research on lattices. From an implementation point of view, all the existing research on Saber implementations can be applied directly to Sable. In particular, the implementations in [DFAG19] and [MTK<sup>+</sup>20] should be readily available to support Sable parameters owing to the higher flexibility offered by HW/SW co-designed accelerators. The processor in [RB20] implements an instruction set architecture (ISA) with a unified sampling module to give support to LightSaber, Saber and FireSaber parameters. These three parameter sets sample the secrets from a centered binomial distribution with different  $\eta$  values, being  $\eta = 5, 4, 3$ , respectively. This module being extended to support also  $\eta = 1$ , such processor shall also serve for accelerating Sable. Moreover, any arithmetic module of a Saber processor can be directly reused for Sable after sign-extending the most significant bit of every secret coefficient.

Although existing Saber co-processors can be reused for Sable, the secrets of our scheme are smaller. The architectures in [DFAG19] and [MTK<sup>+</sup>20] are more generic, but the one proposed in [RB20] exploits the small secrets to achieve high performance without exhausting the FPGA resources. We optimize their architecture for our parameters, which

allows us to substantially reduce the area requirements without a performance loss. Figure 5 draws our proposed architecture. The dashed box highlights the arithmetic unit, which is instantiated 256 times for a full parallel multiplication. For the arithmetic unit we use a custom architecture which is very efficient for 2 bits secrets. If the least significant bit of the secret coefficient is zero, the value in the accumulator register does not change, and it is irrelevant if the other secret bit is 0 or 1. If the least significant bit of the secret is one, the current coefficient of a will be either add or subtract from the result depending on the most significant bit of the secret. The multiplier implements 256 arithmetic units for a fully parallelized multiplication. Our parameters allow us to pack more secret coefficients in less memory, therefore we can reduce the overhead for loading the secret register. The negacyclic convolution is performed in-place and the result is stored in the accumulator registers. These registers can be reset to perform a polynomial multiplication, or preserved to perform the row-column multiplication in the matrix-vector multiplication saving up the time spent on the additions. The performance and area figures of our design are discussed in Sec. 5.4 as for the implementations of Florete and Espada.

Figure 5: Parallel architecture of Sable polynomial multiplier

#### 5.4 Results

We have implemented all our hardware designs using the Vivado Design Suite 2018.1 and targeting the Xilinx ZedBoard Zynq-7000 AP SoC XC7Z020-CLG484 and runnning the synthesis and implementation with the default strategies. We use the ARM Cortex-A9 CPU running at 666 MHz available in the same chip to send the data and commands to the hardware accelerator, which in turn runs at 125 MHz for Florete and Espada, and at 150 MHz for Sable. Table 5 shows a comparison for each scheme in Scabbard when implemented only on SW or accelerated by the multiplier available in hardware. For Espada we use the multiplier described in Sec. 5.2, while for Sable we show the speed-ups that can be obtained by the compact multiplier described in Sec. 5.1 and by the high speed multiplier described in Sec. 5.3. We include Saber because the implementation in [MTK<sup>+</sup>20] also follows a HW/SW co-design approach which allows a fair comparison. We include the total area requirements of these three HW/SW co-processors in Appendix F. In the following, we restrict our discussion to the multiplier architectures, which is the only block implemented on hardware, and allows us a fair comparison to the state of the art.

In Table 6 we show the area requirements of the polynomial multiplier and compare it with the compact multiplier for Saber in  $[MTK^+20]$  and the high performance multiplier

| Scheme name                 |        | ance on Ze<br>V only) - [ |        | 1 01101111 | ance on Zo<br>V/SW) - [ | Zedboard Speed up<br>- $[\mu s]$ |        |        |        |  |

|-----------------------------|--------|---------------------------|--------|------------|-------------------------|----------------------------------|--------|--------|--------|--|

|                             | KeyGen | Encaps                    | Decaps | KeyGen     | Encaps                  | Decaps                           | KeyGen | Encaps | Decaps |  |

| Espada                      | 51373  | 55706                     | 58527  | 9618       | 10460                   | 9820                             | 5.3    | 5.3    | 6.0    |  |

| $Sable^*$                   | 47032  | 62611                     | 77095  | 2406       | 3114                    | 2765                             | 19.5   | 20.1   | 27.9   |  |

| $Sable^{\dagger}$           | 47032  | 02011                     | 11095  | 2958       | 3714                    | 3419                             | 15.9   | 16.9   | 22.5   |  |

| Saber [MTK <sup>+</sup> 20] | 17659  | 22438                     | 27001  | 3273       | 4147                    | 3844                             | 5.4    | 5.4    | 7.0    |  |

Table 5: Performance comparison between schoolbook implementations on software and the speed-up achieved by the polynomial multiplier on hardware.

$^*$  using the high speed 256  $\times$  256 multiplier  $^{-\dagger}$  using the compact 256  $\times$  256 multiplier

for Saber in [RB20]. In particular, we compare the compact designs for Florete and Espada in rows 1 and 2 with the compact Saber processor from  $[MTK^+20]$  in row 4, and the high speed multiplier for Sable in row 3 to the fast Saber multiplier from [RB20] in row 5. We choose to compare our designs with Saber because it is the most well-known LWR-based scheme and all our schemes are also based on variants of the LWR problem. Also, note that we compare the performance of a full matrix-vector multiplication rather than a single polynomial multiplication because otherwise Florete may seem the least efficient solution when it is actually the opposite, and Espada may seem an order of magnitude faster due to the small polynomials and large matrix dimension.

|   | Scheme                      | Platform    | f   | LUTs      | FFs   | DSPs | $t_{mvmul}$   |

|---|-----------------------------|-------------|-----|-----------|-------|------|---------------|

| 1 | Florete [Ours]              | Zedboard    | 125 | 2,878     | 1,263 | 38   | $88 \ \mu s$  |

| 2 | Espada [Ours]               | Zedboard    | 125 | $4,\!150$ | 2,537 | 48   | $111 \ \mu s$ |

| 3 | Sable [Ours]                | Zedboard    | 150 | 6,084     | 3,354 | 0    | $17 \ \mu s$  |

| 4 | Saber [MTK <sup>+</sup> 20] | Zedboard    | 125 | 2,927     | 1,279 | 38   | $158 \ \mu s$ |

| 5 | Saber [RB20]                | Ultrascale+ | 250 | 17,429    | 5,083 | 0    | $11 \ \mu s$  |

Table 6: Area and performance results of the polynomial arithmetic on hardware for our schemes and state-of-the-art Saber